1

Изобретение относится к передаче данных, преимущественно для передачи информации с решающей обратной связью.

Известно устройство для исправления и обнаружения ошибок, в котором исправление ошибок осуществляется на основании анализа, вычисляемого синдрома и опознавания позиций искаженных символов l.

При этом для исправления t-кратных ошибок необходимо применять избыточный код с кодовым расстоянием d 21 + 1. Это устройство сложно в исполнении и его сложность возрастает с увеличением числа элементов комбинации и с увеличением кодового расстояния.

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для исправления ошибок в кодовой комбинации, которое обеспечивает исправление t-кратных ошибок при использовании корректирующего кода с кодовым расстоянием d t + 1 р .

Однако наличие в таком устройстве двух блоков обнаружения ошибок, трёх регистров -памяти и четырех ячеек обуславливает его сложность.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что в устройстгво для исправления ошибок в кодовой комбинации, содержащее регистр сдвига, первый элемент-И, ячейку памяти, регистр ошибок, первый счетчик ошибок, регистр памяти, сумматор по модулю два, триггер, вто0рой элемент И, блок обнаружения ошибки, причем информационный вход устройства соединен с первым входом первого элемента И, второй вход которого соединен с первым тактовый входом

5 устройства, выход первого элемента И соединен с управляющим входом регистра сдвига, второй тактовый вход устройства соединен с установочным входом регистра сдвига и со сбросовьпл

0 входом ячейки памяти, выход которой соединен с информационным входом регистра ошибок и счетным входом первого счетчика, выход регистра ошибок соединен с первым входом второго

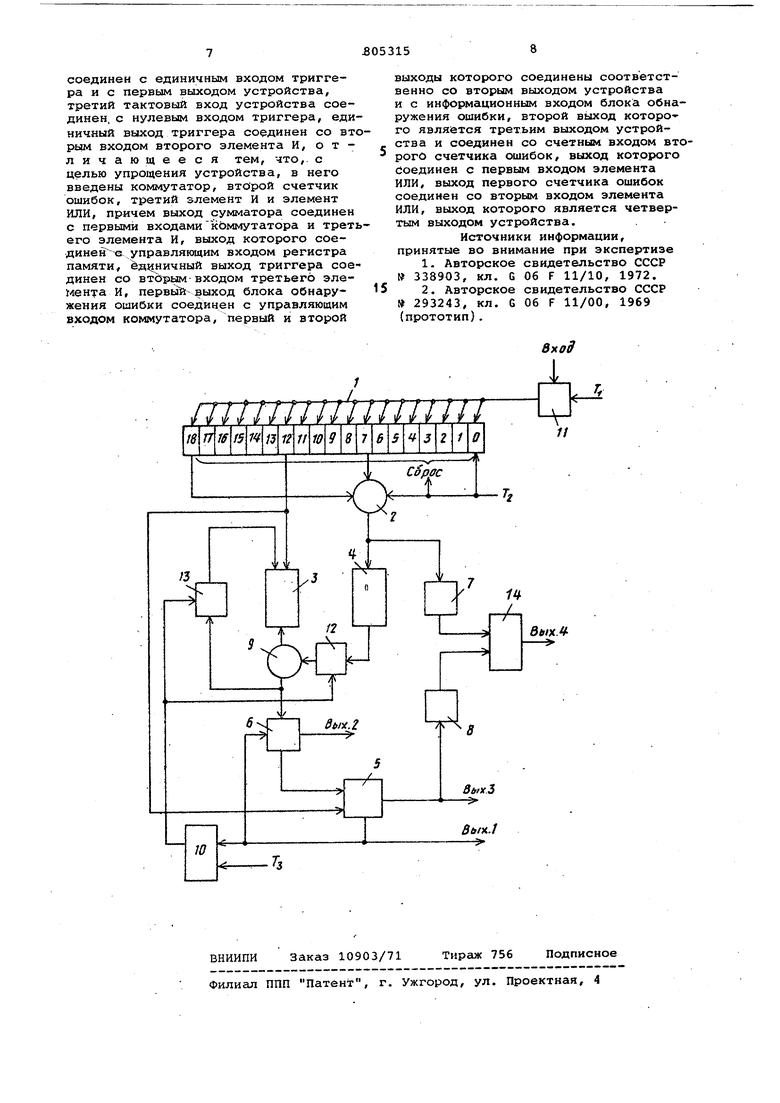

5 элемента И, выход которого соединен с первым входом сумматора по модулю два, единичный выход 1-го разряда регистра сдвига соединен со входом записи ячейки памяти, выход переполнения регистра сдвига соединен со входом стирания ячейки памяти, единичный выход j-го разряда регистра сдвига соединен с управляющим входом блока обнаружения обшибки и с информационным входом регистра памяти, вы ход которого соединен со вторым входом сумматора по модулю два, первый выход блока обнаружения ошибки соединен с единичным входом триггера и с nepBtJM выходом устройства, третий тактовый вход устройства соединен с нулевым входом триггера, едини ный выход триггера соединен со вторым входом второго элемента И, введе ны коммутатор, второй счетчик ошибки третий элемент И и элемент ИЛИ, причем выход сумматора соединен с первыми входами коммутатора и третьего элемента И, выход которого соединен с управляющим входом регистра памяти единичный выход триггера соединен со вторым входом третьего элемента И, первый выход блока обнаружения ошибки соединен с управляющим входом ком мутатора, первый и второй выходы которого соединены соответственно со вторым выходом устройства и с информационным входом блока обнаружения ошибки, второй выход которого являет ся третьим выходом устройства и соед нен со счетным входом второго счетчика ошибок, выход которого соединен с первым входом элемента ИЛИ, выход первого счетчика ошибок соединен со вторым входом элемента ИЛИ, выход ко торого является четвертым выходом устройства. На чертеже приведена функциональная схема устройства. Устройство содержит регистр 1 сдв га, ячейку 2 памяти, регистр 3 памяти, регистр 4 ошибок, блок 5 обнаружения ошибки, коммутатор б, счетчики 7 и 8 ошибок, сумматор 9 по модулю два, триггер 10, элементы И 11-13 элемент ИЛИ 14.. В этом устройстве ин формационный вход соединен с первым входом элемента И 11, второй вход которого соединен с первым тактовым входом Т устройства, а выход; - с уп равляющим входом регистра 1 сдвига. Второй тактовый вход устройства T-j соединен с установочным входом регистра 1 сдвига и со сбросовым входо ячейки 2 памяти, выход которой соединен с информационным входом регист ра 4 ошибок и счетным входом счетчика 7 ошибок. Выход регистра 4 ошибок соединен с первым входом элемента И 12, выход которого соединен с первым входом сумматора 9 по модулю два а второй вход элемента И 12 соединен с единичным вьоходом триггера 10. Еди ничный выход i-го разряда регистра 1 сдвига соединен со входом записи ячейки 2 памяти, выход переполнения соединен со входом стирания ячейки 2 памяти, а единичный выход j-ro разряда - с управляющим входом блока 5 обнаружения ошибки и с информационным входом регистра 3 памяти, выход которого соединен со вторым входом сумматора 9 по модулю два. Первый выход блока 5 обнаружения ошибки соединен с единичным входом триггера 10, с управляющим входом коммутатора 6 и с первым выходом устройства. Третий тактовый вход Т устройства соединен с нулевым входом триггера 10, единичный выход которого соединен со вторыми входами элементов И 12 и 13. Выход сумматора 9 по модулю два соединен с первым входом коммутатора 6 и первым входом элемента И 1.3, выход которого соединен с управляющим входом регистра 3 памяти. Первый и второй выходы коммутатора б соединены соответственно со вторым выходом устройства и с информационным входом блока 5 обнаружения ошибки, второй выход которого является третьим выходом устройства и соединен со счетным входом счетчика 8 ошибок, выход которого соединен с первым входом элемента ИЛИ 14. Выход счетчика 7 ошибок соединен со вторым входом элемента ИЛИ 14, выход которого является четвертым выходом устройства. Устройство для исправления ошибок в кодовой комбинации для случая, когда принимаемые элементарные импульсы стробируются в ё точках (€ 25), при зоне неопределенности b I1, что составляет 44%, работает следующим образом. В нулевой разряд регистра 1 сдвига записана 1. Импульсом на вход Tj устройства триггер 10 установлен в единичное положение. На вход элемента И 11 поступают информационные импульсы, а на вход Т - стробирукчцие. Количество стробирующих импульсов, поступающих на вход регистра 1 сдвига зависит от искажения одного элемента кодовой комбинации. При поступлении положительного элемента кодовой комбинации 1, записанная в нулевом разряде регистра 1 сдвига, продвигается влево. Если на вход регистра 1 сдвига поступит 8 и более стробирующих импульсов, то 1 будет продвинута в 8-1 разряд и далее. При этом импульсом .из 7-го разряда, т.е. с первого выхода регистра 1 сдвига, в ячейку 2 памяти запишется 1. Если поступит 13 и более импульсов, то 1 будет продвинута в 13-й разряд и далее. При этом на выходе 12-го разряда, т.е. на втором выходе регистра 1 сдвига, появится импульс, который в регистр 3 памяти и в блок 5 обнаружения ошибки запишет 1. Если число стробнрукяцих импульсов будет не меньше 19-ти, то импульсом с 18-го разряда, т.е. .с выхода переполнения регистра 1 сдвига в ячейке 2 будет стерта 1..Это соответствует приему неискаженного кодового элемента 1.

По окончании приема элемента кодовой комбинации тактовым импульсом на вход Т-2. производится сброс всех разрядов регистра 1 сдвига в О, а в нулевой разряд записывается 1. После этого начинается прием следующего элемента кодовой комбинации. Если число стробирующих импульсов будет меньше 19-ти, то по окончании приема элемента кодовой комбинации 1 из ячейки 2 памяти будет переведена тактовым импульсом в счетчик 7 ошибок и в регистр 4 ошибок. Это соответствует приему кодового элемента 1 с искажением (ненадежный элемент).

Если при приеме 1 элемента кодовой комбинации число стробирующих импульсов на входе регистра 1 сдвига будет не больше 12-ти, то в регистр памяти и в блок 5 обнаружения ошибки запишется О, что соответствует приему кодового элемента с ошибкой. При этом, если число стробирующих импульсов будет больше 7-и, то в ячейку 2 памяти и далее в счетчик 7 ошибок и регистр 4 ошибок запишется 1, что соответствует приему кодового элемента О с искажением (ненадежный элемент) . Аналогичный принцип работы и при приеме кодового элемента О.

Таким образом, после приема всех элементов кодовой комбинации в регистре 3 памяти будет находиться принятая кодовая комбинация, а в регистре 4 ошибок будут записаны 1 в тех разрядах, где элементы кодовой комбинации были сомвительннлми (либо О, либо 1).

Поступившая в блок 5 обнаружения ошибки кодовая комбинация проверяетс на наличие ошибок. Если ошибка не.обнаружена,, то сигнал Верно поступае с первого выхода блока 5 обнаружения ошибки на управляющий вход коммутатора 6, где переключает его на второй выход устройства для вывода информации к получателю. Одновременно сигнал Верно переключает триггер 1 в нулевое положение, что запрещает перезапись информации через элемент И 13 в регистре 3 памяти и запрещает прохождение информации из регистра 4 ошибок через элемент И 12 на сумматор 9 по модулю два. Этот же сигнал Верно поступает на первый выход устройства для вывода информации из регистра 3 памяти и из регистра 4 ошибок.

Если При проверке кодовой комбинации обнаружена ошибка, то блок 5 обнаружения ошибки формирует сигнал HP iepHo, который поступает на счетHrfV 8 ошибок и одновременно на третий выход устройства для переключения триггера 10 в единичное положение и для вывода информации из регистра 3 памяти и регистра 4 ошибок на сумматор 9 по модулю два, где происходит поразрядное сложение по модулю два, т.е. исправление тех раз-рядов кодовой комбинации, в которых зафиксированрл ненадежные элементы. Исправленная кодовая комбинация через элемент И 13 перезаписывается в регистр 3 памяти, а через коммутатор 5 6 вновь поступает в блок 5 обнаружения ошибки для проверки. Если в исправленной кодовой комбинации ошибка не обнаружена, то кодовая комбинация из регистра 3 памяти выводится

0

получателю описанным выше путем. При

наличии ошибки очередной импульс Неверно поступит на счетчик 8 ошибок и со счетчика 8 ошибок через элемент ИЛИ 14 на четвертый выход устройства для стирания информации в регистре 3 памяти и запроса повторной информации.

Кроме того, при поступлении на вход счетчика 7 числа импульсов, равQ ного кодовому расстоянию избыточного

кода, он выдает сигнал через элемент ИЛИ 14 на четвертый выход устройства для стирания принятой информации и запроса повторной -информации.

5 Таким образом, устройство обеспечивает исправление и обнаружение ошибок в кодовой комбинации значительно проще изв.естных аналогичных устройств.

30

Формула изобретения

Устройство для исправления ошибок в кодовой комбинации, содержащее регистр сдвига, первый элемент И, ячейку памяти, регистр ошибок, первый счетчик ошибок, регистр памяти, сумматор по модулю два, триггер, второй элемент И, блок обнаружения ошибки, причем информацион;1ый вход устройства соединен с первым входом первого . элемента И-, . второй вход которого соединен с первым тактовым входом устройства, выход первого элемента И . соединен с управляющим входом регистpa сдвига, второй тактовый вход устройства соединен с установочным входом регистра сдвига и со сбросовым входом ячейки памяти, выход которой соединен с информационным входом регистра ошибок и счетным входом первого счетчика, выход регистра ошибок соединен с первым входом второго элемента И, выход которого соединен с первым входом сумматора по модулю два, единичный выход i-ro разряда регистра сдвига соединен со входом записи ячейки памяти, выход переполнения регистра сдвига соединен со входом стирания ячейки памяти, единичный вход j-ro разряда регистра

сдвига соединен с управляющим входом блока обнаружения ошибки и с информационньом входом регистра памяти, выход которого соединен со вторым входом сумматора по модулю два, первый выход блока обнаружения ошибки

соединен с единичным входом триггера и с первым выходом устройства, третий тактовый вход устройства соединен, с нулевым входом триггера, единичный выход триггера соединен со вторь м входом второго элемента И, о т личающееся тем, что, с целью упрощения устройства, в него введены коммутатор, второй счетчик ошибок, третий элемент И и элемент ИЛИ, причем выход сумматора соединен с первыми входами коммутатора и третьего элемента И, выход которого соедине Г управляющим входом регистра памяти, единичный выход триггера соединен со вторым входом третьего элемента И, nepBt -выход блока обнаруженин ошибки соединен с управляющим входом коммутатора, первый и второй

выходы которого соединены соответственно со вторым выходом устройства и с информационным входом блока обнаружения ошибки, второй выход которо го является третьим выходом устройства и соединен со счетным входам втрого счетчика ошибок, выход которого Соединен с первым входом элемента ИЛИ, выход первого счетчика ошибок соединен со вторым входом элемента ИЛИ, выход которого является четвертым выходом устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 338903, кл, G Об F 11/10, 1972.

2.Авторское свидетельство СССР 293243, кл. G Об F 11/00, 1969 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙКОМБИНАЦИИ | 1971 |

|

SU293243A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В КОДОВОЙ КОМБИНАЦИИ | 1972 |

|

SU335689A1 |

| Устройство для исправления двойных и обнаружения многократных ошибок циклическими кодами | 1983 |

|

SU1185611A1 |

| Устройство для исправления пакетных ошибок модульными кодами | 1988 |

|

SU1596465A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Система для передачи и приема дискретной информации | 1979 |

|

SU903850A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| Устройство для исправления модульных ошибок | 1988 |

|

SU1522414A1 |

| Декодирующее устройство | 1986 |

|

SU1381720A1 |

| Декодирующее устройство | 1988 |

|

SU1522415A1 |

Авторы

Даты

1981-02-15—Публикация

1978-04-03—Подача