Изобретение относится к области вычислительной техники и может быть иснользовано в системах обработки цифровой информации.

Известны устройства для корректировки двоичных арифметических кодов вида AN, в которых вычисление остатка по модулю А производится путем последовательной поразрядной обработки корректируемой информации на регистре сдвига с обратной связью. В указанных устройствах для проведения коррекции требуется много времени и большой объем необходимого оборудования.

Цель изобретения - сокращение времени коррекции и уменьшение объема необходимого оборудования. Это достигается за счет того, что устройство для корректировки двоичных арифметических кодов производит одновременную обработку нескольких разрядов корректируемого кода как при вычислении остатка, так и при осуществлении исправления, причем вычисление остатка и исправление выполняется одними и теми же схемами.

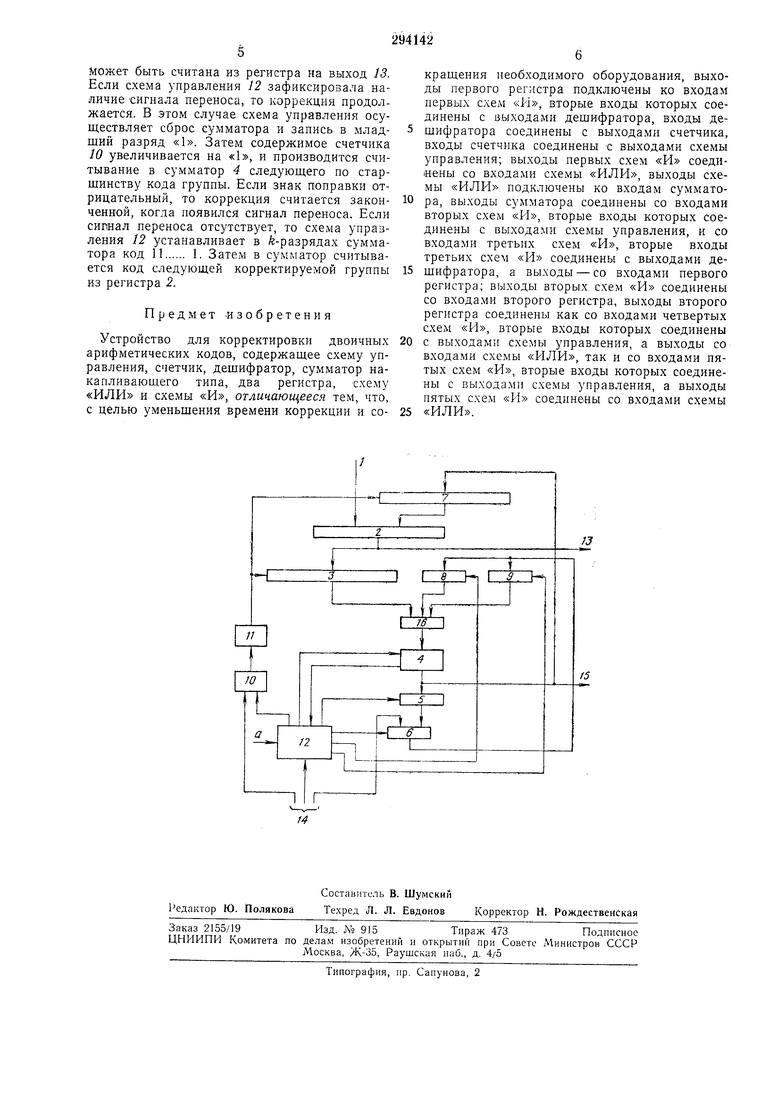

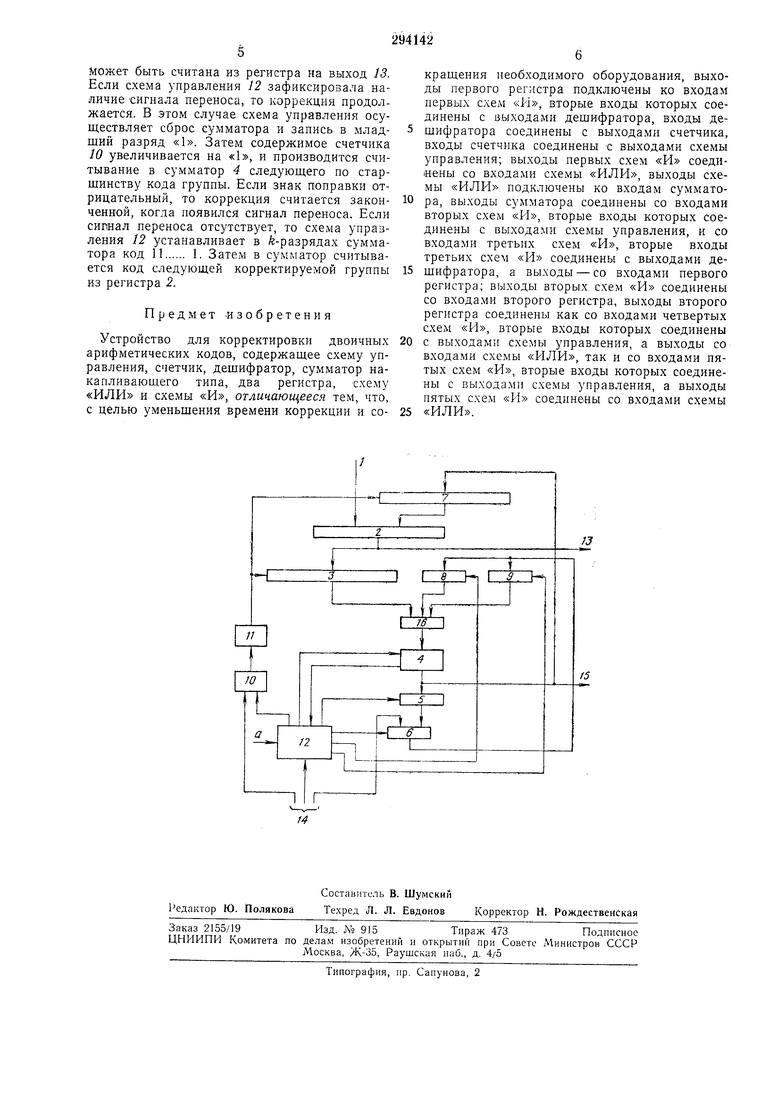

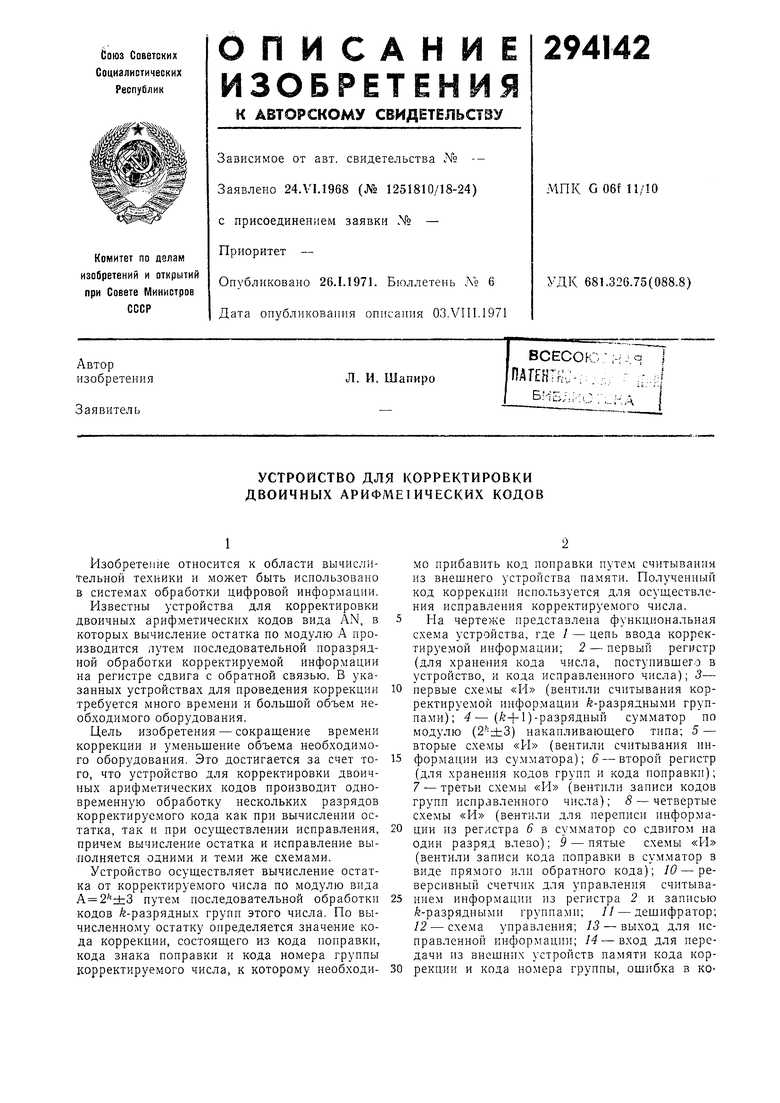

Устройство осуществляет вычисление остатка от корректируемого числа но модулю вида А 2±:3 путем последовательной обработки кодов fe-разрядных групп этого числа. По вычисленному остатку определяется значение кода коррекции, состоящего из кода поправки, кода знака поправки и кода номера группы корректируемого числа, к которому необходи.МО прибавить код поправки путем считывания из внешнего устройства памяти. Полученный код коррекции используется для осуществления исправления корректируемого числа. Па чертеже представлена функциональная схема устройства, где - цепь ввода корректируемой информации; 2 - первый регистр (для хранения кода числа, поступившего в устройство, и кода исправленного числа); 3-

первые схемы «П (вентили считывания корректируемой информации -разрядными группами); 4- (+1)-разрядный сумматор по модулю (2-±3) накапливающего типа; 5 - вторые схемы «И (вентили считывания пнформации из сумматора); 6 - второй регистр (для хранения кодов групп и кода поправки); 7 - третьи схемы «И (вентили записи кодов групп исправленного числа); 8-четвертые схемы «И (вентилн для переписи информации пз регистра 6 в сумматор со сдвигом на один разряд влево); 9 - пятые схемы «PI (вентили записи кода поправки в сумматор в виде прямого или обратного кода); W-реверсивный счетчик для управления считыванием информации из регистра 2 и записью -разрядными группами; 1 - дешифратор; 12 - схема управления; 13 - выход для исправленной информации; 14 - вход для иередачи из внешних устройств памяти кода кортором привела к искажению всего числа, и сигналов запуска корректора; 15- выход для кода остатка от искаженного числа но модулю (2±3); /( -схема «ИЛИ.

Устройство работает следующим образом.

Искаженная информация, поступающая на вход устройства, фиксируется в регистре 2. Внешним сигналом а производится запуск устройства для определения остатка от числа записанного в регистре 2 по модулю (24-3) или (2-3), в зависимости от того, для работы с каким модулем предусмотрено устройство. Схема управления 12 осуществляет сброс регистров 6 и сумматора и включение реверсивного счетчика 10 в режим вычитания. После этого схема управления начинает формировать тактовые сигналы в счетчик и на вентили 5, 8, 9.

Счетчик W с дешифратором 11 осуществляют унравление вентилями 3, через которые информация из регистра 2 в виде кодов групн разрядов поступает в собирательную схему 16, а через ее выходы в сумматор 4. Передача групп осуществляется последовательно, начиная со старших разрядов. В общем случае число разрядов принимаемого в корректор числа можно представить в следующем виде:

,

где

г - число разрядов в старшей группе (число групн равно ). Любое двоичное число Л можно представить в виде полинома:

N

bj2}.

Тогда общую формулу, в соответствии с которой корректор осуществляет нахождение остатка от корректируемого числа но модулю вида (), МОЖ1НО записать

tk+r-l

К 1±(з- 6.2/-)mod()+ ... + L ч „0/

(i+i}k-i+ 2 &, 3mod()-f ...+ J

ft-i

+ 3mod(2 ± 3) + 2 6.2П niod(2 ± 3).

В сумматоре осуществляется сложение но модулю ) или (2-3).

Тактовым сигналом, открывающим вентили 5, информация из сумматора переписывается в регистр 6. В следующем такте производится выдача кода из регистра 6 через вентили 8 и собирательную схему 16 в сумматор со сдвигом на один разряд влево.

Сложением числа, содержащегося в сумматоре с кодом числа, поступившего через вентили 8, завершается каждый промежуточный цикл работы корректирующего устройства. Следующий цикл начинается с выдачи из схемы управления 12 в счетчик тактового импульса. Выполнение всей операции вычисления остатка по модулю () состоит из (+1)-го онисанного выше частичного цикла. При вычислении остатка но модулю (2+3) последНИИ цикл отличается от предыдущих, так как в соответствии с формулой в последнем цикле необходимо вычесть код остатка по модулю (2-f-3), полученный в предпоследнем цикле, из кода младшей группы.

Для того чтобы заменить операцию вычитания на операцию сложения, содержащаяся в сумматоре информация в последнем цикле переписывается через вентили 5 в регистр 6. Следующим тактовым импульсом схемы унравления 12 производится сброс сумматора и запись в 1-й разряд «1. После этого производится перепись содержимого регистра 6 через вентили 9 в виде обратного кода в сумматор 4. В следующем такте из регистра 2 через вентили 3 в сумматор 4 считывается код младшей группы корректируемого числа.

После окончания последнего цикла схема управления 12 выдает во внещнее устройство памяти сигнал запроса, а из сумматора 4 на

выход 15 ноступает код остатка, по которому производится считывание из внещнего устройства памяти на вход 14 кода коррекции, соответствующего вычисленному остатку. Код коррекции состоит из й-разрядного кода поправки, одноразрядного кода знака поправки и кода номера группы, к которому необходимо нрибавить код ноправки с учетом знака. Код поправки записывается в регистре 6, знак поправки фиксируется в схеме управления 12,

а код номера группы поступает в счетчик 10. Затем схема управления 12 осуществляет переключение счетчика на режим прибавления «1, закрывает вентили обратной связи сумматора 4, управляющие сложением по модулю

2±3, и формирует ряд тактовых импульсов для коррекции числа, содержащегося в регистре 3. Первым тактовым импульсом производится сброс сумматора, и запись в 1-й разряд «1, если знак поправки отрицательный. Затем открывается ряд вентилей 3, соответствующих коду номеру грунны, содержащемуся в счетчике.

Код группы разрядов считывается из регистра 2 через вентили 3 в сумматор 4. Следующим тактовым импульсом информация, содержащаяся в регистре 6, считывается в сумматор через вентили 9 в прямом или обратио.м коде (в зависимости от знака поправки). Если знак нонравки отрицательный, то открыБаются вентили считывания обратного кода.

Схема управления 12 фиксирует появление сигнала переноса из k-ro разряда сумматора 4. Р1справленный код группы считывается из

сумматора 4 через вентили 7 в соответствующие разряды регистра 2. Если знак поправки положительный и сигнал переноса отсутствовал, то коррекция считается законченной. В этом случае информация, образовавшаяся в

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОРРЕКТИРОВКИ ДВОИЧНЫХ АРИФМЕТИЧЕСКИХ КОДОВ | 1972 |

|

SU328464A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для исправления ошибокВ СиСТЕМЕ ОСТАТОчНыХ КлАССОВ | 1979 |

|

SU842820A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Устройство для вычисления функций синуса и косинуса | 1977 |

|

SU723583A1 |

| Устройство для вычисления тригонометрических функций | 1984 |

|

SU1166103A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2007 |

|

RU2326494C1 |

Даты

1971-01-01—Публикация