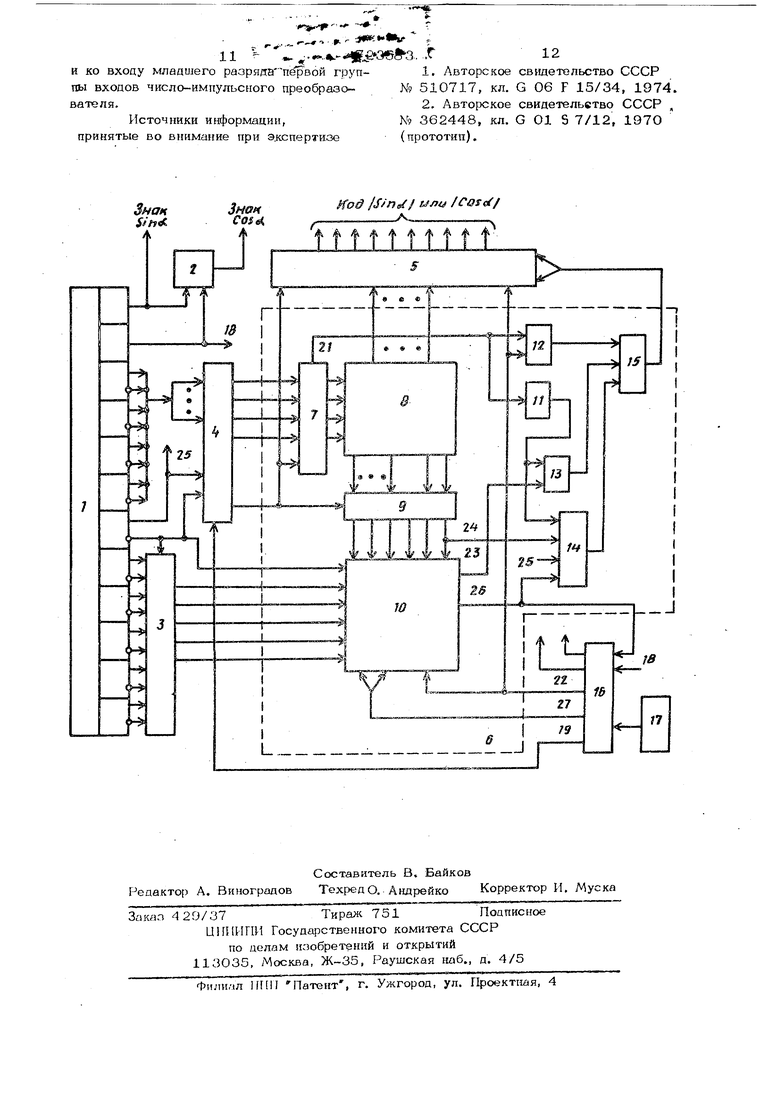

Изобретение относится к области вычислительной техники и моЖет быть использовано в устройствах преофазования параллельного кода угла в коды синуса и косинуса. Известно устройство для вычисления функции синуса и косинуса на основе таблиц, хранящихся в блоке постоянной памяти (ПЗУ) 1 . Однако использование ГОУ, обеспечивая виибольшее быстродействие, требует большого объема памяти для получения высокой точности вычислений. Наиболее близким по технической сущ ности к предложенному является устройство для вычисления функций синуса и ко синуса, содержащее п -разрядный входной регистр, сумматор подмодулю два, первы и второй коммутаторы, реверсивный счетчик, блок памяти, число-импульсный преобразоваггель, блок управления, генератор тактовых импульсов, причем прямые и ин версные выходы младших разрядов входного регистра (с первого по п -ый) через первый коммутатор подключены к соответствующим входам первой группы число-импульсного преобразователя, инверсные выходы разрядов входного регистра {с (т+1)-го по (п-2)-ой1.подключены к соответствующим входам второго коммутатора. Выходы (n-l)-ro и п -го разрядов входного регистра подключены ко входам сумматора по модулю два. Выход сумматора по модулю два и выход П -го разряда входного регистра являются соответственно выходом знака косинуса и выходом знака синуса устройства. Первая группа выходов блока памяти подключена к установочным входам реверсивного счетчика, выходы разрядов которого являются информационными выходами устройства. Выход генератора так.товых импульсов подключен к тактовому, а выход (м-1)-го разряда входного регистра и выход переполнения число-импульсного преобразователя - к соответствующим управляющим входам блока управления, выходы которого подключены соответственно к управляющему входу второго коммутатора, тактовому и установочному входам число-импульсного преобразователя и входу управления записью реверсивного счетчика. Один из выходов блока управления является выходом сигцала окончания формирования функции синуса, а другой - выходом сигнала окончания формирования функции косинуса устройства 2 . Однако это устройство имеет низкую точность вычислений и малое быстродействие. Цепь изобретения - повышение точности и быстродействия устройства для вычисления функции синуса и косинуса. Это достигае1Ся тем, что устройство для вычисления функции синуса и косинуса содержит сумматор адреса, сумматор коррекиии, элемент НЕ, три элемента И, Элемент ИЛИ, причем выход младшего разряда второго коммутатора подключен ко входу первого, а остальные выходы второго коммутатора - ко входам второго слагаемого сумматора адреса, выходы разрядов суммы .которого подключены к адресным входам блока памяти, а выход переполнения - к nepBoi%iy входу перво го и через элемент НЕ к первому входу второго и первому входу третьего элементов И. Выходы первого, второго и третьего элементов И через элемент ИЛ подключены к счетному входу реверсивно го счетчика. Входы первого и второго слагаемото сумматора коррекции -подключены соотве1х;твенно ко второй и третьей группам выходов блока памяти, управляющий вход сумматора коррекции - к выходу i/шадшего разряда второго коммутатора п управляющему входу реверсивного счетчика, выходы сумматора кoppe щиико второй, группе входов чиспо-импульсного преобразователя. Второй вход перво го апемента И подключен ко входу управ ления записью реверсивного счетчика, вт рой вход второго элемента И - к числоимпульсному выходу число- импульсного преобразователя. Второй вход третьего элемента И подключен к выходу старшег разряда сумматора коррекции, третий и четвертый входы третьего элемента И соответственно к прямому выходу ()го разряда входного регистра и выходу переполнения число-импульсного преобразователя. Инверсный выход (W+1 го разряда входного регистра подключен к ущзавляющему входу первого коммутатора н ко входу кшадшего разряда перво 7 34 группы входов число-импульсного преобразователя. Функциональная, схема устройства для случая m 5,1л 12 представлена на чертелсе. Устройство содержит входной регистр 1, сумматор по модулю два 2, первый 3 и второй 4 коммутаторы, реверсивный счетчик 5, генератор 6 синусоидального аппроксимирующего кода, состоящий из сумматора адреса 7, блока памяти 8 в виде постоянного запоминающего устройства (ПЗУ), сумматора коррекции 9, число-импульсного преобразователя (ЧИП) 10, элемента НЕ 11, элементов И 1214, элемента ИЛИ 15, блок управления 16, генератор тактовых импульсов 17, выход (n-l)-ro разряда 18, управляющий вход второго коммутатора 19, выход 20 младщего разряда второго коммутатора, выход 21 переполнения сумматора адреса, установочный вход 22 число-импульсного преобразователя, число-импульсный выход 23 число-Импульсного преобразователя, выход 24 старшего разряда сумматора коррекции, прямой выход 25 (т+1)-го разряда входного регистра, выход 26 переполнения число-импульсного преобразователя, тактовый вход 27 число-импульсного преобразователя. Устройство.работает следующим образом. В устройстве по 12 - разрядному коду угла сх Оёос6.27т:()регистр 1 ци шически вырабатывает в каждом цикле преобразования 11 - разрядные коды . и соь CV . а также формирует импульс конца определения кода cos и импульс конца определения кода ып и выдает эту информацию на выходы. Старщие разряды у кодов sin и coSc знаковые и определяются по двум старшим разрядам регистра 1. Поэтому 12-й разряд регистра 1 является знаковым разрядом кода sifi л. , а знаковый разряд кода COS J определяется сумматором 2 как сумма по модулю два логических значений 11-го и 12-го разрядов регистра 1. Определение кодов чисел и |соЬ(А.| осуществляется методом кусочно-плинейной аппроксимации и использованием тригонометрических формул приведения. Аппроксимация функций производится по синусной функции в уг(. (-f-г-) который разбит на 17 равных участков. Величина каждого из .«.г..этих участков равна радиан, а узловая точка выбрана в середине участка аппроксимации. С помощью блока управления 16 коды l indlf и Icob- t определяются последовательно в каждом цикле преобразования, состоящем из двух периодов Т1 и Т2, В течение Т1 определяется код |sii(l а в течение Т2 - код |coscC| Поэтому блок управления 16 по значению 11-го разряда угла оС регистра 1 на выходе 19 вырабатывает для комм татора кодов 4 управляющий сигнал таки образом, что в течение Т1 с выходов ком мутатора кодов 4 снимается 5-разрядны код угла (Tl) tx:,,.aliv5c np.v . упрО а в течение Т2-5-разряднь й .код угла .)-oc,,,.QM где О-11-разр5 :1гый коэффициент 11-го разряда 1, а (.- -угол, величина которого опредеп ртся разрядами регистра ,1 с 6-го разряда по 10-й разряд, представляющий собой управляющую часть уг ла с регистра 1, по которой в каждом из периодов преобразования Т1 го1иТ2про« изводится определение значения функции начальной точке участка аппроксимации и направления изменения функции при аппроксимации (слева направо или справа налево от начальной точки аппроксимации). Младщие пять разрядов регистра 1 определяют угол « аппр., представляющий собой аппроксимирующую часть угла й регистра 1, по которой производится конечное определение функции ( течение Т1 и 1ссь,1 в течение Т2. Прямой и инверсный код угла i аппр. с выходов регистра 1 поступает на коммутатор кодов 3, работа . которого управляется инверсным значение 6-горазряда регистра 1 таким образом, что на выходах коммутатора кодов 3 вырабатывается пяти-разрядный код угла, .с«б - - оппр/ Код 3 аппр. схЬ поступает на инфс мацион Hbie входы старших разрядов ЧИП 10, На информационный вход младшего разряда ЧИП 10, с целью повышения точности преобразования угла аппр. (схЬ ) в число-импульсный код поступает с регистра 1 инверсное значение 6-го разряда угла 5. . обозначив код гш информационных входах 10 через :. аппр.(схб) аппр(аб) annpiC Voc pe где с. аппр. - представляет собой 6-разрядный код угла (вес младшего разряда этого кода равен радиан), младщий разряд которого всегда равен О, а старшие разряды определяются кодом угла Перед началом цикла преобразования в счетчике 5 и ЧИП 10 содержатся результаты предыдущего цикла преобразования, т.е. в счетчике 5 хранится код coj А. - предыдущего цикла преобразования, а ЧИП 10 находится в О. С выходов коммутатора кодов 4 код 4-х старщих разрядов угла стС упр (Т1) и с выхода .20 значение младщего разряда кода « упр. (Т1) поступают соответственно на входы первого слагаемого и вход второго одноразрядного слагаемого сумматора адреса 7. По коду о. упр. (Т1) сумматор адреса 7 вьхрабатывает 4-раз-. рядный код суммы j (Т1) и логический сигнал признака переполнения П21, вырабатываемый на выходе 21 сумматора адреса 7. Код (Т1) определяется выражением(тО-|%,2из ряда ОД....14,15, где ответственно разрядный и весовой коэф- ф1щиенты I го разряда кода j (Т1). Младщий разряд кода i- упр. (Т) с логическим значением А с выхода 20 коммутатора кодов 4 поступает также на вход 5правления направлением счета счетчика и управляющий вход сумматора 9, При этом, еслиД 0, то счетчик - 5 установлен на счет в +, а если А 1, то разрешен счет в -. Кроме того, в зависимости от значения Д на выходах сумматора 9 вырабатывается шестиразрядный код углового коэффщиента на правой или левой половине участка аппроксимации, т.е. код Krn). тл)(т поступающий на числовые входы ЧИП 10. Логический сигнал с выхода 21 непосредственно управляет по первому входу работой элемента И 12, а через элемент НЕ 11, по первым входам - работой элементов И 13 к 14. Пусть рассматр1таемому циклу преобразования соответствует такой код угла 2, что в течение Т1 и Т2 . Цикл начинается с пр 1ходом от источника сии7. 7

хроимпуль.сов 17 на блок управления 16

старт-импульса. По старт-импульсу блок управления 16 на выходе 22,генерирует импульсы начала периода, по которому производится запись в счетчик 5 кода (Т2)-дсх; а в чип 10 кода

W ® оппр- V .

После этого блок управления 16 по так товым импульсам истлчника синхроимпульсов 17 иа выходе 27 вырабатывает серию из (N+1) импульсов, посэупающих на тактовый вход ЧИП 10. S4 импульсов этой серии представляют собой число-им пульсный код угла рСаппр. (Ol6 ) Чак оСаппр. (аб )j по которому ЧИП 10 на выходе 23 вырабатывает, число импульсный код произведения

оппрХае). ( К j.vA Ki(,,)

каждый импульс которого имеет вес 2 и поступает (так как ) через элементы 13 .и 15 на счетный вход счетчика-регистра 5. Так как при ( код ,ч4аппр (об ) Саппр . то в силу )- А.К j()VA (к j(C,, с выхода 26 ЧИП 10 импульс переполнения поступает также на вход обратной связи блока управления 16. После окончания этого импульса блока управлегшя 16 инвертирует на i выходе 19 управляющий сигйал таким образом, что с выходов коммутатора i кодов 4 будет сниматься код угла ctynpiTZ)-c pQ«V ;jTa и формирует импульс окончания периода Т1, по которому с выходовпреобразователя снимается код slaoc . После это-..,-.,. ). Av(-A).2-°.a6.K6. В момвнтйосле окончания (N+1) импульса ЧИП ,10 устанавливается О. После этого схема управления генерирует импульс г по которому.с выходов преобразователя может сниматься код совос На этом цикл вычисления заканчивается, а очередной цикл начнется только при поступлении на блок управления 16 от источника синхроимпульсов 17 следующего старт-импульса. В случае, когда в одном из периодов преобразования вырабатывается тфизнак переполнения сумматора адреса 7, т.е. когда 021-1, по нмпульсу начала периода преобразования, вырабатывается на выходе 22 схемы управления 16, в ЧИП 10 и счет чик-регистр 5 записываются соответст

35838

спецификации представления информации двоичным обратным кодом ЧИП ° аппр. будет представлен с погрешностью в один квант. Поэтому импульс переполне5 ния ЧИП 10 (импульс переполнения генерируеахзя ЧИП 10 по (N +1) импульсу на его тактовом входе, по которому импульс произведения .на выходе 23 ЧИП 10 не вырабатывается, что является осо0 бенностью ЧИП 10) используется для коррекции этой погрешности. На выходе элемента И 14 при , и .(К6-разрядный коэффициент кода старшего разряда корректирующего

сумматора 9) по импульсу переполнения ЧИП 10, поступающел г с выхода 26 ЧИП 10 на четвертый вход элемента И -14, вырабатывается кфректирующий нмпульс, поступающий через элемент 15 на счетный вход счетчика 5, Следовательно, после поступления на тактовый вход ЧИП 10 (N+1) импульсов на выходах счетчик-регистра 5 при вырабатывается код числа

Sin (Т1).дс«.-ь Av(-A). j (,,,5).2-°. QS.Keje lsinc lJ го, блок управления 16 на выходе 22 вновь генерирует импульс начала периода, по которому в счетчик 5 записывается код )Дос , а в ЧИП 10 - код - Затем блок управления16 повторно генерирует на выходе 27 серию из ( N +1) импульсов, после oкoliчaIШя котфой на выходах счетчик-регистра 5 вырабатывается при код числа аб) А,К,УЛ|К венно код cx.(a6) и sin о--о.. При этом сигналом разрешена работа элемента И12 и запрещена работа элементов И 13 и 14. Поэтому импульс 1Ещчала периода с выхода 22 блока управления 16 поступает с некоте ой задержкой через элементы 12 и 15 на счетный вход счетчика 5, который сщгналом разрешен для счета в -, Следовательно, в момент после окончавия импульса начала периода в счетчике - регистре 5 установится код 1111111111, который не изменится в течение всего рассматриваемого периода преобразователя, длительность котоРого определяется кодом о„„р.(ае) , записанным в ЧИП 1О. Погрешнееть воспроизвесЕиня функции при не. превышает 2. . Причем, независимо от того, что или длительность цикла преобразования является величиной, записимой только от кода о аппр. (Об ) и находится в пределах от ДО (V -) triif где гм - период частоты тактовых импульсов источника синхроимпульсов 17. Технико-экономическая эффективность настоящего изобретения заключается в том, что усложнение в предложенном преобразователе происходит только за счет увеличения емкости ПЗУ, и в то же время максимальная абсолютная ошибка воспроизведения функций прототипом составляет 3-2 , а у предложенного устройства эта ошибка не превьш1ает 2 f О . При этом предложенный преобразователь имеет не менее, чем в восемь раз меньшую длительность ци1сла преобразования. Структурная схема предлоладнного преобразователя позволяет производить дальнейшее увеличение точности воспроизведе ния функций без увеличения разрядности датчика кода угла. Формула изобретения Устройство для вычисления функций синуса и косинуса, содержащее п-разрядный входной регистр, сумматор по модулю два, первый и второй коммутаторы, реверсивный счетчик, блок памяти, число импульсный преобразователь, блок управления, генератор тактовых импульсов, причем прямые и инверсные выходы млад ших разрядов входного регистра (с первого по m -ый) через первый коммутатор подключены к соответствующим входам первой группы число-импульсного преобразователя, прямые и инверсные выходы разрядов входного регистра (с(т+1)-го по (п-2)-ой) подключены к соответству ющим входам второго коммутатора, выходы (п-1)-го и п -го разр$щов входног регистра подключены ко входам суммато pa по модулю два выход сумматора по модулю два и выход п -го разряда входного регистра являются соответственно выходом знака косинуса и выходом знак синуса устройства, первая группа выходо блока памяти подключена к установочны ЕУХодам реверсивного счетчика, выходы разрядов которого являются информацион ными выходами устройства, выход генер тора тактовых импульсов подключен к тактовому, а выход (n-l)-ro разряда входного регистра и выход переполнения число-импульсного преобразователя - к соответствующим управляющим входам блока управления, выходы которого подключены соответственно к управляющему входу второго коммутатора, тактовому и установочному входам число-импульсного преобразователя и входу управления записью реверсивного счетчика, один из выходов блока управления является выходом сигнала окончания формирования функций сиьгуса, а другой - выходом сигнала окончания (формирования функций косинуса устройства, отличающееся тем, что, с целью псжышения точности и быстродействия устройства для вычисления функций синуса и косинуса, оно содержит сумматор адреса, сумматор коррекции, элемент НЕ, три элемента П, элемент ИЛИ, причем выход младшего разряда второго коммутатора подключен ко входу первого, а остальные выходы второго коммутатора - ко входам второго слагаемого сумматора адреса, выходы разрядов суммы которого подключены к адресным входам блока памяти, а выход переполнения - к первому входу первого и через элемент НЕ - к первому входу второго и первому входу третьего элементов И, выходы первого, второго и третьего элемеюов И через элемент ИЛИ подключены к счетному входу реверсивного сче гчика, входы первого и второго слагаемого сумматора коррекции подключены соответственно ко второй и третьей группам выходов блока памяти, управляющий вход сул матора коррекции - к выходу младшего разряда коммутатора и управляющему входу реверсивного счетчика, выходы сумматора коррекции - ко второй группе входов число-импульсного преобразователя, второй.вход первого элемента И подключен ко входу управления записью реверсивного счетчика, второй вход второго элемента И - к числоимпульсному выходу число-импульсного преобразователя, вторсй вход третьего элемента И подключен к выходу старшего разряда сумматора коррекции, третий и четвертый входы третьего элемента Исоответственно к прямому выходу {т +1)го разряда входного регистра и выходу переполнения число-импульсногх) преобразователя, инверсный выход (т+1)-го разряда входного регистра подключен к управляющему входу первого коммутатора

.. ... - 11 ,.„. ....- ... .г

и ко входу Nmaauiero разряда пе рвой группы входов число-импульсного преобразователя.

Источники информации, принятые во внимание при экспертизе

1.Авторское св1щетольство СССР № 510717, кл. G 06 F 15/34, 1974.

2.Авторское свидетельетво СССР К 362448, кл. G 01 S 7/12, 1970 {прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Преобразователь кода угла в коды синуса и косинуса | 1977 |

|

SU684554A1 |

| Цифровой генератор функций | 1989 |

|

SU1663607A1 |

| Функциональный преобразователь кода угла | 1978 |

|

SU716042A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1163322A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Преобразователь двоичных кодов угла и дальности в двоично-десятичные коды | 1987 |

|

SU1432782A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

Знак Cos

}fod jSfnef/ unt /Cofef/ ч

Авторы

Даты

1980-03-25—Публикация

1977-09-26—Подача