Изобретение относится к вычислительной технике.

Известно устройство для корректировки двоичных арифметических кодов но авт. св. № 294142, в котором для обеспечения коррекции осуществляется вычисление остатка от корректируемого числа по модулю вида А , затем по вычисленному остатку из внешнего запоминающего устройства считывается код коррекции, состоящий из кода поправки, знака поправки и кода номера группы корректируемого числа, к которой необходимо прибавить код поправки, а затем осуществляется исправление корректируемого числа.

Однако в данном устройстве необходимо наличие внешней памяти для хранения кодов коррекции.

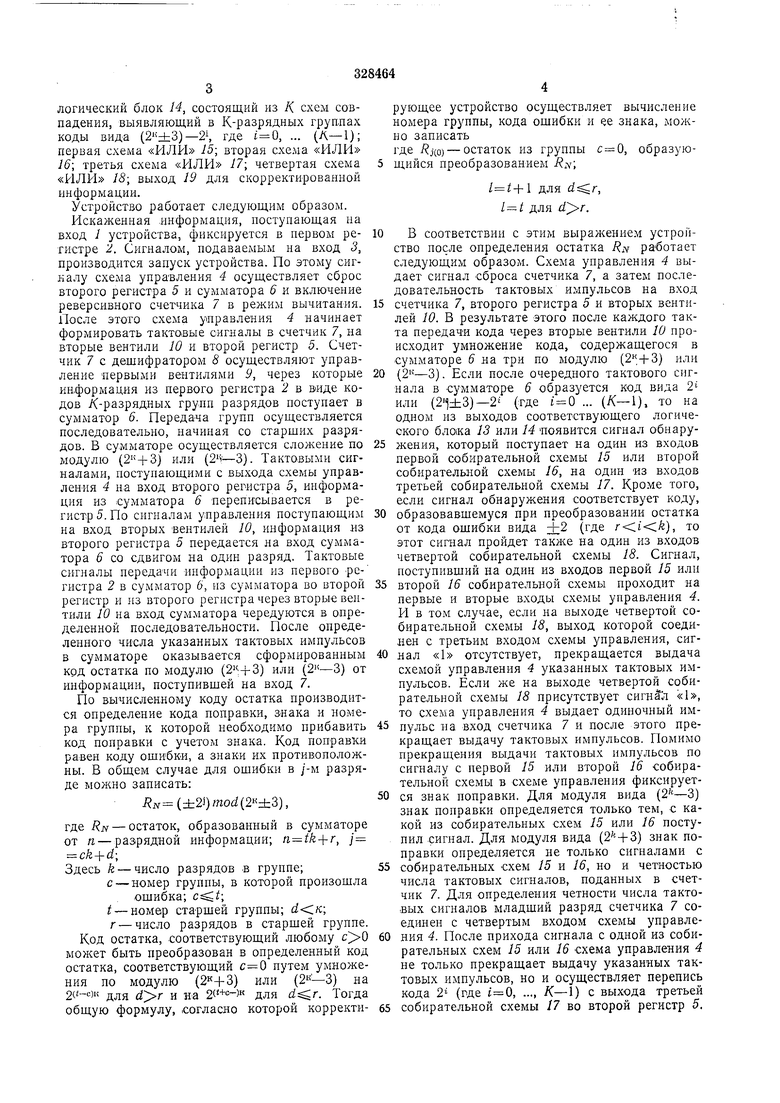

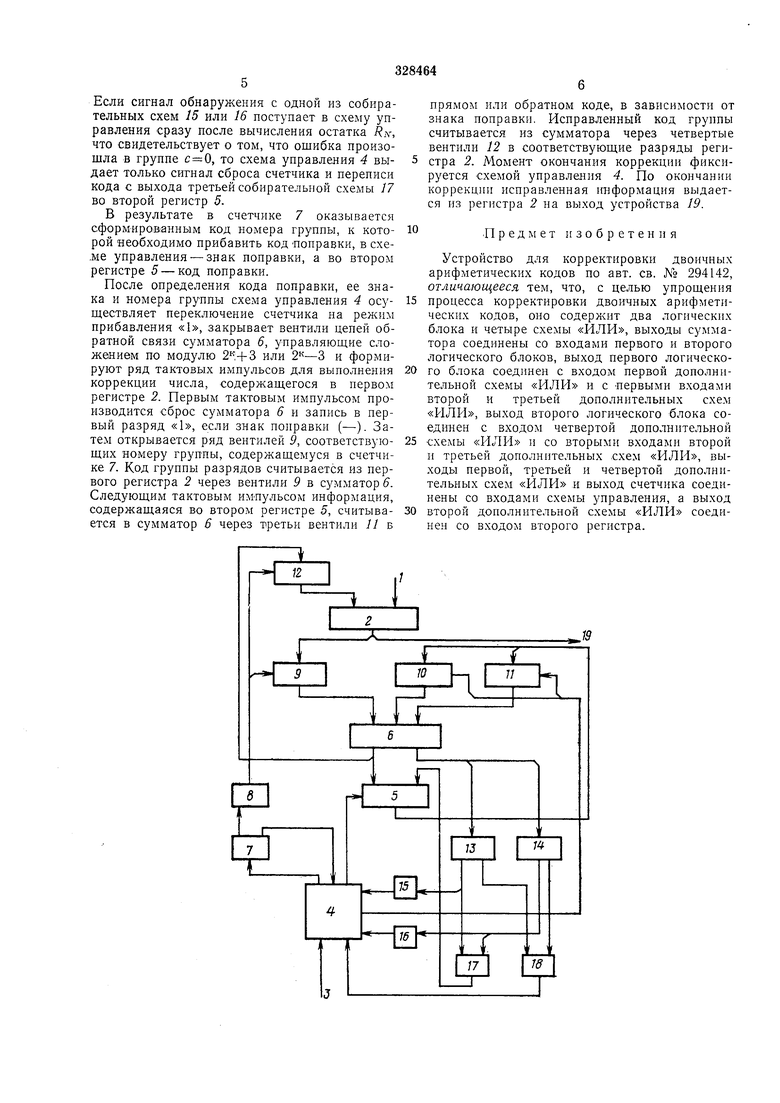

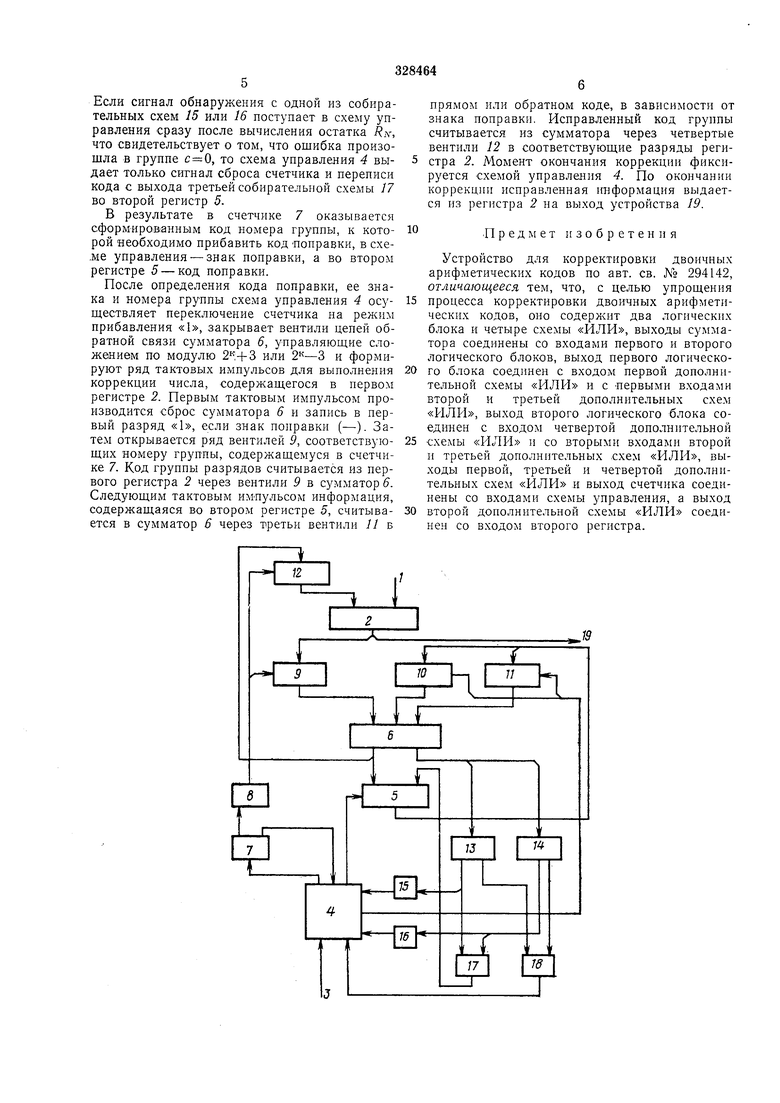

В состав предлагаемого корректирующего устройства введены два логических блока и четыре собирательных схемы, соединенные соответствующим образом с остальными схемами устройства, что обеспечивает возможность определения кода поправки, знака и номера К-разрядной группы путем преобразований предварительно вычисленного кода остатка. Такое выполнение устройства позволяет упростить процесс корректировки двоичных арифметических кодов.

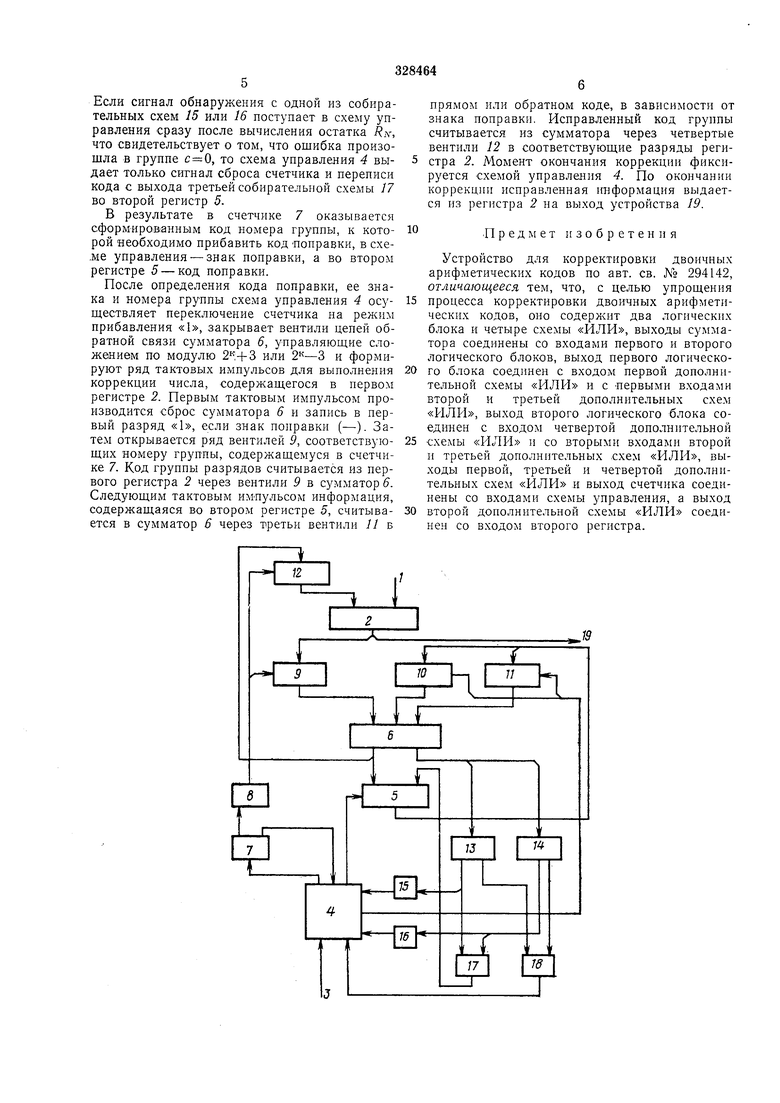

Она содер кит следующие элементы: цепь ввода 1 корректируе1мой я-разрядной информаци1,где n ili + r (k-число разрядов в группе, / - наибольший номер группы, / - число разрядов в старшей группе; лервый регистр 2, предназначенный для хранения кода числа, поступившего в устройство, и кода исправленного числа; вход J для сигнала запуска устройства; схему 4 управления; второй регистра,

предназначенный для хранения кодов групп и кода поправки; 6-(Д+1}-разрядный сумматор по модулю .(2±3) накапливающего тина; реверсивный счетчик 7 для управления считыванием инфор.мации пз регистра 2, и записью Л-разрядпыми групиалш, счетчик сч 1тает по модулю /; дешифратор 8, первые схемы «И 9 (вентили, предназначенные для считывания корректируемой информации /(-разрядными группами); вторые схе.мы «И 10

(вентили, предназначенные для переписи информации из регистра 5 в сумматор со сдвигом на один разряд влево); третьи схемы «li 11 (вентили, предназначенные для записи кода поправки из регистра 5 в су.м.матор в виде

прямого или обратного кода); четвертые схемы «И 12 (вентили, предназначенные для записи кодов групп исправленного числа); первый логический блок 13, состоящий из Л схем совпадения, выявляющих в /(-разрядный груплогический блок 14, состоящий из /( схсдМ совпадения, выявляющий в К-разрядиых груплах коды вида ()-2 где , ... (Л-1); первая схема «ИЛИ 15; вторая схема «ИЛИ 16; третья схема «ИЛИ 17; четвертая схема «ИЛИ 18; выход 19 для скорректированной информации.

Устройство работает следующим образом.

Искаженная .информация, поступающая на вход 1 устройства, фиксируется в первом регистре 2. Сигналом, подаваемым на вход 3, производится запуск устройства. По этому сигкалу схема управления 4 осуществляет сброс второго регистра 5 и сумматора 6 и включение реверсивного счетчика 7 в режим вычитания. После этого схема управления 4 начинает формировать тактовые сигналы в счетчик 7, на вторые вентили 10 и второй регистр 5. Счетчик 7 с дешифратором 8 осуществляют управление -первыми вентилями 9, через которые ИЕформация из первого регистра 2 в виде кодов Х-разрядных групп разрядов поступает в сумматор 6. Передача групп осуществляется последовательно, пачиная со старших разрядов. В сумматоре осуществляется сложение по модулю (2Ч-3} или ). Тактовыми сигналами, поступающими с выхода схемы управления 4 на вход второго регистра 5, информация из сумматора 6 переписывается в регистр 5. По сигналам управления поступающим на вход вторых вентилей 10, информация из второго регистра 5 передается на вход сумматора 6 со сдвигом на один разряд. Тактовые сигналы передачи информации из первого регистра 2 в сумматор 6, из сумматора во второй регистр и из второго регистра через вторые вентили 10 на вход сумматора чередуются в определенной последовательности. После определенного числа указанных тактовых импульсов в сумматоре оказывается сформированным код остатка по модулю (2,+3) или () от информации, поступившей на вход 7.

По вычисленному коду остатка производится определение кода поправки, знака и номера группы, к которой необходимо прибавить код поправки с учетом знака. Код поправки равен коду ошибки, а знаки их противоположны. В общем случае для ошибки в /-м разряде молаю записать:

(±2i)mod(,

где RN - остаток, образованный в сумматоре от п - разрядной информации; n.tk + r, I- ck+d; Здесь k - число разрядов в группе;

с - номер группы, в которой произошла ошибка;

t - номер старшей группы;

г - число разрядов в старщей группе. Код остатка, соответствующий любому может быть преобразован в определенный код остатка, соответствующий путем умножения по модулю () или () на 2((-c)K для . JJ jj:a 2()« для . Тогда общую формулу, (Согласно которой корректирующее устройство осуществляет вычисление номера группы, кода ошибки и ее знака, можно записать

где Rj(Q) - остаток из группы с 0, образующийся преобразованием

для , l-t для .

В соответствии с этим выражением устройство после определения остатка работает следующим образом. Схема управления 4 выдает сигнал сброса счетчика 7, а затем последовательность тактовых импульсов на вход

счетчика 7, второго регистра 5 и вторых вентилей 10. В результате этого после каждого такта передачи кода через вторые вентили 10 происходит умножение кода, содержащегося в сумматоре 6 на три по модулю (2,+3) или

(). Если после очередного тактового сигнала в сумматоре 6 образуется код вида 2 или ()-2 (:где i 0 ... (/(-1), то на одном из выходов соответствующего логического блО|Ка 13 или 14 появится сигнал обнаружения, который поступает на один из входов первой собирательной схемы 15 или второй собирательной схемы 16, на один из входов третьей собирательной схемы 17. Кроме того, если сигнал обнаружения соответствует коду,

образовавшемуся при преобразовании остатка от кода ошибки вида +2 (где ), то этот сигнал пройдет таклсе на один из входов четвертой собирательной схемы 18. Сигнал, поступивший на один из входов первой 15 или

второй 16 собирательной схехмы нроходит на первые и вторые входы схемы управления 4. И в том случае, если на выходе четвертой собирательной схемы 18, выход которой соединен с третьим входом схемы управления, сигнал «1 отсутствует, прекращается выдача схемой управления 4 указанных тактовых импульсов. Если же на выходе четвертой собирательной схемы 18 присутствует сигнал «1, то схема управления 4 выдает одиночный импульс на вход счетчика 7 и после этого прекращает выдачу тактовых импульсов. Помимо прекращения выдачи тактовых импульсов по сигналу с первой 15 или второй 16 собирательной схемы в схеме управления фиксируется знак поправки. Для модуля вида () знак поправки определяется только тем, с какой из собирательных схем 15 или 16 поступил сигнал. Для модуля вида (2+3) знак поправки определяется не только сигналами с

собирательных схем 15 и 16, но и четностью числа тактовых сигналов, поданных в счетчик 7. Для определения четности числа тактовых сигналов младший разряд счетчика 7 соединен с четвертым входом схемы управления 4. После прихода сигнала с одной из собирательных схем 15 или 16 схема управления 4 пе только прекращает выдачу указанных тактовых импульсов, но и осуществляет перепись кода 2 (где К-1) с выхода третьей

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для КОРРЕКТИРОВКИ двоичных АРИФМЕ1ИЧЕСКИХ КОДОВ | 1971 |

|

SU294142A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| УСТРОЙСТВО для ПРЕРЫВАНИЯ ПРОГРАММ | 1973 |

|

SU368604A1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для вычисления функции @ =2 @ | 1981 |

|

SU1057942A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| Устройство для формирования остатка по произвольному модулю от числа | 2021 |

|

RU2760927C1 |

| Преобразователь двоичного кода вдВОичНО-дЕСяТичНый | 1979 |

|

SU847318A1 |

Даты

1972-01-01—Публикация