Устройство относится к триггерным пересчетным схемам, применяемым в радиоэлектронике, дискретной автоматике и смежных областях техники.

Среди таких схем особое место занимают схемы с последовательным опознаванием, обладающие рядом ценных специфических особенностей, в частности, весьма малой задержкой выходных импульсов относительно входных при любом коэффициенте пересчета k.

Известно несколько вариантов подобных схем, построенных на различных (в том числе и бинарных) элементах и имеющих как фиксированные, так и управляемые значения k. Однако на практике схемы с последовательным опознаванием используются довольно редко, так как опубликованные варианты таких схем обладают серьезными недостатками, главным из которых является не высокое быстродействие. Причину этого нетрудно понять, анализируя классический вариант схемы с последовательным опознаванием. В этой схеме требуемые значения k получаются путем записи соответствующего кода в основной счетчик в начале цикла счета импульсов с выхода схемы, аналогично тому, как это делается в общеизвестной схеме с импульсными обратными связями. При этом установка исходного состояния происходит без отключения схемы от источника запускающих импульсов, в резуль-.

тате чего при произвольном k первый триггер за один период входной частоты должен срабатывать дважды (как н в схеме с обратными связями). Более того, быстродействие известной схемы оказывается далее ниже, чем в схеме с импульсными обратными связями изза того, что в момент появления импульса на общем выходе схемы основной счетчик находится в состоянии 11 ... 11. Вследствие этого при записи кода в отдельных разрядах основного счетчика возникают импульсы переноса в последующие разряды, что требует удлинения импульса установки кода и, следовательно, дополнительно уменьшает быстродействие. Кроме того, ненулевое исходное состояние основного счетчика в момент установки кода понижает надежность работы схемы из-за наличия импульсов одновременно на обоих входах триггеров и повышения требований к длительности импульса установки кода.

Наконец, при использовании такой схемы в управляемом счетчике ненулевое состояние основного счетчика в момент установки кода создает дополнительные трудности в управлеНИИ величиной k, так как из-за появления на входах триггера основного счетчика импульсов переноса из предыдущих разрядов необходимо иметь активный сигнал как для установки какого-либо триггера в состояние «1,

ние «О. При электромеханической коммутации это потребует применения контактов, работающих на переключение, а при электронном управлении величиной k удвоенного числа элементов в схеме управления величиной k.

Для повышения быстродействия подобных схем в литературе предложено использовать в таких схемах сквозной нервное. Однако поскольку установка кода и в этом случае производится при ненулевом исходном состоянии основного счетчика и без отключения его от источника запускающих импульсов, то эта мера оказывается недостаточно эффективной и быстродействие полученной схемы все же существенно ниже быстродействия обычного счетчика.

Эффективным средством повыщения быстродействия является использование вспомогательного счетчика с отключением основного счетчика от входа схемы на время установки кода, однако при этом резко возрастает число элементов в схеме и, кроме того, сохраняются все остальные упомянутые вьшш недостатки, связанные с ненулевым состоянием основного счетчика в момент установки кода.

Предлагаемое устройство позволяет устранить недостатки известных схем без существенного увеличения количества оборудования. Основное отличие этого устройства от известных вариантов заключается в такой модификации схемы с последовательным опознаванием, при которой в момент появления импульса на выходе схемы основной счетчик находится в состоянии 00...00 (а не в состоянии 11... 11), а запись кода в этот счетчик осуществляется при отключении счетного входа основного счетчика от источника запускающих импульсов.

С этой целью нулевые входы ячеек опознавания соединены с теми же выходами триггеров основного счетчика, с которых снимаются импульсы переноса.в следующий разряд (а не с дополнительными выходами, как в известных схемах) и, кроме того, в цепях переноса основного счетчика установлены вентили, управляемые с выходов соответствующих ячеек опознавания. При этом на нулевой вход первой ячейки опознавания импульсы поступают непосредственно со входа схемы, а вентиль, управляемый этой ячейкой, установлен на входе основного счетчика.

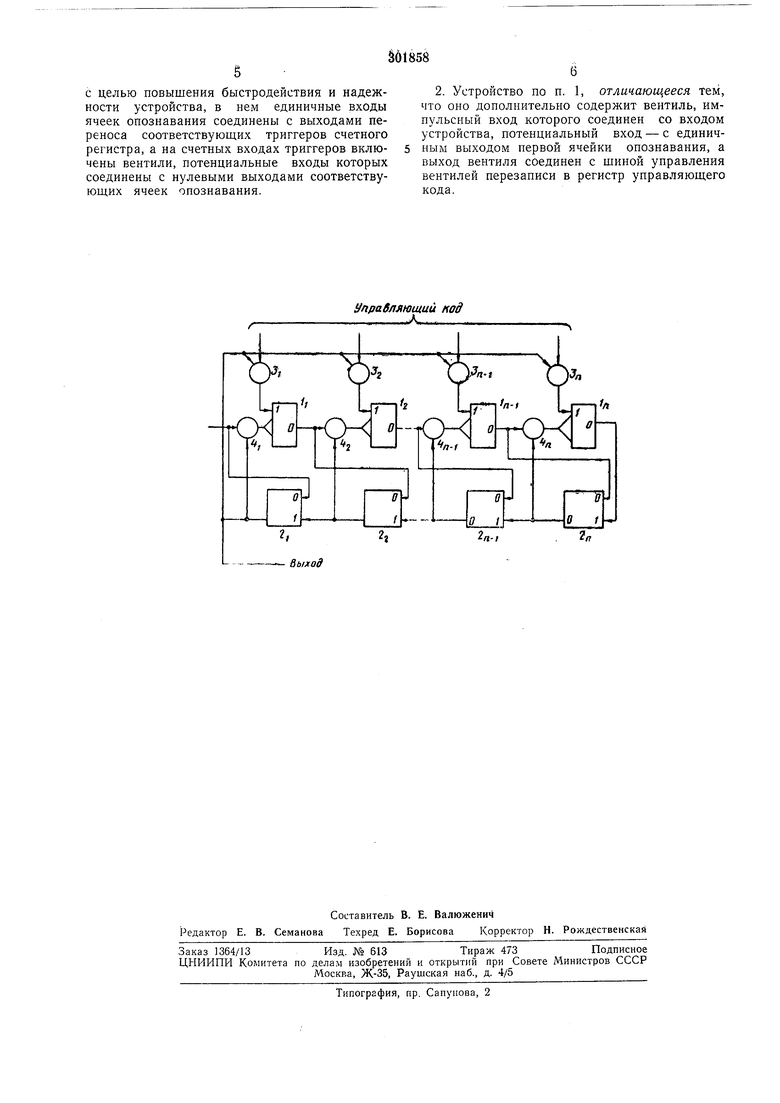

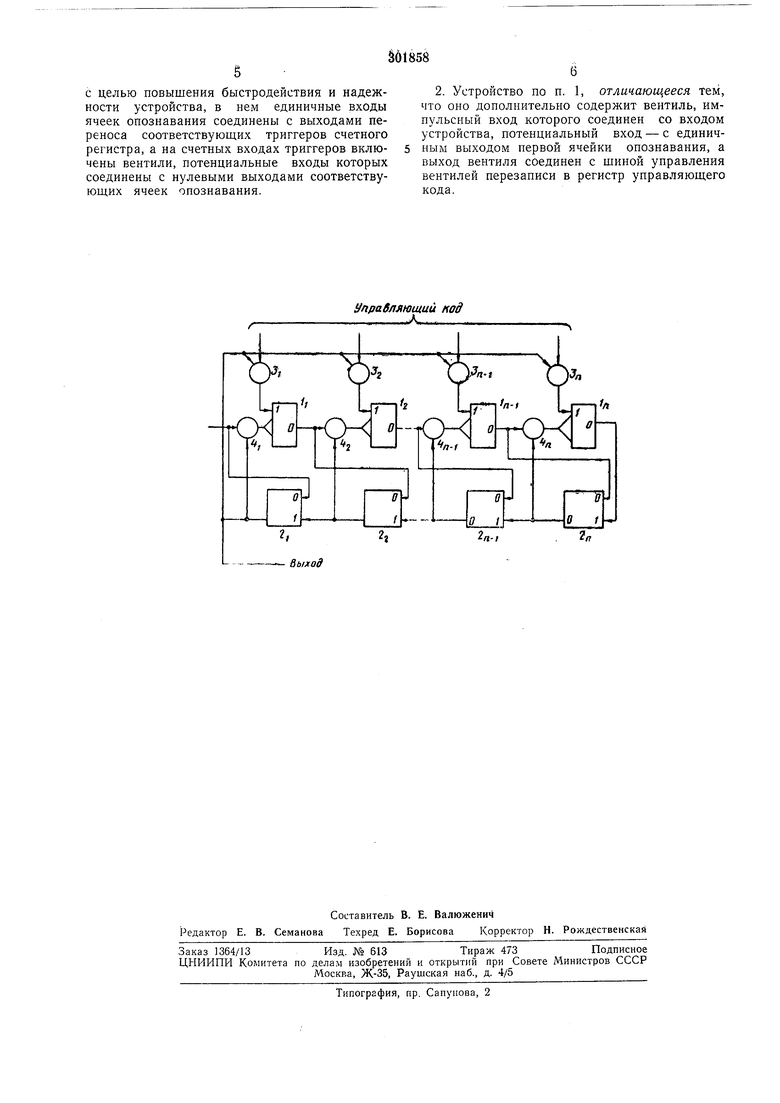

На чертеже показана схема описываемого устройства.

Оно СОСТОИТ из триггеров li-In, образующих счетный регистр, ячеек опознавания 2i- 2п, соединенных с этими триггерами таким образом, что нулевой вход й-й ячейки опознавания соединен с нулевым выходом (k- 1)-го триггера, а единичный выход данной ячейки соединен с нулевым выходом k-ro триггера, вентилей нерезаписи управляющего кода на триггера и вентилей 4i-4n связи нулевого выхода предыдущего триггера со счетным входом последующего.

Работа предлагаемой схемы сводится к следующему.

В исходном состоянии в счетный регистр записан исходный код А (в зависимости от

требуемого k), а все ячейки опознавания находятся в состоянии «О. После прихода Л входных импульсов на выходе счетного регистра появляется импульс, перебрасывающий в состояние «1 ячейку 2„, которая закрывает вентиль 4п- После прихода следующих импульсов на вход схемы появляется импульс на выходе триггера In-i, который сбрасывает в состояние «О ячейку 2п и устанавливает в состояние «1 ячейку , которая в свою очередь закрывает вентиль 4n-i. Па вход же триггера In этот импульс не проходит, так как вентиль 4п в момент появления этого импульса закрыт. Далее процесс продолжается аналогичным образом: после прихода еще 2 входных импульсов появляется импульс на выходе триггера In-z, который сбрасывает в состояние «О ячейку 2п- и устанавливает в состояние «1 ячейку , но не проходит на вход триггера 1п- и т. д.

При установке в состояние «О ячейки 2i выдается импульс на выход схемы, который используется и для установки начального кода в основной счетчик через вентили i-Зп, после чего схема приходит к исходному состоянию.

Импульс на выход схемы и на установку кода в основной счетчик можно получать и несколько иным образом: с помощью дополнительного вентиля, управляемого с единичного

выхода ячейки опознавания 2i. В этом случае импульс установки кода будет получаться с несколько меньшей задержкой относительно входного импульса, чем в приводимой схеме (что несколько увеличит быстродействие схемы).

Описанный выше принцип построения пересчетных схем может быть использован в схемах как с фиксированным, так и с управляемым k, а также при неполном числе ячеек

опознавания. В последнем случае для уменьшения числа элементов в схеме ячейки опознавания и управляемые ими вентили имеются не во всех, а только в нескольких младших разрядах счетчика. При этом единичный вход

ячейки опознавания с наибольшим номером соединяется с выходом основного счетчика, а остальные входы и выходы ячеек опознавания подключаются к основному счетчику.

Предмет изобретения

1. Двоичное пересчетное устройство с последовательным опознаванием, содержащее регистр из триггеров со счетными входами, ячейки опознавания и вентили перезаписи в регистр кода, определяющего коэффициент пересчета, причем выход первой ячейки опознавания, являющийся одновременно выходом устройства, соединен с общей шиной управления

с целью повышения быстродействия и надежности устройства, в нем единичные входы ячеек опознавания соединены с выходами переноса соответствующих триггеров счетного регистра, а на счетных входах триггеров включены вентили, потенциальные входы которых соединены с нулевыми выходами соответствующих ячеек опознавания.

2. Устройство по п. 1, отличающееся тем, что оно дополнительно содержит вентиль, импульсный вход которого соединен со входом устройства, потенциальный вход - с единичным выходом первой ячейки опознавания, а выход вентиля соединен с шиной управления вентилей перезаписи в регистр управляющего кода.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛА ВРЕМЕНИ В ЦИФРОВОЙ КОД | 1973 |

|

SU391587A1 |

| ДЕСЯТИЧНЫЙ СЧЕТЧИК | 1971 |

|

SU292244A1 |

| Устройство для опроса источников дискретных сообщений | 1980 |

|

SU955015A1 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА С АВТОМАТИЧЕСКИМ ПРОГРАММИРОВАНИЕМ И МИКРОПРОГРАММНЫМ УСТРОЙСТВОМ УПРАВЛЕНИЯ | 1964 |

|

SU224161A1 |

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1968 |

|

SU217718A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ ДВОИЧНОГО КОДА В ИЗБЫТОЧНЫЙ ЦИКЛИЧЕСКИЙ КОД | 1971 |

|

SU318939A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| Дробный делитель частоты следования импульсов | 1983 |

|

SU1120490A1 |

| ЦИФРОВАЯ МАШИНА ДЛЯ ПОИСКА ИНФОРМАЦИИ | 1966 |

|

SU214201A1 |

| Дешифратор времяимпульсных кодов | 1991 |

|

SU1807562A1 |

г,

Упраблянзший код J

г

2«.

/I-;

Даты

1971-01-01—Публикация