(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU822292A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU815769A2 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Вероятностный коррелометор | 1980 |

|

SU892449A1 |

| Устройство для приема и обнаружения комбинации двоичных сигналов | 1987 |

|

SU1413656A1 |

| Устройство для упорядочения массива чисел | 1986 |

|

SU1383336A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

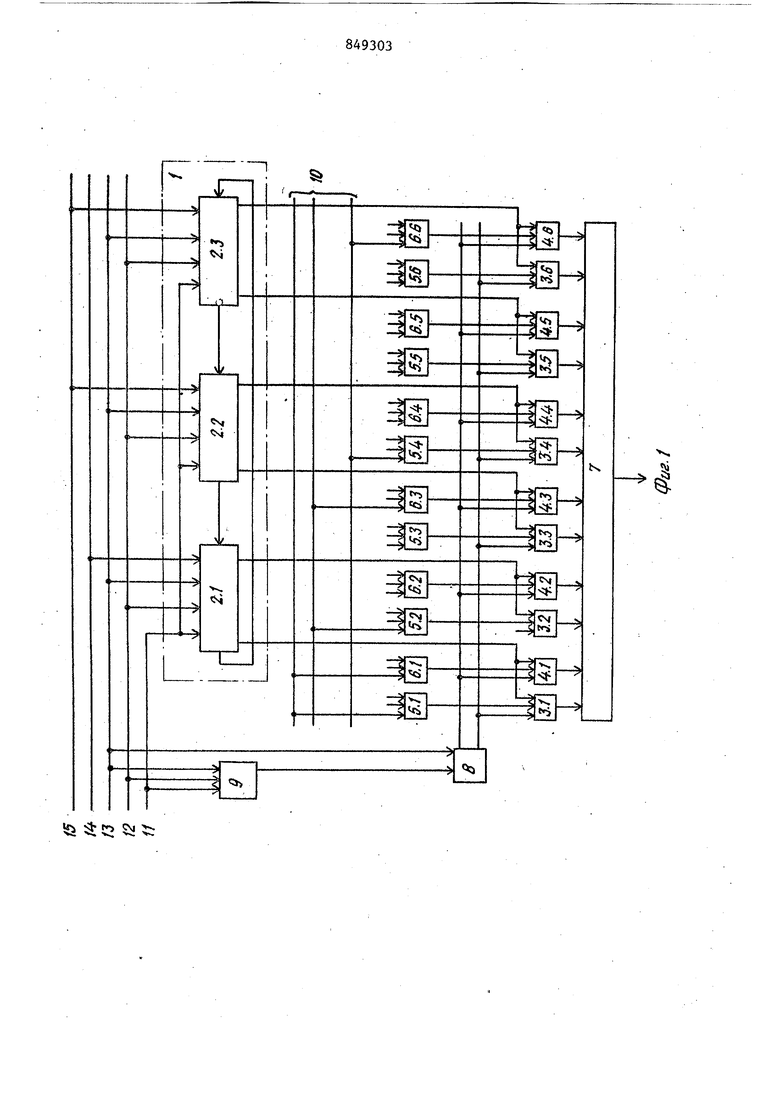

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах ЦВМ с последовательной обработкой ииформащп-. Известно постоянное запоминающее устройство (ПЗУ) с вьщачей информации в последовательном коде, которое содержит регистр, входы которого соединены с соответствующими логичес кими шинами, и адресные шины, элементы И и ИЛИ, причем первые входы элементов И соединены с соответствую щими выходами регистра, вторые - с соответствующими адресными шинами, а выходы - со входами элемента ИШ j Недостатком этого устройства является большое количество разрядов регистра при хранении большого количества чисел, так как для хранения т, п-разрядных чисел необходим регистр разрядности m-t-n-1, где m количество чисел, an- разрядность Iзаписанных чисел. Наиболее близким по технической сущности к предлагаемому является устройство, которое содержит .регистр сдвига, шины управления, элементы И по количеству разрядов регистра и элемент ИЛИ, причем выходы разрядов регистра сдвига соединены с информационными входами элементов И, управляющие входы которых подключены к соответствующим.адресным шинам, а выходы соединены со выходами элет мента ИЛИ, информационные входы регистра сдвига подключены к соответствующим шинам логических нуля и единицы, вход разрешения записи регистра сдвига соединен с шиной Обращение, а выход последнего разряда регистра сдвига подключен ко входу его первого разряда . Недостатком известного ПЗУ является его сложность при хранении больших массивов, чисел, так как количество запоминающих ячеек m регистра сдвига равняется количеству хранимых чисел в ПЗУ. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что постоянное запоминающее устройство, содержащее регистр сдвига, информационные входы которого соединены с соответствующими шинами логических нуля и единицы, а выходы - с информационными входами основных элементов И, выходы которых соединены с одними входами элемента ИЛИ, и шины управления Обращения, тактовая и шина установки в исходное состояние, к которым подключены соответствующие входы регистра cдirйгa, оно содержит дополнительные элементы И, триггер, двоичный счетчик и труппы элементов ИЛИ, входы которых подключены к адресным шинам, выходы элементов ИЛИ одной группы соединены с соответствую щими упра ляющими входами основных элементов И, а выходы элементов ИЛИ другой группы соединены с соответству ющими управляющими входами дополнительных элементов И, информационные входы которых соединены с выходами разр дов регистра сдвига, а выходы подключен к соответствующим входам элемента ИЛИ входы двоичного счетчика подключены к шинам управления Обращение, тактовой и к шине установки в исходное состояние, которая подключена к нулевому рходу триггера, нулевой выход ко торого подключен к первому управляюще му входу основных элементов И, а единичный выход - к первому управляющему входу дополнительных элементов И, еди ничный вход триггера соединен с выходом двоичного счетчика. . На фиг. 1 представлена блок-схема устройства на 36 восьмиразрядных двоичных числах; на фиг. 2 - ориентированный эйлеров граф для четырехразрядных: двоичньпс чисел. ПЗУ содержит кольцевой регистр 1 сдвига, состоящий из п ячеек 2 памяти, основные п элементы И 3, дополнительные п элементы И 4, первую группу п элементов ШЕ 5, вторую п группу элементов 6, элемент ИЛИ 7, триг гер 8, двоичный счетчик 9, шины управления: адресные 10, Обращение 11, тактовую 12, установки в исходно состояние 13, логические 1 и О соответственно 14 и 15. Прямые и обратные выходы регистра 1 сдвига, которыми являются прямые и 8 34 обратные выходы его ячеек 2 памяти, подсоединены к информационным входам элементов И 3 и,группы элементов И 4, вторые управляющие входы которых подключены к выходам двух групп элементов ИЛИ 5 и ИЛИ 6 соответственно. Выходы элементов И 3 и группы элементов И 4 подключены ко входам элемента ИЛИ 7, причем первые управляющие входы элементов И 3 и группы элементов И 4 соединены соответственно с нулевым и единичным выходами триггера 8, единичный вход которого подключен к выходу двоичного счетчика 9. Входы двух групп элементов ИЛИ 5 и ИЛИ 6 подключены к соответствующим адресньп шинам 10. Шина 11 Обращение соединена со входами разрешения записи регистра 1 сдвига и счетчика9. Тактовая шина 12 соединена с тактовьми входами ячеек 2 памяти и счетным входом счетчика 9. Установочные -входы ячеек 2 памяти и счетчика 9, а таКже нулевой вход триггера 8 подключен не 13 установки в исходное соетояние. Информационные параллельные входы регистра I сдвига подключены либо к шине 14 логической 1, либо к шине 15 логического О. Регистр 1 сдвига предназначен для записи начального кода числа, определяемого соединением информационных параллельных входов регистра1 сдвига с теми или иными шинами 14 и 15 логических 1 и О, и является накопителем информации. Изменяя подсоединения входов регистра 1 к логическим шинам, изменяется начальный код, записьшаемый в регистр 1 сдвига и, тем самым, изменяется массив 2п-разрядных чисел записанных в устройство. В новом массиве 2п-разрядные числа состоят из другого множества п-разрядных чисел, которое определяется новым начальным кодом, записанным в регистр 1 сдвига. Группы элементов ИЛИ 5 и ШШ 6 служат для организации произвольной выборки чисел по данному адресу путем подсоединения входов этих элементов к соответствующим адресным шинам 10, причем для выборки одного числа к выбранной адресной шине 1 О подключают один вход элемента ИЛИ 5 и один вход элемента ШШ 6. ПЗУ работает следующим образом. , В исходном состоянии регистр I сдвига, триггер 8 и счетчик 9 находятся в нулевом состоянии. При подаче Обращение с щины 1J Об импульса ращение на входы регистра 1 сдвига и счетчика 9 приходит разрешающий сигнал, который подгота ливает счетный вход счетчика 9 и. в регистр 1 сдвига записывает начальньй код числа, который с выходов яч ек 2 памяти поступает на информацион ные входы соответствующих элементов И 3 и И 4. Одновременно с импульсом Обращение возбуждается одна выбран ная адресная шина 10, с которой разрешающий сигнал через один элемент ИЛИ 5 и один элемент ШШ 6 подается на вторые управляющие входы соответствующих элементов И 3 и И 4, а так как на первых управляющих входах всех элементов И 3 установлен разрешающий сигнал с нулевого выхода триг гера 8, то с выхода элемента И 3 через элемент ИЛИ 7 на выход устройств поступает первый разряд выбранного числа. После формирования на выходе устройства первого разряда выбранного числа подается первый тактовый сигна на щину 12, и информация сдвигается, в .регистре 1 .сдвига на один разряд по кольцу, подключая-к выходу устройства .второй разряд начального код Одновременно этот тактовый сигнал поступает на подготовленный счетный вход счетчика 9. После сформирования на выходе устройства второго разряда выбранного числа подается второй тактовый сигнал на шину 12, и информация снова сдвигается в регистре 1 сдвига на один разряд по кольцу, подключая к выходу устройства третий разряд начального кода причем тактовый сигнал .поступает также на счетный вход счетчика 9. . После проведения п-1 сдвигов посредством подачи п-1 тактовых импульсов, где п-разрядность хранимых в ре гистре 1 сдвига чисел, на выходе ус ройства сформируются первые п разрядов -выбранного числа, которые, являются разрядами одного из п-разрядных чисел, записанных в регистру 1 сдвига. При поступлении п тактового импуль са информация сдвигается в регистре I сдвига на один разряд по кольцу, а на выходе счетчика 9 заканчивается формирование сигнала, который поступает на единичный 03 6 вход триггера 8 и устанавливает на его единичном выходе разрешающий сиг-; нал, который подается на первые управляющие входы всех элементов И 4, тем самым подключая к выходу устройства выход другой ячейки 2 памяти, из которой информация поступает через элементы И 4 и ИЛИ 7 на выход устройства, и формируется п+1 разряд выбранного числа, который одновременно является первым разрядом п-разрядного числа, записанного в регистре I сдвига. С поступлением последующих п-1 тактовых импульсов из регистра 1 сдвига выбираются оставшиеся п-1 разрядов второго п-разрядного числа, записанного в регистр 1 сдвига, а на выходе устройства сформируются последние п-1 разрядов выбранного числа. . Таким образом, после окончания 2п-1 тактового импульса на выходе устройства сформируются все 2п разрядов выбранного из устройства числа. Затем на шине 13 установки в исходное состояние формируется сигнал, по окончании которого снимается возбуждение с адресной шины 10 и шины 11 Обращение, .а регистр 1 сдвига, триггер 8 и счетчик 9 устанавливаются в нулевое состояние. Устройство готово к следующему обращению. В предлагаемом устройстве (фиг. I) хранится 36 восьмиразрядньк двоичных числа (6 36, количество перестановок с повторениями из шести элементов по 2) . В качестве начального кода числа в регистре 1 записан код 100, который является кодом ориентированного цикла, образованного ориентированным эйлеровым графом. Для четырехразрядных чисел ориентиованный эйлеров граф (фиг. 2) имеет ребер. Каждому ребру графа поставено в соответствие одно четырехразрядое число. Замкнутая последовательость неповторяющихся ребер при из ocnefj,oBaTenbHoii обходе в направлении трелок образуют цикл. Для получения ода ориентированного цикла надо взять таршие разряды чисел, которым соотетствуют ребра цикла при последоваельном обходе цикла в .направлении трелок. Начинать обход цигапа можо с любого ребра, принадлежащего анному циклу.

Коду ориентированного цикла 100 принадлежат числа 1001, 0010 и 0100. Из кода ориентированного цикла путем п-1 сдвига (где п-разрядность чисел графа) в направлении от младших разрядов к старшим (влево) получаются коды чисел, которым соответствует этот код ориентированного цикла

1

001

010

100

В результате сдвигов в столбцах получились три числа, которым соответствуют ребра, принадлежащие даннму циклу{фиг. 2) Q

Так как ячейки 2 памяти регистра 1 сдвига имеют и обратные выходы, то фактически в регистре 1 записаны два начальных кода: 100 и 011, Коду 011 также соответствует цикл в эйлеровом графе с ребрами, которым соответствуют числа ОНО, 1101 и 1011, например

ш

ПО

101

011

В устройстве (фиг. 1) хранятся восьмиразрядные числа, состоящие из двух четырехразрядных чисел, которые записаны в регистре 1 и выбираются из регистра 1 последовательн

Согласно подключению информационных параллельных входов регистра 1 к шинам 14 и 15 логических 1 и О, в ячейку 2.1 памяти записывается 1, и в ячейки 2.2 и 2.3 записывается О. Поэтому при считьшании первого числа на выходах ячейки 2.1 памяти формируются числа 1001 и 0110, на выходах ячейки 2.2-0010 и 1101, а на выходах ячейки 2.3 - 0100 и 1011.

При считьшании второго числа из регистра 1 числа 1001 и 0110 формируются на выходах ячейки 2.3 памяти, числа: 0010 и 1101 - на выходах ячейки 2.1 памяти, а числа 0100 и 1011 - на выходах ячейки 2.2 памяти Это вызвано тем, что после окончания считьшания первого числа в регистре 1 устанавливается код 100, который сдвигается на один разряд по кольцу п тактовым импульсом. В регистре 1 сдвига устанавливается код 001, который является начальным

кодом при выборке второго четырехразрядного числа. При поступлении последующих п-1 тактовых импульсов на прямых выходах регистра 1 сформируются следующие числа

ооГ

010 100 .001

На обратных выходах ячеек 2 памяти сформируются следующие числа

Гш

01 1 110

Таким образом,.при считывании первого и второго числа из одних и тех

же ячеек 2 памяти регистра 1 считываются различные числа, так как происходит сдвиг покольцу начального кода относительно выходов регистра 1 при считьшании второго числа относительно

5 первого. В приведенном примере происходит этот сдвиг влево -на один разряд регистра 1, так как и n-m, где празрядность записаннь1х в регистр 1 чисел, равная 4, am- количество разрядов в регистре 1, равная 3.

В общем случае, если , то по кольцу сдвиг начального кода происходит влево на разрядов регистра 1. Если , то сдвиг по кольцу происходит вправо на разрядов

регистра 1. Если , то . и сдвига по кольцу нег, т.е. из одних и тех же .ячеек 2 памяти регистра 1 считьшаются одни и те же числа.

0 Если выбирают число 10010010 по адресу, по которому возбуждается одна из адресных шин Ю, то к этой адресной шине подсоединяют по одному входу элементов ИЛИ 5. -1 и ИЛИ б. 1

5 (фиг. 1).

Для выборки числа 01100100 по соответствующей адресной шине 10 к этой шине подключают по одному входу элементов ИЛИ 5.2 и ШШ 6.3 (фиг. 1).

0 Для выборки числа 11010110 по соответствующей адресной шине 10 к этой шине подключают по одному входу элементов ИЛИ 5.4 и ИЛИ 6.6 (фиг. 1). В некоторых случаях информацию

5 представляют в виде нескольких кодов ориентированных циклов. Тогда регистр 1 сдвига состоит из нескольких независимых регистров сдвига. Если в предлагаемом устройстве хранить числа большой разрядности, то формируют эти числа более чем из двух п-разрядных чисел, записанных в регистре 1 сдвига. Для этого в устройство дополнительно вводят более, чем одну группу элементов И, соответствующее количество элементов ИЛИ, триггера и связи между ними. В предлагаемом устройстве, содержа-ю тов щем регистр 1 сдвига с ячейками 2 п мяти, хранится (2m) 2п разрядных ч сел (количество перестановок с повторениями из 2гп элементов по два). Для хранения такого объема информадни требуемое количество- элементов (без учета счетчика и триггера равно 4т + 4т + I Sm +i . ГДЕ 4ifn - количество элементов ИЛИ 5 и ИЛИ 6; 4т- количество элементов-И 3 и И 4; 1 - элемент ИЛИ 7. Общее количество входов у этих элементов равно 2(т)+ 34т+ 4т 8т 16т. В известном устройстве для хранения такого объема информации требуется (2т) ячеек памяти, а требуемо количество элементов равно (2гт) +1 1, (3) где (2iTi) - количество элементов И; 1 - схема ИЛИ. Общее количество входов у этих элементов равно . . 2 (2т)Ч (2т) 12т (4) Сравнивая формулы (l) и (З), (2) и (4) видно , что предлагаемое устрой ство дает выигрыш как в количестве элементов, так и в количестве входов у этих элементов, причем выигрыш по элементам получаем уже при , и по входам при . Как видно из сравнения известного устройства с предлагаемым устройство последнее имеет выигрыш в количестве оборудования, причем наибольший вьшгрыш получается в количестве элементов памяти, так как для хранения 84 3 (2т) К 2п бит требуется только m элементов памяти. . Формула изобретения Постоянное запоминающее устройство, содержащее регистр сдвига, информационные входы которого соединены с соответствующими шинами логических нуля и единицы, а выходы - с информационными входами основных элеменИ, выходы которых соединены с одними входами элемента ИЛИ, и шины управления Обращения, тактовая и шина установки в исходное состояние, к которым подключены соответству1сяцие входы регистра сдвига, отличающееся тем, что, с целью упрощения устройства, оно содержит дополнительные элементы И, триггер, двоичный счетчик и группы .элементов ИЛИ, входы которых подключены к адресным шинам, выходы элементов ИЛИ одной группы соединены с соответствующими управляющими входами основных элементов И, а выходы элементов ИЛИ другой группы соединены с соответствующими управляющими входами дополнительных элементов И, информационные входы которых соединены с выходами разрядов регистра сдвига, а выходы подключены к соответствую1цим входам элемента ИЛИ, входы двоичного счетчика -подключеИы к шинам управления 0бращвние, тактсгвой и к шине установки в исходное состояние, которая подключена к нулевому входу триггера, нулевой выход которого подключен к первому управляющемувходу основных элементов И, а единичный выход к первому управляющему входу дополнительных элементов И, единичный вход триггера соединен с выходом двоичного счетчика. Источники информации, принятые во-внимание при экспертизе 1.Авторское свидетельство СССР №491157, кл. G 11 С 17/00, 05.11.75. 2.Авторское свидетельство СССР № 565326, кл. G II С 17/00, 15.07.77 (прототип).

W СЧ1

0000

nil

аг.г

Авторы

Даты

1981-07-23—Публикация

1979-04-13—Подача