Известны цифровые вычислительные машины с автоматическим программированием и микропрограммным устройством управления, содержащие устройство ввода-вывода, арифметическое устройство параллельного типа, оперативное запоминающее устройство, одностороннее запоминающее устройство.

Предлагаемая цифровая вычислительная машина с автоматическим программированием и микропрограммным устройством управления отличается тем, что в ней генератор тактовых импульсов соединен через схему задержки с цепью сброса на нуль регистра адреса долговременного запоминающего устройства и с первыми входами вентилей разрешения микрокоманд. Вторые входы этих вентилей подключены соответственно к схеме «ИЛИ» анализа наличия микрокоманд или чисел и схеме «И» анализа наличия константы в микрокоманде, подключенным к регистру адреса долговременного запоминающего устройства, а выходы вентилей разрешения микрокоманд через схему «ИЛИ» подсоединены к формирователю разрешения микрокоманд, подключенному ко входу вентилей элементарных операций, которые подсоединены к выходам долговременного запоминающего устройства и к вентилю регистра адреса долговременного запоминающего устройства, подключенного также к регистру адреса оперативного запоминающего устройства.

Выходы устройства управления через вентиль элементарных операций подсоединены к блоку фиксированных ячеек, блоку местного управления устройством ввода-вывода, а также к формирователю разрешения адресов микрокоманд, выходу которого подсоединены ко входам вентилей регистра адреса долговременного запоминающего устройства, вторые входы которых подсоединены соответственно через линию задержки к ячейке долговременного запоминающего устройства хранения адреса следующей микрокоманды и к регистру команд.

Регистр команд подсоединен также ко входу первого вентиля регистра адреса оперативного запоминающего устройства, а выход линии задержки соединен также со входом второго вентиля регистра адреса оперативного запоминающего устройства.

Выходы вентилей регистра адреса долговременного запоминающего устройства подсоединены к регистру адреса долговременного запоминающего устройства, который подключен через дешифратор к накопителю долговременного запоминающего устройства; выходы формирователей разрешения адресов микрокоманд подсоединены ко вторым входам вентилей регистра адреса оперативного запоминающего устройства. Накопитель оперативного запоминающего устройства через сумматор подключен к регистру команд, а также к регистру внешнего устройства, который также подключен к регистру команд; блок фиксированных ячеек подключен через цепи считывания и регенерации оперативного запоминающего устройства к сумматору.

Выходы вентилей признаков условного перехода как сумматора, так и регистра команд подсоединены через схему «ИЛИ» к первому разряду регистра адреса долговременного запоминающего устройства.

Это позволяет расширить круг решаемых задач, использовать переменную систему команд, увеличить надежность, быстродействие, облегчает эксплуатацию, наладку при значительной экономии оборудования машины, а также позволяет использовать произвольные коды внешних устройств.

Другим отличием цифровой вычислительной машины является то, что для увеличения разрядности микропрограммной части долговременного запоминающего устройства в нем две однотипные ячейки накопителя соединены параллельно.

Предлагаемая вычислительная машина также отличается тем, что, с целью упрощения устройства микропрограммного управления, в ней формирователь разрешения микрокоманд и формирователь разрешения адресов микрокоманд выполнены на одновибраторах с двумя выходами для импульсов, фаза которых различается на π.

Другим отличием цифровой вычислительной машины является то, что для сокращения оборудования, унификации электрической схемы ввода и вывода на печать со схемой ввода с трансмиттера и вывода на перфорацию, в ней разделенные контакты одного телеграфного аппарата соединены параллельно с аналогичными контактами другого аппарата и подключены к регистру внешних устройств через реверсивно работающие ключи переключения телеграфных аппаратов из режима приема в режим передачи.

Следующим отличием предлагаемой цифровой вычислительной машины является то, что для использования телеграфных аппаратов для первичной подготовки и проверки вводимой и выводимой информации, а также индивидуальной наладки при независимой от машины работе внешних устройств в ней выходы триггера, счетный вход которого подсоединен к стартстопным контактам телеграфных аппаратов, подключены через клавишу «автономный» к реверсивно работающим ключам.

Вычислительная машина также отличается тем, что для улучшения доступа к накопителю оперативного запоминающего устройства адресная часть расположена на платах с петлями, укрепленными по бокам куба накопителя.

Другим отличием цифровой вычислительной машины является то, что для увеличения объема библиотеки программ решения задач, изменения микропрограмм ячейки накопителя долговременного запоминающего устройства выполнены конструктивно съемными взаимозаменяемыми.

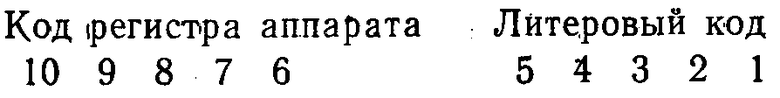

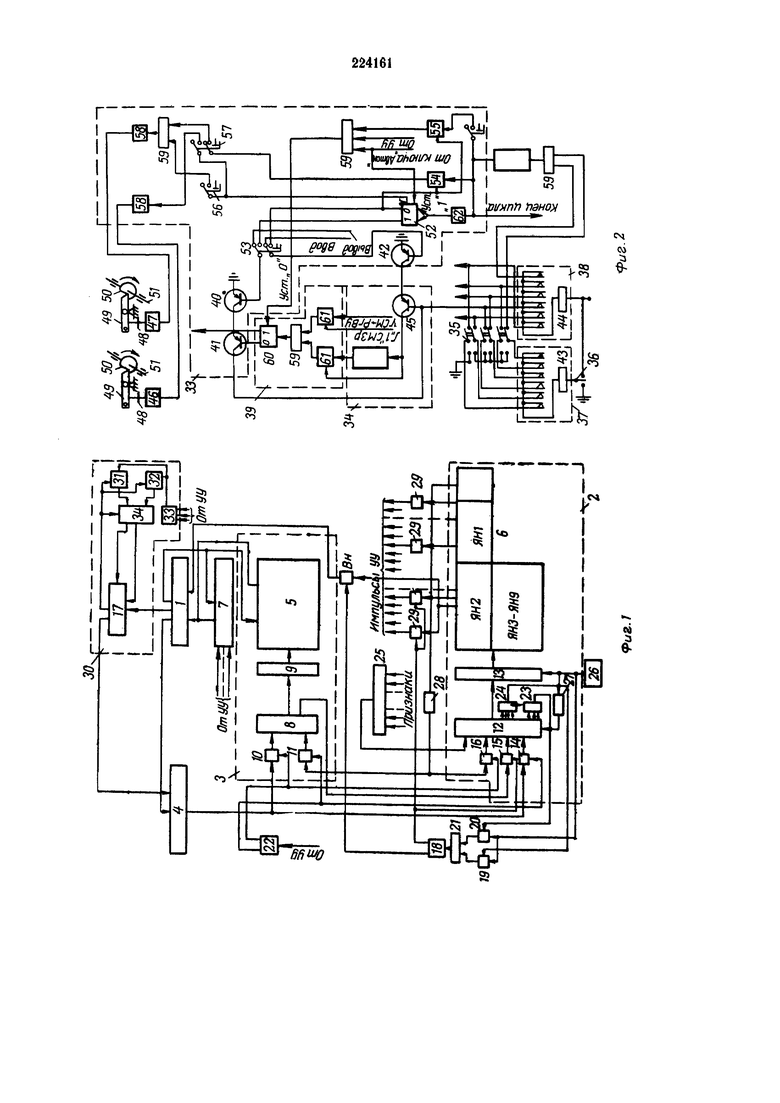

На фиг. 1 представлена структурная схема предлагаемой вычислительной машины; на фиг. 2 - структурная схема устройства ввода-вывода.

В состав предлагаемой машины входят: сумматор 1 параллельного действия со сквозным переносом, предназначенный для выполнения арифметических и логических операций над числами и командами.

Сумматор 1 также служит регистром числа долговременного запоминающего устройства 2 и оперативного запоминающего устройства 3. Сумматор содержит 37 разрядов, из них 34 разряда представляют дробную часть числа, 35-й разряд - целую часть числа, 36-й разряд отведен для знака числа. Дополнительный разряд сумматора предусмотрен для округления результата, для анализа множителя при операции умножения. Выход сумматора связан с регистром 4 команд и накопителем 5 оперативного запоминающего устройства, а вход - с ячейками ЯН2, ЯН3-2Н9 накопителя 6 долговременного запоминающего устройства.

Блок фиксированных ячеек 7 выполняет функции регистров первого и второго числа и используется для запоминания различных величин во время выполнения операций.

Фиксированные ячейки используют те же цепи считывания и регенерации оперативного запоминающего устройства 3, при этом чтение и запись с фиксированных ячеек осуществляется непосредственными связями с устройства управления (УУ).

Оперативное запоминающее устройство 3 (1024 двоичных, 36 разрядных слов) предназначено для запоминания и выдачи переменной части программ и промежуточных данных.

В машине используется оперативное запоминающее устройство типа Z. При чтении информации из какой-нибудь ячейки оперативного запоминающего устройства 3 содержимое данной ячейки стирается и автоматически регенерируется. В его состав входит накопитель 5, регистр 8 адреса, импульсно-потенциальный дешифратор 9.

Накопитель 5 выполнен в виде куба, собранного из восьми кассет числовой части и четырех плат адресной части, расположенных по бокам куба так, что к ним возможен двусторонний доступ.

Регистр 8 содержит 11 двоичных разрядов. Помимо основного назначения, этот регистр также используется для временного хранения адреса следующей микрокоманды и связан с регистром 4 через вентили 10, а также через вентиль 11 с ячейкой ЯН1 накопителя 6, в которой хранятся адреса микрокоманд.

Долговременное запоминающее устройство 2 предназначено для постоянного хранения и выдачи встроенных в машину программ, а также микропрограмм машинных операций и микропрограмм тестов. Объем хранимой информации - 16384 слова. В первых 2048 адресах хранятся микропрограммы. Длина слова равна 72 разрядам, что достигается одновременным чтением двух параллельно соединенных ячеек накопителей емкостью 2048 36-разрядных слов каждая. Адреса с 2049 по 16384, в которых хранятся 36-разрядные слова, находятся в остальных семи ячейках накопителя.

Все ячейки накопителя съемные. Запоминающее устройство 2 содержит ячейки ЯН1-ЯН9 накопителя 6, регистр 12 адреса и дешифратор 13. Входы регистра 12 адреса связаны с регистром 4 через вентиль 14, с регистром 8 через вентиль 15 и с ячейкой ЯН1 накопителя 6, обеспечивающей чтение в регистр 12 адреса следующей микрокоманды, через вентиль 16.

Регистр 4 предназначен для хранения команд. Кроме этого в нем хранятся промежуточные величины во время выполнения сложных машинных операций.

Вход регистра 4 связан с сумматором 1 и регистром 17 внешних устройств.

Устройство управления содержит одновибратор 18 разрешения микрокоманд с вентилями 19 и 20, подключенными ко входу одновибратора 18 через схему «ИЛИ» 21; одновибратор 22 разрешения адресов микрокоманд, запускаемый импульсом устройства управления, схему «ИЛИ» 23 анализа старших разрядов регистра 12, схему «И» 24 анализа старших разрядов адреса следующей микрокоманды, схему 25 «ИЛИ», собирающую все вырабатываемые в машине признаки; генератор 26, схемы 27 и 28 задержек.

Устройство управления обеспечивает чтение информации из долговременного запоминающего устройства 2 в виде чисел или же в виде микрокоманд, при этом микрокоманды, как правило, состоят из набора элементарных операций и адреса следующей микрокоманды; нормальное функционирование адреса следующей микрокоманды, поступающего из ячейки ЯН1 накопителя 6 в регистр 12 непосредственно либо через регистр 8; выполнение условных переходов в микропрограммах в зависимости от вырабатываемых в машине признаков.

В устройство управления также входят блок вентилей 29, обеспечивающий соответствующее распределение всех элементарных операций.

Внешнее устройство 30, содержащее стандартные телеграфные аппараты 31, 32 (соответственно РТА-50-2М и СТА-2М). регистр 17 внешних устройств, местное устройство управления 33, цепи 34 формирования сигналов; полученных от телеграфных аппаратов 31, 32. Аппарат РТА-50-2М предназначен для ввода и вывода буквенно-цифровой информации, аппарат СТА-2М - для ввода информации от перфорированной ленты и вывода информации на перфорацию ленты. Аппарат СТА-2М позволяет вводить информацию при помощи Клавиатуры -. аналогично РТА-50-2М, а также с перфоленты. Для независимой от машины работы внешнего устройства предусмотрен автономный режим. В этом режиме внешнее устройство 30 может быть использовано для подготовки и проверки перфоленты.

Регистр 17 по входу связан с пятью младшими разрядами сумматора 1 и контактами передатчиков обоих аппаратов.

Машина работает следующим образом. Импульсы генератора 26 образуют импульсы чтения долговременного запоминающего устройства 2. После определенной задержки, образуемой схемой задержки 27, теми же импульсами генератора 26 очищается содержимое регистра 12 адреса.

Если будет читаться микрокоманда, что может быть в случае, когда в регистре 12 находится адрес меньше 2048, то к приходу следующего импульса чтения долговременного запоминающего устройства 2 выполняются те элементарные операции, которые имеются в данной микрокоманде, а адрес следующей микрокоманды, определяемый считанной микрокомандой, через определенную задержку благодаря схеме задержки 28 поступит в очищенный регистр 12. Задержка адреса следующей микрокоманды определяется временем переходных процессов, вызванных установкой на нуль регистра 12. Указанный способ предоставления адреса следующей микрокоманды позволяет осуществить безусловные переходы к любой из 2048 микрокоманд.

Во многих микропрограммах необходимы условные переходы. Условные переходы выполняются микрокомандами, содержащими элементарные операции, которые опрашивают схемы, вырабатывающие соответствующие признаки. Все опрашиваемые признаки подают на одну схему «ИЛИ» 25, выход которой поступает на единичный вход первого разряда регистра 12. Таким образом, если выполняется команда, в которой имеется элементарная операция, опрашивающая какой-либо признак, то наряду с поступлением адреса следующей микрокоманды в регистр 12, причем в этом случае берется четный адрес, в младший разряд регистра 12 поступает единица, если соответствующий признак выработан. Если признак не выработан, то адрес следующей микрокоманды поступит в регистр 12 без изменений.

Осуществление безусловных и условных переходов позволило в машине весьма просто организовать микропрограмму любой сложности.

Для выполнения какой-либо операции адрес первой микрокоманды образуется путем; посылки кода соответствующей операции в регистр 12. Все развилки в микропрограммах осуществлены этим способом.

Прерывание микропрограмм при чтении информации с программной части долговременного запоминающего устройства, т.е. с ячеек ЯН3-ЯН9 накопителя 6, осуществляется следующим образом: в соответствующей микрокоманде вырабатывается импульс устройства управления, т.е. соответствующая элементарная операция, которая запускает одновибратор 22 разрешений адресов Микрокоманд, вырабатывающий разрешения для передач адресной части регистра 4 в регистр 12 и адреса следующей микрокоманды в регистр 8.

К приходу следующего импульса генератора 26 при помощи анализа трех старших разрядов регистра 12 с помощью схемы «ИЛИ» 23 образуется признак, обеспечивающий запуск одновибратора разрешения микрокоманд 18, импульсами генератора 26, одновибратор, запускаясь, пропускает импульсы числа с запоминающего устройства 2 в сумматор 1, а также разрешает передачу адреса следующей микрокоманды из регистра 8 в регистр 12. Схема «И» 24, анализирующая 8-11-е разряды регистра 12, образует признак, позволяющий считывать константы ячейки ЯН2 накопителя 6, начиная с 1920-го адреса, а не элементарные операции. Это осуществляется следующим образом. Импульсы генератора 26, опрашивая данный признак, запускают одновибратор 18, разрешающий поступление импульсов г накопителя В сумматор. Импульсы, считываемые с первой ячейки накопителя, образуют элементарные операции и адрес следующей микрокоманды. Таким образом, если в 8-11-м разрядах регистра 12 записаны единицы, то имеется возможность читать микрокоманду с константой, засылаемой в сумматор. Эти константы используются во многих микропрограммах, например для образования дополнительного кода чисел.

В машине для обнаружения неисправностей, помимо программных тестов, имеются также микропрограммные тесты. Соответствующие команды помещены в ячейках ЯН1, ЯН2 накопителя 6.

Использование микрокоманд с константами и осуществление условных переходов позволяет составлять микропрограммные тесты следующим образом: при помощи соответствующей микрокоманды заносится «1» в проверяемый элемент последовательно по каждому входу и каждый раз проверяется состояние данного элемента при помощи микрокоманд условных переходов. При выявлении неисправности в какой-нибудь входной цепи при помощи элементарных операций вывода печатается обозначение данной неисправной цепи.

Аналогично проверяются выходные цепи каждого элемента: при помощи соответствующих элементарных операций выходной сигнал данного элемента подается на входы последующих элементов; при обнаружении неисправности в выходной цепи при помощи элементарных операций вывода печатается обозначение данной неисправной цепи. Примером осуществления данного способа являются тесты: «проверка цепей внешних устройств», тест «проверка фиксированных ячеек машины» и тест «дождик».

1. Тест проверки. цепей внешнего устройства. Проверка осуществляется следующим образом: на печатающей машине оператором последовательно печатаются все символы, при этом код каждого символа попадает в регистр внешних устройств, а затем при помощи соответствующей микрокоманды в регистр команд и далее в сумматор. Этим проверяются в данной машине цепи ввода. Следующая микрокоманда передает из сумматора код в очищенный предыдущими микрокомандами регистр внешних устройств. Далее следует микрокоманда печати содержимого регистра внешних устройств. Если все цепи ввода и вывода работают нормально, то вводимый и выводимый символы совпадают. Если имеются неисправности в указанных цепях, то при выводе печатается символ, отличный от вводимого символа.

2. Тест проверки фиксированных ячеек машины. Проверка осуществляется следующим образом: из долговременного запоминающего устройства в сумматоре читается константа, которая записывается в проверяемую фиксированную ячейку блока фиксированных ячеек. Затем из данной фиксированной ячейки считывается записанный код, который поступает на счетные входы триггеров сумматора и складывается «по модулю 2» с тем же кодом, который сохранился в сумматоре после записи. Затем производится проверка содержимого сумматора на нуль. Если в сумматоре не получился нуль, то выводится на печать номер проверяемой ячейки с помощью нескольких микрокоманд. Если содержимое сумматора равно нулю, то переходят к проверке следующих фиксированных ячеек аналогичным образом. После проверки последней фиксированной ячейки текст повторяется новой константой.

3. Тест «дождик». Для проверки разрядности оперативного запоминающего устройства постоянным кодом вначале выполняется микрокоманда с константой, засылаемой в сумматор. Далее несколькими микрокомандами эта константа записывается по всем адресам оперативного запоминающего устройства, затем производится последовательное чтение всех адресов оперативного запоминающего устройства, причем номера адресов фиксируются в счетчике. В качестве счетчика используется счетчик адресов команд. Подсчет адресов осуществляется микрокомандой, в которой имеется элементарная операция «прибавление единицы в счетчик адресов команд». Каждый считанный код, поступай на счетные входы триггеров сумматора, складывается «по модулю 2» с содержимым сумматора, и результат сложения автоматически записывается по данному адресу оперативного запоминающего устройства.

Таким образом, при правильной работе оперативного запоминающего устройства в сумматоре в результате каждого чтения или остается считанный код, или образуется код нулей.

Правильность считанного кода контролируется следующим образом. После каждого чтения производится проверка содержимого сумматора на нуль с помощью микрокоманды условного перехода. Если в сумматоре нуль, то считанный код считается правильным и производится чтение по следующему адресу; если содержимое сумматора не нуль, то с ним складывается «по модулю 2» та же константа, образованная очередной микрокомандой, затем снова проверяется на нуль содержимое сумматора с помощью микрокоманды условного перехода. Если содержимое сумматора равно нулю, то считанный из оперативного запоминающего устройства код правильный и производится чтение по следующему адресу; если содержимое сумматора не нуль, то считанный из оперативного запоминающего устройства код неправильный и машина переходит к микрокомандам, которые выводят на печать содержимое счетчика адреса команд в восьмеричной системе счисления. Далее выводится содержимое сумматора также в восьмеричной системе счисления.

По первому числу определяется номер адреса оперативного запоминающего устройства, с которого произошло неправильное считывание, а по второму числу определяется номер неисправного разряда по данному адресу оперативного запоминающего устройства.

Внешнее устройство машины обеспечивает следующие режимы работы:

1. При работе с машиной: а) ввод алфавитно-цифровой информации с клавиатуры с печатью на рулонной бумаге; б) ввод информации с перфоленты в пятизначном двоичном коде; в) вывод информации из машины на печать на рулонную бумагу; г) вывод информации из машины на перфорацию в пятизначном двоичном коде.

2. В автономном режиме при одновременной независимой работе машины: д) печать на рулонной бумаге с клавиатуры; е) печать на рулонной бумаге с клавиатуры и перфорация на перфоленте в пятизначном двоичном коде: ж) печать на рулонной бумаге с перфорированной ленты; з) реперфорация перфорированной ленты; и) перфорация с клавиатуры в пятизначном двоичном коде; к) прием информации с отдаленного объекта через линию связи путем перфорации на аппарате 32 (СТА-2М); л) передача информации с перфорированной ленты в отдаленный объект через линию связи.

Режимы по пунктам з, и, к, л осуществляются путем переключения тумблеров 35 в положение «автономный», что соответствует их левому положению на схеме; в режимах по пунктам к, л необходимо также переключить тумблер 36 в положение «отдаленный объект», что соответствует левому положению на схеме.

В этих режимах аппарат 32 работает индивидуально в режиме телеграфного аппарата.

Связь с отдаленным объектом двусторонняя, а номинальный ток катушки передатчика аппарата обеспечивается со стороны объекта.

Использование в качестве вводного и выводного устройства машины аппаратов 32. (СТА-2М) и 31 (РТА-50-2М) позволило унифицировать электрическую схему ввода и вывода на печать со схемой ввода с трансмиттера и вывода на перфорацию путем жесткого параллельного соединения выходных кодовых каналов обоих аппаратов.

С целью сокращения оборудования и повышения надежности работы аппаратов 31, 32 контакты 37, 38 обоих аппаратов разделены и заменены вольфрамовыми.

Замена серебряных контактов на искроустойчивые вольфрамовые позволила резко повысить срок службы и устранила необходимость периодической чистки контактов.

Разделение контактов аппаратов 31, 32 дает возможность сократить оборудование, необходимое для преобразования последовательного представления кода - в параллельный при вводе и параллельного представления - в последовательный при выводе.

Таким образом, ввод символа в машину будет означать передачу 5-разрядного кода по пяти отдельным каналам 34, 39 (в фиг. 2 показан третий канал) в регистр 17 и использование шестого канала как признака конца одного цикла работы аппарата, а вывод символа из машины будет означать последовательный опрос через ключ 40 и управляемый триод 41 всех пяти разрядов регистра 17 контактами 37, 38 передатчиков. Следовательно, печать, а также образование кодов при вводе информации осуществляется с помощью контактов 37, 38 передатчиков аппаратов 31 или 32.

Режим приема или передачи обеспечивается ключами 40 и 42, которые при работе внешнего устройства 30 с машиной управляются кодом операции команды. При коде «ввод» открыт ключ 42 и закрыт ключ 40, тем самым обеспечивается ввод информации в машину как с аппарата 31, так и с аппарата 32 (по желанию оператора).

При коде «вывод» открыт ключ 40 и закрыт ключ 42 и обеспечивается режим вывода информации как на печать, так и на перфорацию.

Открытое состояние ключа 42 обеспечивает замыкание цепи питания электромагнита 43 или 44 передатчика через управляемый триод 45 и ключ 42 при последовательном замыкании контактов аппарата в зависимости от вводимого символа.

Открытое состояние ключа 40 обеспечивает замыкание цепи питания электромагнита 43 или 44 передатчика через управляемый триод 41 и ключ 40 путем последовательного опроса контактами 37, 38 содержимого регистра 17.

Запуск аппаратов в один цикл при выводе осуществляется возбуждением электромагнитов 46 или 47, якоря которых 48 притягивают рычаги 49, освобождают кулачки 50, затормаживающие вал 51 передающего механизма аппаратов.

С целью упрощения и ускорения процесса анализа опознавания вводимого знака, в машине осуществлено преобразование внешнего знакового кода на внутренний с определенной группировкой: число, степень, индекс, буква и т.д. Все внутренние коды знаков представляют последовательность 36-разрядных чисел. Группы отличаются друг от друга наличием единицы в определенном разряде.

Декодирование осуществляется следующим образом: переданные в машину внешние коды знаков являются адресами соответствующих внутренних кодов, записанных в долговременном запоминающем устройстве 2 по указанным группам.

В машине после ввода какого-нибудь знака возможно обращение к внешнему устройству для вывода на печать или на перфорацию того или иного знака. Этот знак может оказаться в любом из трех имеющихся на аппаратах 31 и 32 регистров, поэтому становится необходимым до печати каждого знака выводить на печать код регистра аппарата для данного знака. Это приводит к излишнему обращению к аппаратам 31, 32, так как в большинстве случаев регистр аппарата уже находится в положении, соответствующем выводимому регистру.

Например, для печати числового значения, состоящего из десяти десятичных чисел, машине необходимо осуществить 20 обращений к внешнему устройству, из них 10 для числовых кодов и 10 для регистровых. Из последних 10 обращений 9 (возможно и 10) не меняют положения регистра.

Поэтому в машине положение регистра аппарата запоминается в одной из фиксированных ячеек блока фиксированных ячеек 7. При вводе информации каждый раз, когда вводится код какого-нибудь регистра аппарата, он запоминается в одной из фиксированных ячеек и тем самым фиксируется положение регистра аппарата. При выводе информации на печать или на перфорацию код выводимого знака передается в сумматор в следующем виде:

Для печати представленного в сумматоре знака осуществляется сравнение содержимого сумматора (6-10-й разряды) с записанным в фиксированной ячейке кодом регистра аппарата. При совпадении этих кодов на печать выводится только литеровый код, находящийся в 1-5-м разрядах сумматора.

При несовпадении на печать выводится последовательно код регистра аппарата с одновременной записью в указанной фиксированной ячейке, а затем литеровый код.

При работе внешних устройств в автономном режиме управление осуществляется триггером 52 управления автономного режима.

Триггер 52 работает по счетному входу от импульсов, полученных от шестого канала обоих аппаратов. При нажатии клавиши 53 «автономный» триггер 52 устанавливается в состояние «1». При этом ключ 49 отпирается, а ключ 40 запирается и на потенциальные входы вентилей 54, 55 поступает запирающий потенциал.

Это состояние соответствует режиму передачи для обоих аппаратов 31, 32.

Нулевое состояние триггера 52 переключает ключи 40 и 42 и обеспечивает подачу на потенциальные входы вентилей 54, 55 разрешающего потенциала. Это состояние соответствует режиму приема с обоих аппаратов.

При переходе триггера 52 из состояния «1» в состояние «0» на дифференцирующем выходе его образуется импульс, который осуществляет запуск одного из аппаратов. 31, 32 в зависимости от выбранного оператором режима с помощью клавиш «печать с трансмиттера» 56 и «перфорация» 57.

На фиг. 2 приведены также одновибраторы 58, схема «ИЛИ» 59, триггер 60, вентили 61 и схема задержки 62, выполняющие вспомогательные функции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограмммное устройство управления для цифровой вычислительной машины | 1967 |

|

SU482743A2 |

| УСТРОЙСТВО ДЛЯ МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1968 |

|

SU217724A1 |

| УСТРОЙСТВО для МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ | 1968 |

|

SU217066A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для управления цифровой вычислительной машиной | 1974 |

|

SU520591A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Мультипроцессорная система | 1983 |

|

SU1156088A1 |

1. Цифровая вычислительная машина с автоматическим программированием и микропрограммным устройством управления, содержащая устройство ввода-вывода, арифметическое устройство параллельного типа, оперативное запоминающее устройство, одностороннее запоминающее устройство, отличающаяся тем, что, с целью расширения круга решаемых задач, использования переменной системы команд, увеличения надежности, быстродействия, облегчения эксплуатации, наладки при значительной экономии оборудования машины, а также использования произвольных кодов внешних устройств, в ней генератор тактовых импульсов соединен через схему задержки с цепью сброса на нуль регистра адреса долговременного запоминающего устройства и с первыми входами вентилей разрешения микрокоманд, вторые входы которых подключены соответственно к схеме «ИЛИ» анализа наличия микрокоманд или чисел и схеме «И» анализа наличия константы в микрокоманде, подключенным к регистру адреса долговременного запоминающего устройства, а выходы вентилей разрешения микрокоманд через схему «ИЛИ» подсоединены к формирователю разрешения микрокоманд, подключенному ко входу вентилей элементарных операций, которые подсоединены к выходам долговременного запоминающего устройства и к вентилю регистра адреса долговременного запоминающего устройства, подключенного также к регистру адреса оперативного запоминающего устройства; выходы устройства управления через вентили элементарных операций подсоединены к блоку фиксированных ячеек, блоку местного управления устройством ввода-вывода, а также к формирователю разрешения адресов микрокоманд, выходы которого подсоединены ко входам вентилей регистра адреса долговременного запоминающего устройства, вторые входы которых подсоединены соответственно через линию задержки к ячейке долговременного запоминающего устройства хранения адреса следующей микрокоманды и к регистру команд, подсоединенному также ко входу первого вентиля регистра адреса оперативного запоминающего устройства, а выход линии задержки соединен также со входом второго вентиля регистра адреса оперативного запоминающего устройства; выходы вентилей регистра адреса долговременного запоминающего устройства подсоединены к регистру адреса долговременного запоминающего устройства, который подключен через дешифратор к накопителю долговременного запоминающего устройства; выходы формирователей разрешения адресов микрокоманд подсоединены ко вторым входам вентилей регистра адреса оперативного запоминающего устройства; накопитель оперативного запоминающего устройства через сумматор подключен к регистру команд, а также к регистру внешнего устройства, который также подключен к регистру команд; блок фиксированных ячеек подключен через цепи считывания и регенерации оперативного запоминающего устройства к сумматору; выходы вентилей признаков условного перехода как сумматора, так и регистра команд подсоединены через схему «ИЛИ» к первому разряду регистра адреса долговременного запоминающего устройства.

2. Машина по п. 1, отличающаяся тем, что, с целью увеличения разрядности микропрограммной части долговременного запоминающего устройства, в нем две однотипные ячейки накопителя соединены параллельно.

3. Вычислительная машина по п. 1, отличающаяся тем, что, с целью упрощения устройства микропрограммного управления, в ней формирователь разрешения микрокоманд и формирователь разрешения адресов микрокоманд выполнены на одновибраторах с двумя выходами для импульсов, фаза которых различается на π.

4. Машина по п. 1, отличающаяся тем, что, с целью сокращения оборудования, унификации электрической схемы ввода и вывода на печать со схемой ввода с трансмиттера и вывода на перфорацию, в ней разделенные контакты одного телеграфного аппарата соединены параллельно с аналогичными контактами другого аппарата и подключены к регистру внешних устройств через реверсивно работающие ключи переключения телеграфных аппаратов из режима приема в режим передачи.

5. Машина по п. 1, отличающаяся тем, что, с целью использования телеграфных аппаратов для первичной подготовки и проверки вводимой и выводимой информации, а также индивидуальной наладки при независимой от машины работе внешних устройств, в ней выходы триггера, счетный вход которого подсоединен к стартстопным контактам телеграфных аппаратов, подключены через клавишу «автономный» к реверсивно работающим ключам.

6. Машина по п. 1, отличающаяся тем, что, с целью улучшения доступа к накопителю оперативного запоминающего устройства, адресная часть расположена на платах с петлями, укрепленными по бокам куба накопителя.

7. Машина по п. 1, отличающаяся тем, что, с целью увеличения объема библиотеки программ решения задач, изменения микропрограмм, ячейки накопителя долговременного запоминающего устройства выполнены конструктивно съемными и взаимозаменяемыми.

Авторы

Даты

1968-11-26—Публикация

1964-11-09—Подача