Изобретение относится к автоматике, телемеханике и вычислительной технике.

Известны цифровые широтно-импульсные модуляторы, содержащие генератор тактовых импульсов, кольцевой регистр сдвига, блоки синхронизации, триггерные счетчики, блок уиравления, схемы «И, аналого-цифровые преобразователи и суммирующий усилитель.

В предлагаемом модуляторе, с целью повыЩения точности работы, получения выходной характеристики с перемениым шагом квантования по амплитуде и ограничения но максимуму, выходы старших разрядов счетчиков через стробирующие ячейки подключены ко входу кольцевого и реверсивного регистров, выходы которых подключены ко входам трех управляющих триггеров и двух триггеров защиты, выходы которых соединены со входом суммирующего усилителя.

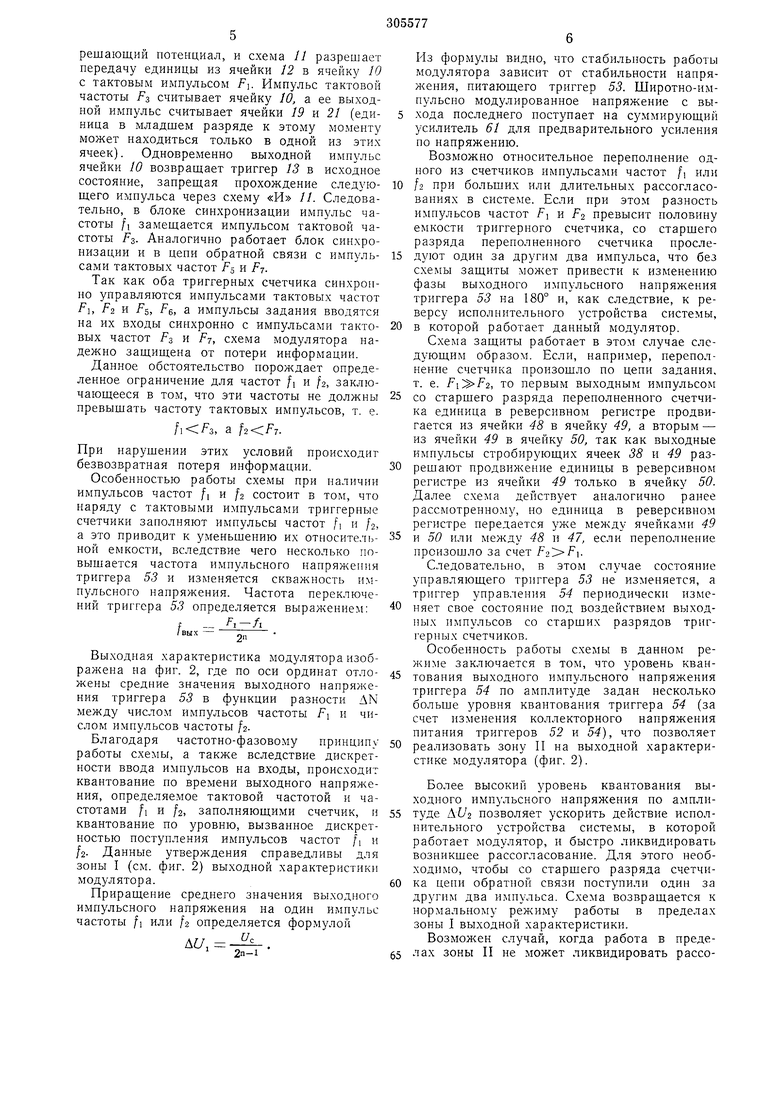

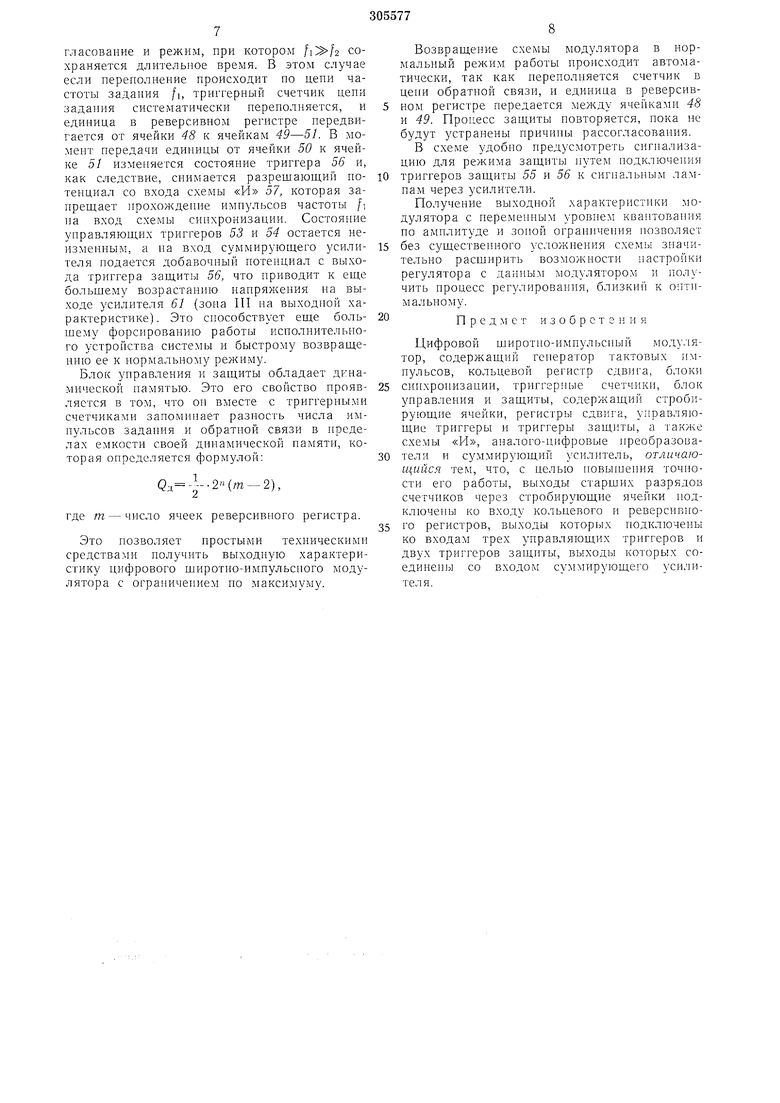

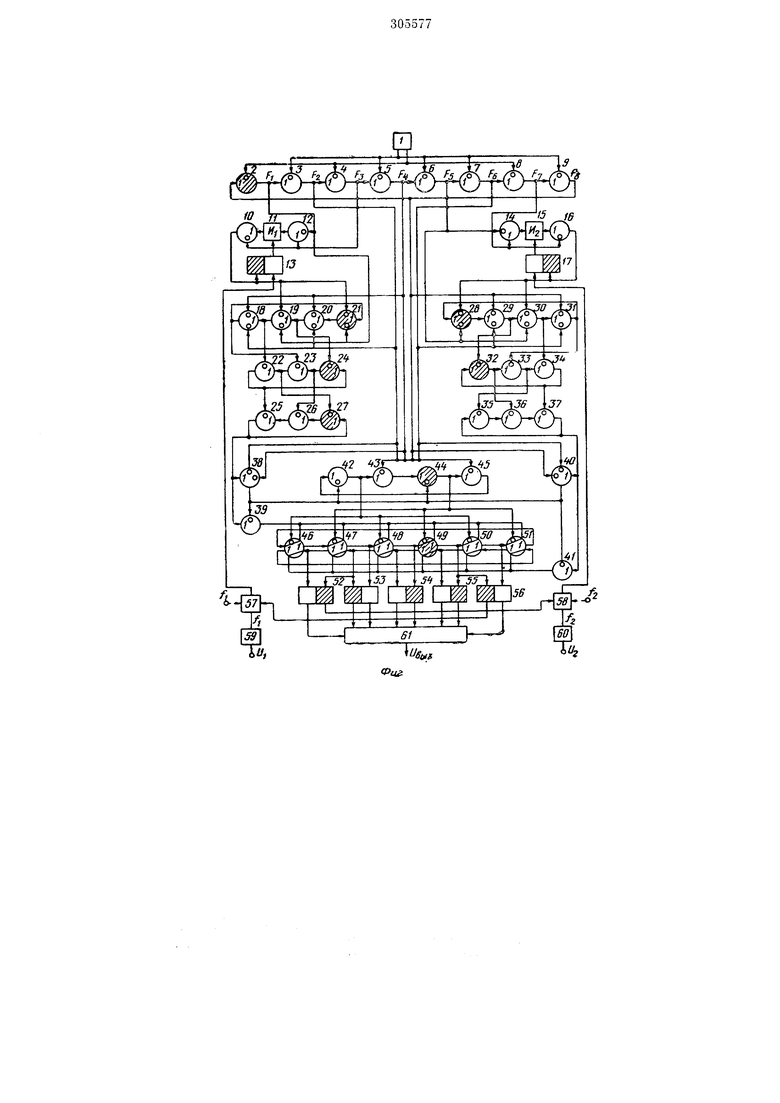

На фиг. 1 изображена развернутая функциональная схема цифрового шнротпо-имнульсного модулятора; на фиг. 2 - его выходная характеристика.

В состав модулятора входят: генератор / незатухающих колебаний с формирователем тактов, кольцевой регистр сдвига иа восьми ячейках 2-9, позволяющий получать восемь однополярных импульсов тока из каждых четырех периодов колебаний генератора /; два блока синхронизации на элементах 10-

13 в цени задання и 14-17 в цепи обратной связи; два нереверсивных триггерных счетчика на ячейках 18-27 и 28-37 соответственно, играющих роль интегрнрующего и делительного устройств; четыре стробирующие ячейки 38-41 для уиравлечия работой кольцевого регистра па ячейках 42-45 и реверсивного регистра на ячейках 46-51 блока управления и защиты; трп выходных

управляющих феррит-транзисторных триггера 52-54, феррит-транзисторные триггеры защиты 55 и 56, которые вместе со схемами «И 57 и 58 защищают исполнительное устройство от реверса при больших или длительных рассогласоваинях; два аналого-цифровых нреобразователя 59 60 в цепи задания и в цепи обратной связи и суммирующий усилитель 61. Перед началом работы все элементы схемы устанавливаются специальным импульсом сброса в состояние, нзображенное на фиг. 1, где заштрихованной половине триггера соответствует высокий отрицательный нотенциал, а заштрихованной ячейке - нервоначальная установка ее в единичное состояние.

Работу модулятора целесообразно рассматривать в трех режимах:

1 - при отсутствии импульсов задания /i

2- при наличии импульсов задания и обратной связи;

3- в режиме защиты.

При отсутствии импульсов задания и обратной связи схема работает следующим образом; генератор импульсов тактовой частоты и кольцевой регистр сдвига периодически вырабатывают восемь однополярных импульсов тока , частоты следования которых и временные сдвиги между которыми одинаковы. Импульсы тактовых частот FI и FZ, поступая на младший разряд триггерного счетчика цепи задания (ячейки 18-21), продвигают единицы но разрядам счетчика, деля частоту в каждом разряде на два (здесь и в дальнейшем название счетчиков и других элементов «задания и «обратной связи чисто условное). Импульсы тактовых частот FS и FS, постуная на младший разряд триггерного счетчика цени обратной связи (ячейки 28-31), делают то же самое.

Данная операция происходит следующим образом.

Импульс тактовой частоты FI считывает ячейки 19 и 21. Единица при этом переписывается в ячейку 20. Импульс тактовой частот FZ продвигает единицу из ячейки 20 в ячейку 19. Одновременно с этим выходной импульс ячейки 20 считывает единицу из ячейки 24 и записывает ее в ячейку 23. Импульс тактовой частоты F только подтверждает состояние ячеек 18 и 20. Следующий цикл импульсов тактовой частоты продвигает единицу из ячейки 19 в ячейку 18, а затем возвращает ее в ячейку 21.

Импульсы тактовых частот F и F, воздействуя на триггерный счетчик цепи обратной связи, производят аналогичные операции.

Так как при установке начальных условий в старший разряд триггерного счетчика цепи обратной связи (ячейка 37) заиисывается единица (что соответствует уменьшению емкости этого счетчика наполовину), четвертый импульс тактовой частоты fs считывает единицу из ячейки 37 и занисывает ее в ячейку 40 и 41. Восьмой импульс тактовой частоты FI считывает единицу из ячейки 25 и записывают ее в ячейки 38 и 39.

Схема управления и защиты действует в этом режиме следующим образом.

Импульс тактовой частоты Fe или FS считывает ячейку 40, и ее выходной импульс считывает ячейки 41 и 44. Выходной импульс ячейки 44 записывает единицу в ячейку 45 и считывает ячейку 49. При этом единица в реверсивном регистре может передаваться только от ячейки 49 к ячейке 48, так как полупроводниковый триод ячейки 4 в это время еще открыт. Одновременно с этим изменяется состояние управляющего триггера 53. Очередной импульс тактовой частоты (F или F) продвигает единицу из ячейки 45 в ячейку 42 и готовит схему к следующей операции.

Импульс тактовой частоты (F2 или 4) считывает ячейку 38, а ее выходной импульс аналогично ранее рассмотренному возвращает единицу из ячейки 48 в ячейку 49, вновь изменяя состояние управляющего триггера 53. Скважность выходного импульсного напряжения триггера 53 за каждый период определяется выражением;

S : I п

где /U - длительность одного

полупериодгз

(импульса); 4 - длительность другого полупериода

(паузы).

Частота переключений триггера 53 связана с частотой тактовых импульсов FI слег,

дующим соотноп1ением; --

2

разрядов триггерного

где п - количество счетчика.

Среднее зиачение выходного импульсного напряжения триггера 53 за период;

:,

и,

ср

где бо - напряжение коллекторного питания

триггера;

Т - период колебаиий выходного импульсного напряжения триггера. Даниый режим работы схем1л удобен для первоначальной проверки ее и при наладке. При наличии импульсов задания и импульсов обратной связи схема действует следующим образом.

Если преобразуемые сигналы Ll и бя представлены в аналоговой форме, они подаются сначала на цифро-аналоговые фупкциональные преобразователи 59 и 60, а затем в частотной форме - на соответствующие входы схем «И 57 и 5S. Частотные нреобразуемые сигналы вводятся непосредственно па входы этих схем. В данном режиме эти схемы разрешают прохождение импульсов к соответствующим блокам синхронизации, так как на другие их входы подаются разрешающие (высокие отрицательпые) нотенцналЕЛ с соответствующих выходов триггеров защиты 55 и 56.

Блоки синхронизации работают следующим образом.

При отсутствии импульсов задания на входе триггера 13 последний занрещает прохождение импульсов через схему «И //, так как па один из ее входов подается низкий отрицательный потенциал с триггера 13. Импульсы тактовой частоты F- периодически записывают единицу в ячейку 12, а им 1ульсы тактовой частоты FI считывают ее, но ввиду запрета со стороны схем «И //, импульсы в ячейку 10 не передаются.

Импульс частоты задания f изменяет состояние триггера 13, вследствие чего па одном из входов схемы «И 11 появляется разрешающий потенциал, и схема // разрешает передачу единицы из ячейки 12 в ячейку 10 с тактовым импульсом F. Импульс тактовой частоты FZ считывает ячейку 10, а ее выходной импульс считывает ячейки 19 и 21 (единица в младшем разряде к этому моменту может находиться только в одной из этих ячеек). Одновременно выходной импулЕзС ячейки 10 возвращает триггер 13 в исходное состояние, запрещая прохождение следующего импульса через схему «И //. Следовательно, в блоке синхронизации импульс частоты /1 замещается импульсом тактовой частоты FZ. Аналогично работает блок синхронизации и в цепи обратной связи с импульсами тактовых частот FS и Fr.

Так как оба триггерных счетчика синхронно управляются импульсами тактовых частот F, FZ и FS, F(,, а импульсы задания вводятся на их входы синхронно с импульсами тактовых частот FZ и FT, схема модулятора надежно защищена от потери информации.

Данное обстоятельство порождает определенное ограничение для частот fi и /2, заключающееся в том, что эти частоты не должны превыщать частоту тактовых импульсов, т. е.

, а .

При нарушении этих условий проис.ходит безвозвратная потеря информации.

Особенностью работы схемы при наличии импульсов частот f и /2 состоит в том, что наряду с тактовыми импульсами триггерные счетчики заполняют импульсы частот 1 и /г, а это приводит к у.меньшению их относительной емкости, вследствие чего несколько повышается частота импульсного напряжения триггера 53 и изменяется скважность импульсного напряжения. Частота переключений триггера 53 определяется выражением: f Pi-fi

/вых -

2

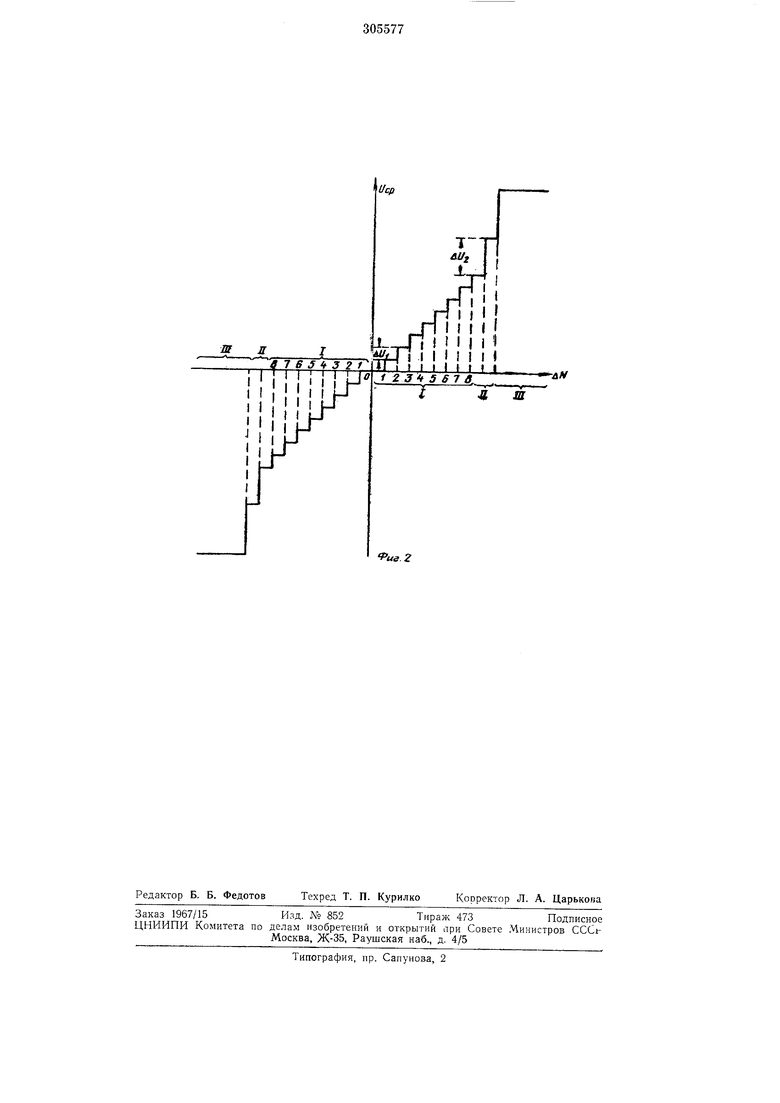

Выходная характеристика модулятора изображена на фиг. 2, где по оси ординат отложены средние значения выходного напряжения триггера 53 в функции разности AN между числом импульсов частоты F и числом импульсов частоты fzБлагодаря частотно-фазовому принципу работы схемы, а также вследствие дискретности ввода импульсов на входы, происходит квантование по времени выходного напряжения, определяемое тактовой частотой и частотами fi и /2, заполняющими счетчик, и квантование по уровню, вызванное дискретностью поступления импульсов частот /i и /2- Данные утверждения справедливы для зоны I (см. фиг. 2) выходной характеристики модулятора.

Приращение среднего значения выходного импульсного напряжения на один имнульс частоты fi или /2 определяется фор.мулой

. lSrИз формулы видно, что стабильность работы модулятора зависит от стабильности напряжения, питающего триггер 53. Широтно-импульсно модулированное напряжение с выхода последнего поступает на суммирующий усилитель 61 для предварительного усиления по напряжению.

Возможно относительное переполнение одного из счетчиков импульсами частот /i или

/2 при больших или длительных рассогласованиях в системе. Если нри это.м разность имнульсов частот FI и F превысит половину емкости триггерного счетчика, со старшего разряда переполненного счетчика проследуют один за другим два импульса, что без схемы защиты мол-сет привести к изменению фазы выходного импульсного напряжения триггера 53 на 180° и, как следствие, к реверсу исполнительного устройства системы,

в которой работает данный модулятор.

Схема защиты работает в этом случае следующим образом. Если, например, переполнение счетчика произошло по цепи задания, т. е. , то первым выходным импульсом

со старшего разряда переполненного счетчика единица в реверсивном регистре продвигается из ячейки 48 в ячейку 49, а вторым - из ячейки 49 в ячейку 50, так как выходные импульсы стробирующих ячеек 38 и 49 разрешают продвижение единицы в реверсивном регистре из ячейки 49 только в ячейку 50. Далее схема действует аналогично ранее рассмотренному, но единица в реверсивном регистре передается уже между ячейками 49

и 50 или между 48 п 47, если переполнение произошло за счет .

Следовательно, в этом случае состояние управляющего триггера 53 не изменяется, а триггер управления 54 периодически изменяет свое состояние под воздействием выходных импульсов со старших разрядов триггерных счетчиков.

Особенность работы с.хемы в данном режиме заключается в том, что уровень квантования выходного импульсного напряжения триггера 54 по амплитуде задан несколько больше зфовня квантования триггера 54 (за счет изменения коллекторного напряжения питания триггеров 52 и 54, что позволяет

реализовать зону П на выходной характеристике модулятора (фиг. 2).

Более высокий уровень квантования выходного импульсного нанряжения по амплитуде At/2 позволяет ускорить действие исполнительного устройства системы, в которой работает модулятор, и быстро ликвидировать возникшее рассогласование. Для этого необходимо, чтобы со старшего разряда счетчика цепи обратной связи поступили один за другим два импульса. Схема возвращается к нормальному режиму работы в пределах зоны .1 выходной характеристики.

Возможен случай, когда работа в предегласование и режим, при котором сохраняется длительное время. В этом случае если переполнение происходит по цепи частоты задания /,, триггерный счетчик цепи задания систематически переполняется, и единица в реверсивном регистре передвигается от ячейки 48 к ячейкам 49-5/. В момеит передачи единицы от ячейки 50 к ячейке 51 изменяется состояние триггера 56 и, как следствие, снимается разрешающий потенциал со входа схемы «И 57, которая запрещает прохождение импульсов частоты /i иа вход схемы синхронизации. Состоянне унравляющих триггеров 53 и 54 остается иеизмеиным, а иа вход суммирующего усилителя подается добавочный потеициал с выхода триггера защиты 56, что приводит к еще большему возрастанию панряжения иа выходе усилителя 61 (зона III на выходной характеристике). Это способствует еще большему форсировапию работы исиолпительного устройства системы и быстрому возвращению ее к нормальному режиму. Блок унравления и защиты обладает др:намической намятью. Это его свойство нроявлястся в том, что он вместе с триггерпыми счетчиками запоминает разность числа импульсов задапия и обратной связи в пределах емкости своей динамической иамяти, которая онределяется формулой: .2(m-2), где т - число ячеек реверсивного регистра. Это позволяет простыми техпическими средствами иолучить выходпую характеристику цифрового широтио-импульспого модулятора с ограничением по максимуму. Возвращение схемы модулятора в нормальный режим работы происходит автоматически, так как переполняется счетчик в цеци обратной связи, и единица в ревереивном регистре передается между ячейками 48 и 49. Процесс защиты новторяется, пока не будут устранены причины рассогласования. В схеме удобно предусмотреть сигнализацию для режима защиты нутем нодключеиия триггеров защиты 55 и 56 к сигнальным лампам через усилители. Получение выходиой характеристики модулятора с неременным уровнем квантования по амплитуде и зопой ограиичеиия позволяет без существенного усложнения схемы зиачительио расширить возможности настройки регулятора с данным модулятором и получить процесс регулирования, близкий к онтимальпому. Предмет и 3 о б р с т е н и я Цифровой широтпо-импульсиый моду.тятор, содержащий геператор тактовых импульсов, кольцевой регистр сдвига, блоки сипхропизацип, триггерные счетчики, блок управления и защиты, содержащий стробирующие ячейки, регистры сдвига, управляющие триггеры и триггеры защиты, а также схемы «И, аналого-цифровые нреобразователи и суммирующий усил 1тель, отличающийся тем, что, с целью иовышения точности его работы, выходы старших разрядов счетчиков через стробирующие ячейки нодключены ко входу кольцевого и реверсивпоIo регистров, выходы которых подключепы ко входам трех управляющих триггеров и двух триггеров защиты, выходы которых соедипепы со входом суммирующего усилителя.

Т-ие 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты | 1973 |

|

SU446940A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1968 |

|

SU217047A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЧИСЛО-ИМПУЛЬСНОГО КОДА В НАПРЯЖЕНИЕ ПОСТОЯННОГО ТОКА | 1972 |

|

SU432674A1 |

| ШЙРОТНО-ЙМПУЛЬСНЫЙ МОДУЛЯТОР | 1967 |

|

SU199526A1 |

| Устройство для стабилизации частоты вращения электродвигателя | 1990 |

|

SU1707723A1 |

| Устройство для управления синусоидальными вибрациями | 1985 |

|

SU1269112A1 |

| Система связи с асинхронной дельта-модуляцией | 1989 |

|

SU1624695A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО- ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО-^ | 1973 |

|

SU375651A1 |

| Устройство измерения частотных характеристик группового времени запаздывания четырехполюсников | 1988 |

|

SU1631511A1 |

| Устройство для квантования в установках с импульсно-кодовой модуляцией | 1977 |

|

SU733099A1 |

Даты

1971-01-01—Публикация