1

Изобретение относится к области вычислительной техники и может быть использовано для выполнения множительно-делительных .операций над переменными, представленными частотой повторения импульсов, а также в качестве устройства для формирования унитарного кода отношения двух частотных последовательностей.

Известно частотно-импульсное множительно-делительное устройство, содержащее два триггера и импульсно-потенциальпые схемы совпадения.

Получение импульсной последовательности на выходе, сформированной из частоты FI, только после прихода импульса частоты FZ увеличивает дисперсию ошибки выходного сигнала в результате пульсации «пачки импульсов на выходе на величину периода частоты р2.

Цель изобретения - получение на выходе устройства импульсов, сформирОванных из частоты FI, сразу после прихода импульса частоты FS за счет предварительного запоминания числа импульсов FI в периоде FZ и списывания их частотой PI с приходом импульса частоты FS.

Это достигается тем, что устройство дополнительно содержит третью, четвертую, пятую и шестую схемы совпадения, дифференциальную цепочку и реверсивный счетчик.

являющийся запоминающим устройством отношения частот в каждом периоде частоты FZ. Выход реверсивного счетчика через схему совпадения связан с триггером, выход которого управляет прохождением частот FZ и FI.

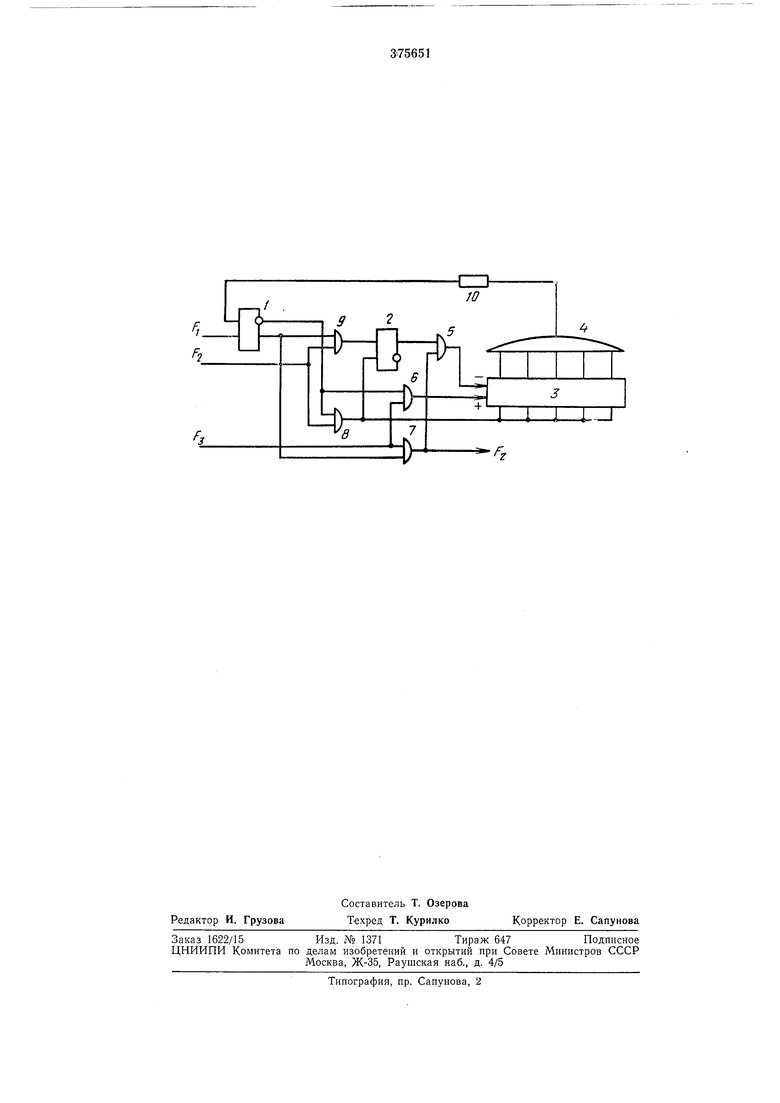

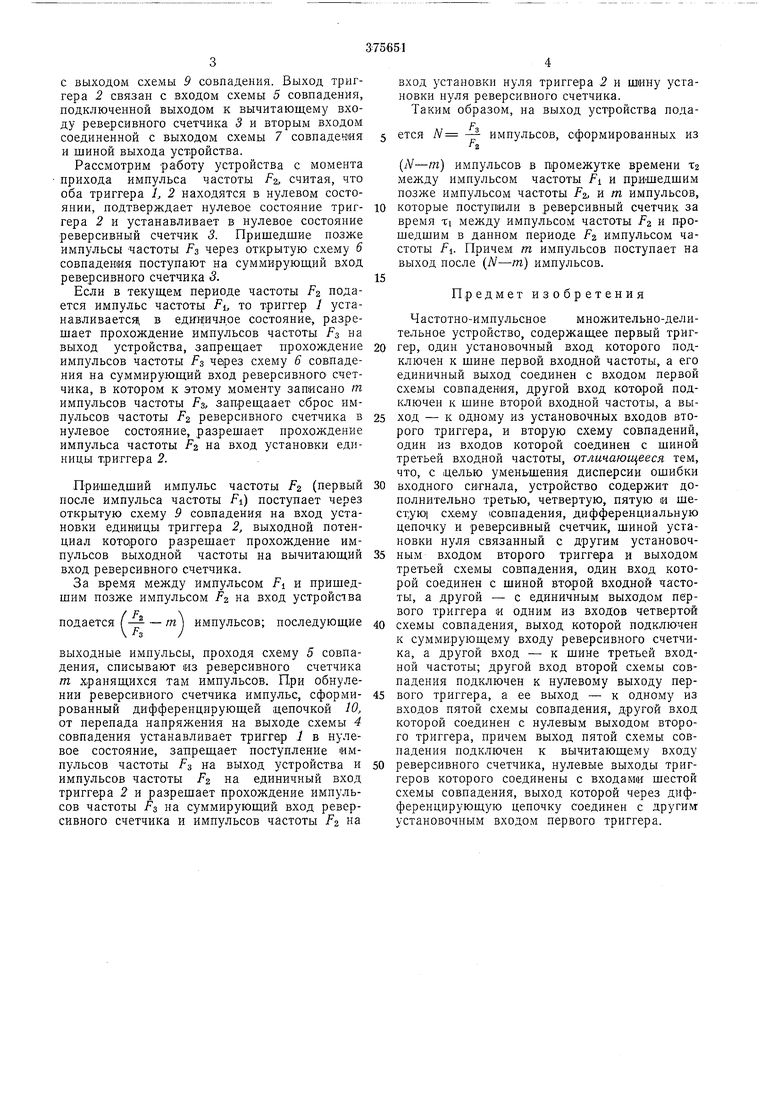

На чертеже показана схема устройства. Устройство содержит триггеры 1 п 2, реверсивный счетчик 3, схемы 4-9 совпадения,

дифференцирующую цепочку 10.

Шина входной частоты Fi соединена с выходом установки единицы триггера /, единичный выход которого подключен к входам схем 7 и 9 совпадения. Второй вход последней соединен с шиной входной частоты FZ и входом схемы 8 совпадения, другим входом связанной с нулевым выходом триггера / и входом схемы 6 совпадения, у которой второй вход подключен к шине входной частоты

FS и входу схемы 7 совпадения. Выход схемы 6 совпадения соединен с суммирующим входом .реверсивного счетчика 3, а нулевые выходы его триггеров - с входом схемы 4 совпадения, выходом через дифференцирующую

цепочку 10 подключенной к входу установки нуля триггера /.

Шина установки нуля реверсивного счетчика 3 подсоединена к выходу схемы 8 совпадения и установочному входу триггера 2,

другой установочный вход которого соединен 3 с выходом схемы 9 совпадения. Выход триггера 2 связан с входом схемы 5 совпадения, подключенной выходом к вычитающему входу реверсивного счетчика 3 и вторым входом соединенной с выходом схемы 7 совпадения5 и шиной выхода устройства. Рассмотрим работу устройства с момента прихода импульса частоты FZ, считая, что оба триггера 1, 2 находятся в нулевом состоЯНИН, подтверждает нулевое состояние триг-ю гера 2 и устанавливает в нулевое состояние реверсивный счетчик 5. Пришедшие позже импульсы -частоты FS через открытую схему 6 совпадения поступают на суммнруюпдий вход реверсивного счетчика 3.15 Если в текущем периоде частоты FZ подается импульс частоты FI, то триггер 1 устанавливается в единичное состояние, разрешает прохождение импульсов частоты FS на выход устройства, запрещает прохождение20 импульсов частоты Fa через схему 6 совпадения на суммирующий вход реверсивного счетчика, в котором к этому моменту записано tn импульсов частоты FS, запрещаает сброс импульсов частоты FZ реверсивного счетчика в25 нулевое состояние, разрешает прохождение импульса частоты FZ на вход установки единицы триггера 2. . Пришедший импульс частоты FZ (первый30 после импульса частоты Fi) поступает через открытую схему 9 совпадения на вход установки единицы триггера 2, выходной потенциал которого разрешает прохождение импульсов выходной частоты на вычитающий35 вход реверсивного счетчика. За время между импульсом Fi и пришедшим позже импульсом FZ на вход устройства / Р подается ( - -от j импульсов; последующие40 выходные импульсы, проходя схему 5 совпадения, списывают из реверсивного счетчика m хранящихся там импульсов. При обнулении реверсивного счетчика импульс, сформи-45 рованный дифференцирующей цепочкой Ю, от перепада напряжения на выходе схемы 4 совпадения устанавливает триггер 1 в нулевое состояние, запрещает поступление «мпульсов частоты з на выход устройства и50 импульсов частоты FZ на единичный вход триггера 2 и разрешает прохождение импульсов частоты РЗ на суммирующий вход реверсивного счетчика и импульсов частоты FZ на 4 вход установки нуля триггера 2 и шину установки нуля реверсивного счетчика, Таким образом, на выход устройства подартся j- импульсов, сформированных из (N-т) импульсов в промежутке времени Т2 между импульсом частоты FI и пришедшим позже импульсом частоты FZ, л т импульсов, которые поступили в реверсивный счетчик за время TI между импульсом частоты FZ и прошедшим в данном периоде FZ импульсом частоты Fi. Причем m импульсов поступает на выход после () импульсов, Предмет изобретения Частотно-импульсное множительно-делительное устройство, содержащее первый триггер, один установочный вход которого подключен к шине первой входной частоты, а его единичный выход соединен с входом первой схемы совпадения, другой вход которой подключен к шине второй входной частоты, а выход - к одному из установочных входов второго триггера, и вторую схему совпадений, один из входов которой соединен с шиной третьей входной частоты, отличающееся тем, что, с целью уменьшения дисперсии ошибки входного ситнала, устройство содержит дополнительно третью, четвертую, пятую и шест,ую| схему совпадения, дифференциальную цепочку и реверсивный счетчик, шиной установки нуля связанный с другим установочным входом второго триггера и выходом третьей схемы совпадения, один вход которой соединен с шиной второй входной частоты, а другой - с единичным выходом первого триггера и одним из входов четвертой схемы совпадения, выход которой подключен к суммирующему входу реверсивного счетчика, а другой вход - к шине третьей входной частоты; другой вход второй схемы совпадения подключен к нулевому выходу первого триггера, а ее выход - к одному из входов пятой схемы совпадения, другой вход которой соединен с нулевым выходом второго триггера, причем выход пятой схемы совпадения подключен к вычитающему входу реверсивного счетчика, нулевые выходы триггеров которого соединены с входами шестой схемы совпадения, выход которой через днфференцирующую цепочку соединен с другим установочным входом первого триггера.

Jrt

3

:-ч

4

cr

ID

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО- ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1973 |

|

SU367430A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1972 |

|

SU424188A1 |

| ОДТЕНТНО-ТЕХНН-Г- :^':и|БИБЛИОТЕКА | 1970 |

|

SU287404A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕУСТРОЙСТВО | 1968 |

|

SU217047A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ ВЫЧИТАЮЩЕЕ УСТРОЙСТВО | 1971 |

|

SU423125A1 |

| ЧАСТОТНО-ИМПУЛЬСНАЯ СЛЕДЯЩАЯ СИСТЕМА | 1973 |

|

SU372543A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ и ДЕЛЕНИЯ ЧАСТОТНО- ИМПУЛЬСНЫХ СИГНАЛОВ | 1972 |

|

SU333564A1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ ВЫЧИТАЮЩЕЕ УСТРОЙСТВО | 1970 |

|

SU284442A1 |

| Частотно-импульсное множительно-делительное устройство | 1975 |

|

SU556437A1 |

| УСТРОЙСТВО для СИНХРОНИЗАЦИИ ИМПУЛЬСОВ | 1972 |

|

SU350151A1 |

B

f.

Авторы

Даты

1973-01-01—Публикация