Изобретение относится к абласти устройств, используемых при регистрации стационарных, периодических закономерностей.

Устройства, исп-ользуемые для решения этой задачи, известны.

Недостатком их является то, что мин-имальное .рассгояние между двумя соседиими отсчетами определяется временем кодирования аналоговой величины и .временем регистрации результата -в заданную ячей;Ку запоминающего блока. Лучшее -время, которое достигнуто в известном устройстве, равно 30-40 мксек.

С целью (повышения разрешаюш,ей способности, регистр адреса состоит из двух групп триггеров, причем счетный вход первого три|-гера первой группы регистра адреса соединен с выходом последнего триггера второй группы регистра адреса, потенциальные выходы триггеров первой группы регистра адреса соединены с соответствуюшими входами схемы сравнения.

Другие входы схемы сравнения соединены с потенциальными выходами соответствующих разрядов счетчи1ка, счетный сход которого соединен с выходом задающего генератора. Имлульоный .выход схемы сравнения сое.динен со входами блока кодирования и 1Программ,ного блока, выход которого соединен со счетным входом первого триггера второй группы релист1ра адреса.

Цель изобретения достигается введением в устройство дополнительного регистра (счетчика) и схемы сравнения.

По сравнению с известными устройствами накопления предлагаемое устройство может получить разрешающее время порядка 0,1 мксек и менее.

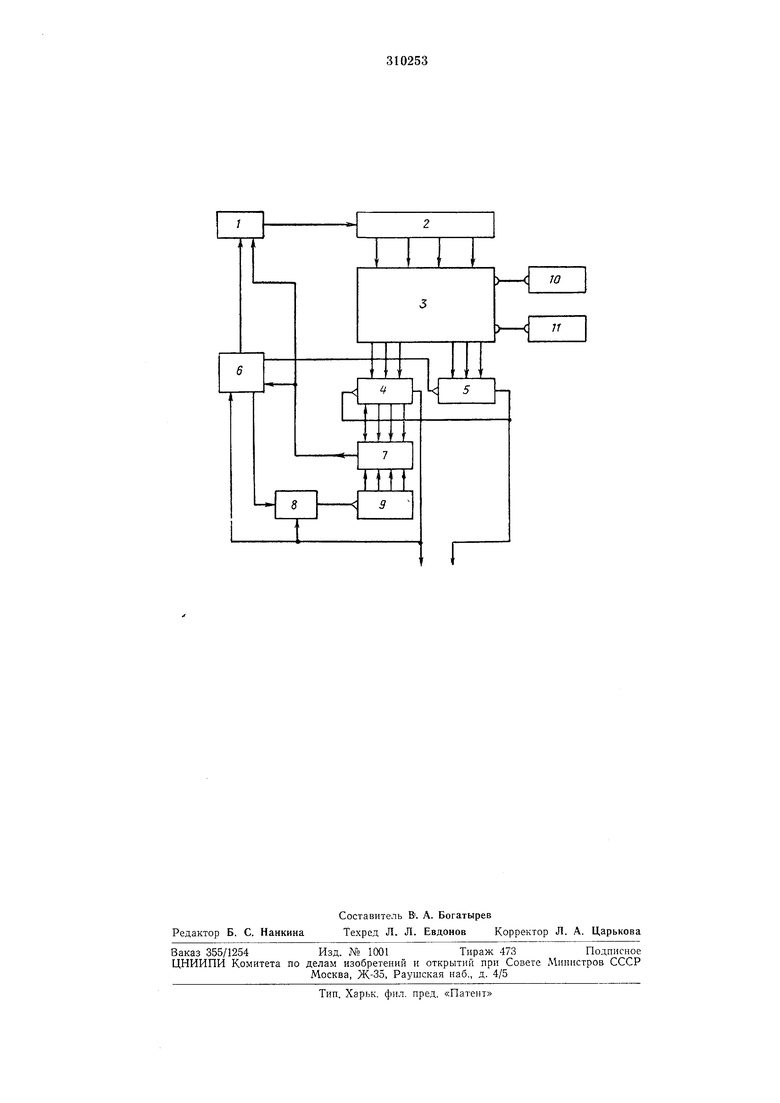

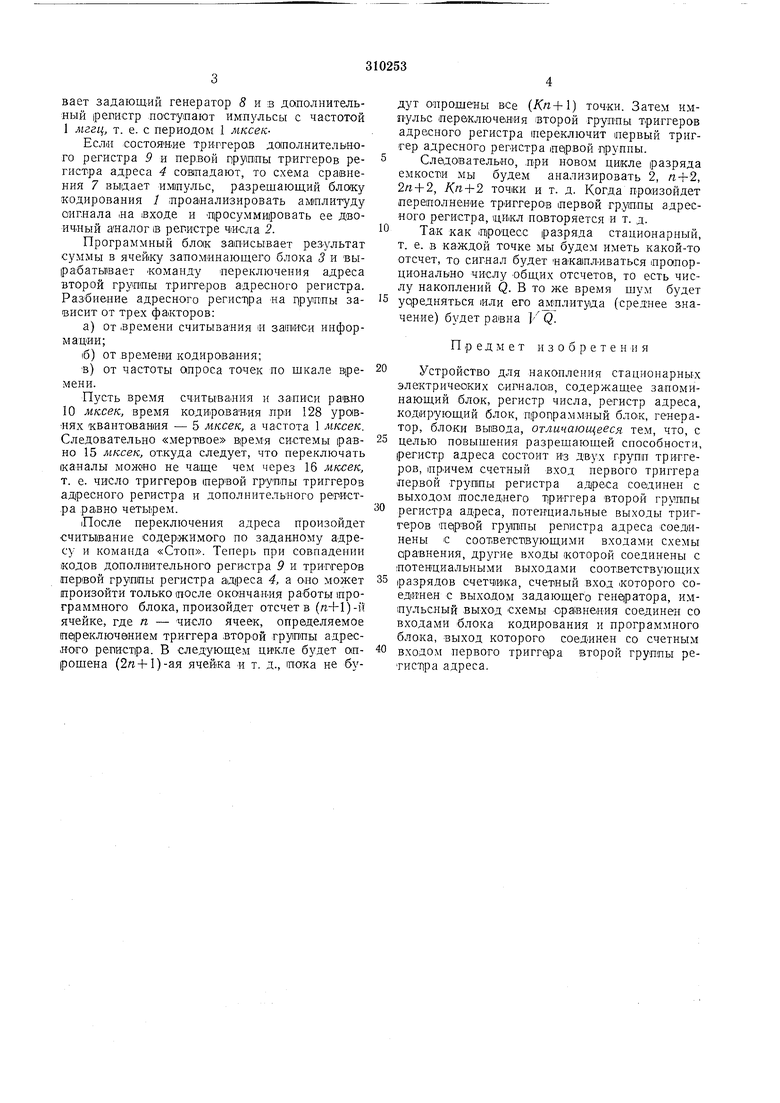

На чертеже приведена блок-схема предложенного устройства, где:

/ - блок кодирования; 2 - регистр числа; 3 - запоминающий блок; 4 - .первая лрулпа триггеров адресного .регистра; 5 - вторая группа триггеров адресного регистра; 6 - программный блок; 7 - схема сравнения; 8 - задающий генератор; 9 -- дополнительный регистр (счетчик); 10, 11 - блоки вывода информации.

Для пояснения работы устройства рассмотрим накопление сигнала (разряда конденсаTOipa), который проходит в тепловых шумах и по амплитуде лежит ниже уровня шума.

Разряд, т. е. закон разряда, периодически повторяется и оинхронизирован с началом отсчета. Время разряда равно 1 мсек, точность с которой нужно изме|рить, равна 1/1000, т. е. время отсчета равно 1 мксек. Синх|ронно с .началом разря.да запускается программный блок 6, а регистры адреса 4, 5, числа 2 и дополнительный регистр 9 устанавливаются в нулевое состояние. Программный блок открывает задающий генератор 8 и в дополнительный |репи€тр .поступают импульсы с частотой 1 мггц т. е. с периодом 1 мксекЕсли состояние триргерол доиолнительного регистра 5 и первой лруопы триггеров регистра адреса 4 сонпадают, то схема сравнения 7 выдает имтульс, разрешающий блоку кодирования 1 (проанализировать амплитуду оигнала ,на входе и П|росумми1ровать ее двоичный аналог IB регистре числа 2.

Программный блок записывает результат суммы в ячейку запоминающего блока 3 и вырабатывает «оманду переключения адреса второй груопы триггеров адресного регистра. Разбиение адресного регист1ра на ripynobi зависит от трех факторов:

а) от времени считывания н заетиси информации;

i6) от времени кодирования;

в) от частоты опроса точек по щкале времени.

Пусть время считывания и записи равно 10 мксек, время кодирования лри 128 уровнях квантавания - 5 мксек, а частота 1 мксек. Следовательно «мертвое время системы равно 15 мксек, откуда следует, что переключать каналы можно не чаще чем через 16 мксек, т. е. число триггеров лервой группы триггеров адресного регистра и дополнительного регистра равно четырем.

После переключения адреса произойдет считывание содержи.мого по заданному адресу и команда «Стоп. Теперь при совпадении кодов дополнительного регистра 9 и триггеров первой группы регистра адреса 4, а оно может произойти только иосле окончания работы программного блока, произойдет отсчет в (п+1)-й ячейке, где п - число ячеек, определяемое переключением триггера второй группы адреслого регистра. В следующем ци1кле будет апрощена (2« + 1)-ая ячейка « т. д., пока не будут опрошены все (/С«+1) точки. Затем импульс пербключения второй группы триггеров адресного регистра переключит первый триггер адресного регистра пе|рвой лруппы.

Следовательно, лри новом цикле разряда емкости мы будем анализировать 2, n-f2, 2л + 2, К.п+2 точки и т. д. Когда произойдет переполнение триггеров лервой группы адресного регистра, (цикл повторяется и т. д.

Так как процесс разряда стационарный, т. е. в каждой точке мы будем иметь какой-то отсчет, то сигнал будет нака1пЛИваться пропорционально числу общих отсчетов, то есть числу накоплений Q. В то же время шум будет

урредняться 1ИЛИ его а 1тлитуда (среднее значение) будет равна 1/Q.

Предмет изобретения

Устройство для накопления стационарньгх электрических сигналов, содержащее запоминающий блок, регистр числа, регистр адреса, кодирующий блок, пропраммный блок, генератор, блоки Вывода, отличающееся тем, что, с

целью повышения разрешающей способности, регистр адреса состоит из двух групп триггеров, причем счетный вход первого триггера первой группы регистра адреса соединен с выходом последнего Т1риггера второй группы

регистра адреса, потенциальные выходы триггеров пе1рвой грушпы регистра адреса соединены с соответствующими входами схемы сравнения, дрзгие входы которой соединены с потенциальными выходами соответствующих

разрядов счетчика, счетный вход которого соединен с выходом задающего гене|ратора, импульсный выход схемы сра1внения соединен со входами блока кодирования и программного блока, выход которого соединен со счетным

входом первого TpHrreipa второй группы реTHCTipa адреса.

Авторы

Даты

1971-01-01—Публикация