Мастоящое изобретение относи1ся к облаети вычиелителыш техники, а iiMeujio к ycT|ioiiетву для оценки вероя1Ч1остио-стат11етнческ1:х характериетик динамичееких ироцеесов и может быть ненользовано в устроистиа.ч для онределения вероятиостно-статнсгических хара.ктериетик в еистемах т ра1 ле11ня.

Извеетны ycTpofieTiia д. 01|,енки )оятноетно-етатиетичееких ха.рактеристнк дина мичееких ироцеесов, еостоя1цие из 2-х входн)1х yeTpoiieTB, генератора ечетных нмнулнсов, 2-х алп1: нтуди1)1х селекторов, устройства управления, .множительного устройства. НаКО; теля, еумматора, блока де,1еиия. блока умножецня, региет 1иру1ои его ycTpoiicTua и блока нитания.

Оеобепноеть нредлагаемого устройства состоит в том, что оно снабжено матрице иитеграторов. етрочиые п столбцовые входы которой подключены к выходам амил1 тудиых селекторов, а каждый из интеграторов, ее подключен к В1 1ходу генератора счетных имнульеов, ко входу которого подключен один из выходов устройства управления, три других входа которого соединеиы с блоком делеиня. миожительным ycTpoiicTBOM и кол:м татор()м, а вы.ходы матрицы нодключены к комм татор , соедииеииому со входами лглчсиппеля и множительного уетройетва, нри-ем выход миожительного устройства иодключается к сумматору. выход которого соединен с одним из входов блока лмножения. 2-й вход блока умиоження подсоединен к выход} блока деления, одни из входов блока деления подключен к ВЫХОД} накоиителя, а выход блока умножения соединен со входо.м регистрирук)Н1его устройства.

Предложеииое устройство иозволяет В1Лчнслять регрееени одного елуча1 1ного ироцееса отиоснте.чьно др}того (}словные математичеекие о/ чндаиия сл}чайных нроцеееов.

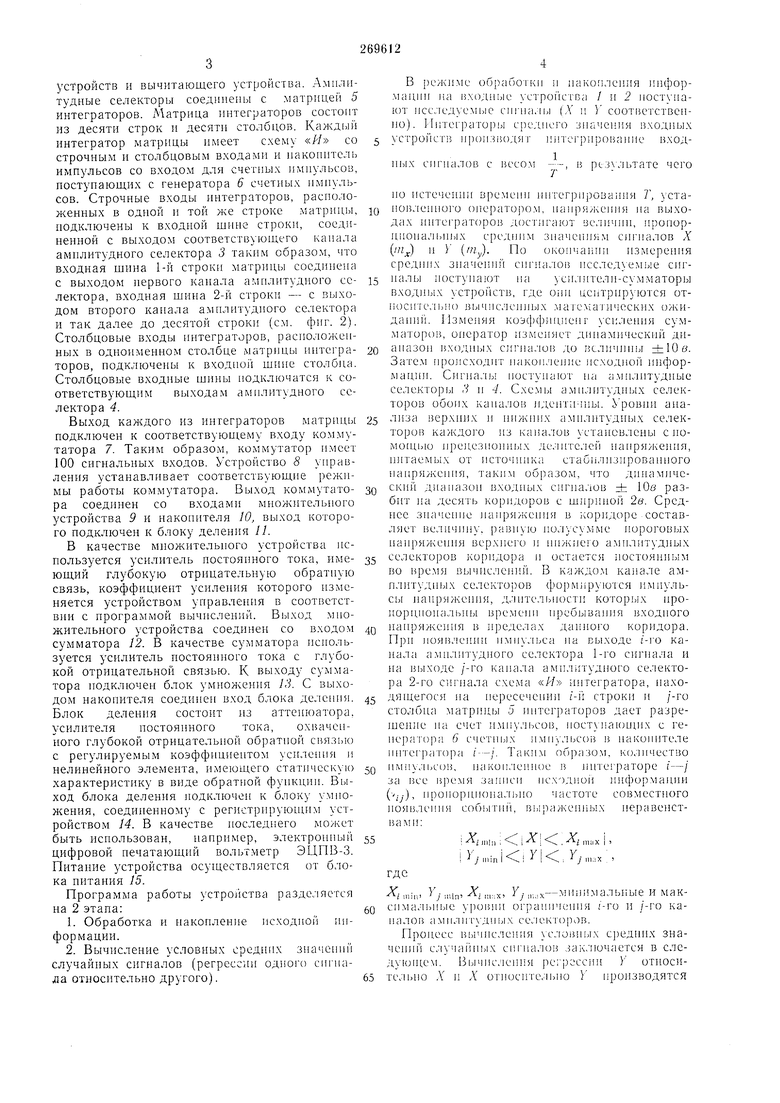

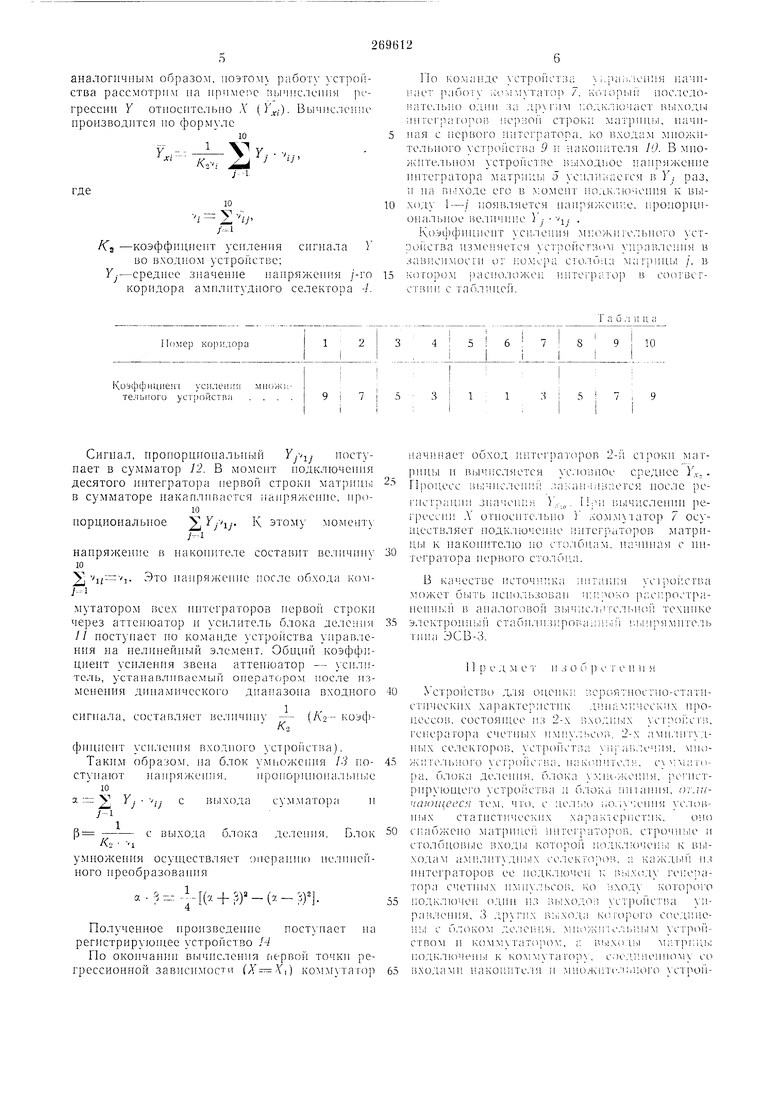

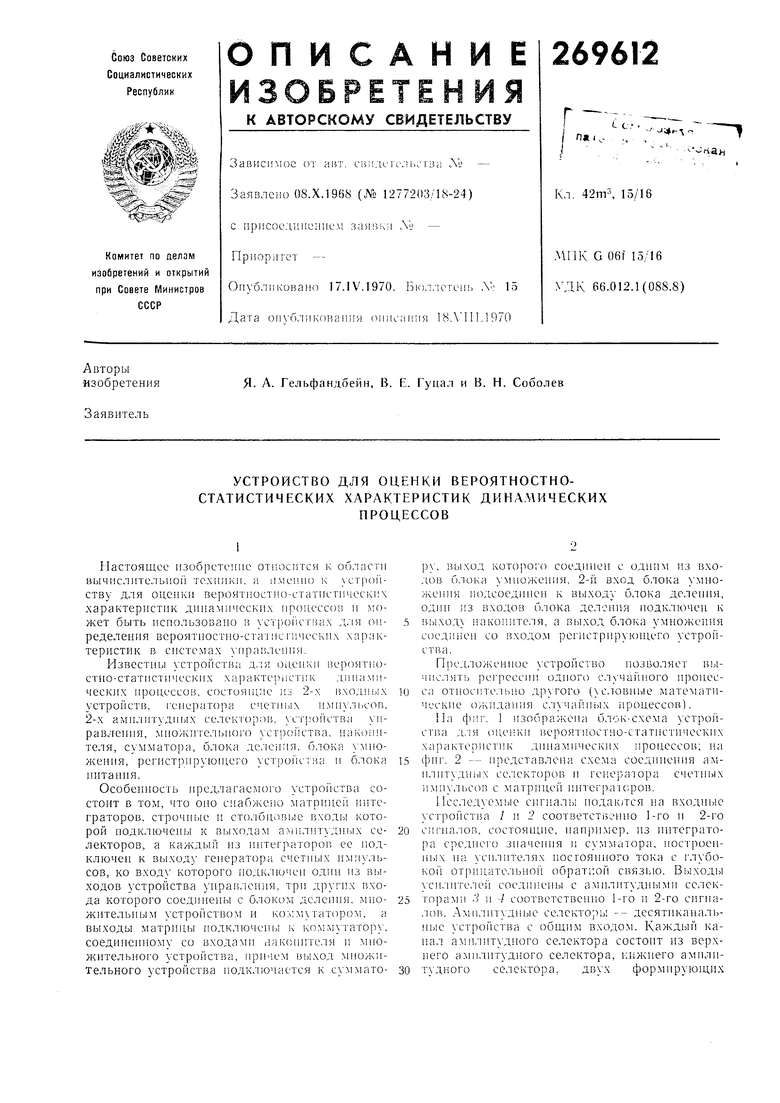

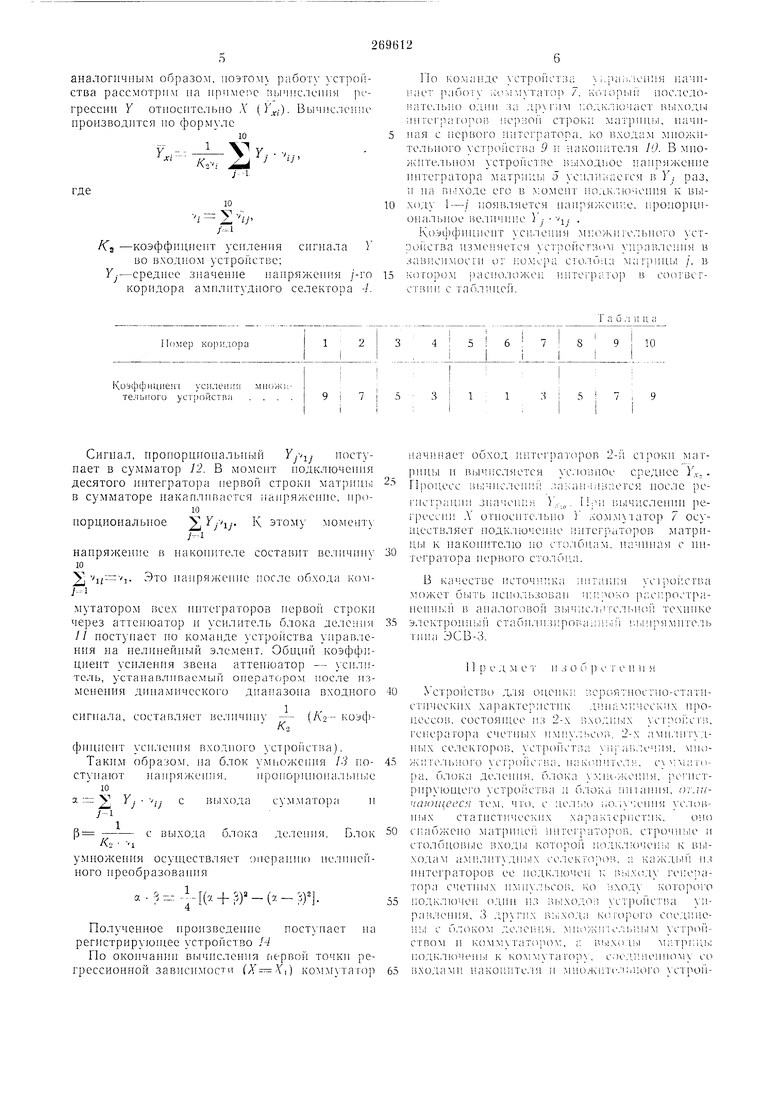

Па фиг. 1 изображена блок-схема }eTpoiiстка д.ля оценки вероятностно-статистических характеристик дииамических ироцеесов; иа фиг. 2 -- представлена ехема соедниения амнлнт}дн1)1х еелекторов н генератора счетных имн}Л1 сов с aтpицeй иитеграторов.

11сслед}ем1 1е сигналы иодакпся иа входшле уетройетва / и 2 соответственно 1-го и 2-го сигналов, состояни1е, иаиример, из интегратора среднего значения н е}.мматора, ностроенных на }силнтелях Г10сгоянного тока с глубокой отрицате.тьно обратной связью. В)1ходы }CH,THTe.iei еоедннены с амилнт диыми селекторами .) и 4 соответствеино 1-го и 2-го еигналов. Ам11лит}Д1|ые селекторы -- десятнканальиые }-стройства с общим входом. Каждый канал амплит}-дного селектора состоит из верхнего амплитудного селектора, нижнего амилитудного селектора, двух формирующи.ч

устройств н вычитающего устройства. Амплитудные селекторы соединены с матрицей 5 интеграторов. Матрица интеграторов состоит из десяти строк и десяти столбцов. Каждый интегратор матрицы имеет схему «Я со строчным н столбцовым входами и накоиитель импульсов со входом для счетных имиульсов, ностуиающих с генератора 6 счетных имиульсов. Строчные входы интеграторов, расположенных в одной н той же строке матрицы, нодключеиы к входной шнне строки, соединенной с выходом соответствующего капала амплитудного селектора 3 таким образом, что входная шина 1-й строки матрицы соедипеиа с выходом нервого канала амилитудного селектора, входная шина 2-й строки - с выходом второго канала амплитудного селектора и так далее до десятой строки (см. фиг. 2). Столбцовые входы интеграторов, расположенных в одноименном столбце матрицы интеграторов, подключены к входной шине столбца. Столбцовые входные шипы подключатся к соответствующим выходам амплитудного селектора 4.

Выход каждого из интеграторов матрицы подключен к соответствующе.му входу ком.мутатора 7. Таким образом, коммутатор имеет 100 сигнальных входов. Устройство 8 управления устанавливает соответствующие режимы работы коммутатора. Выход коммутатора соединен со входами множительного устройства 9 и накоиителя 10, выход которого подключен к блоку деления //.

В качестве мпожительного устройства используется усилитель постоянного тока, имеющий глубокую отрицательную обратную связь, коэффициент усиления которого изменяется устройством уиравлення в соответствии с программой вычислений. Выход мпожительного устройства соединен со входом сумматора 12. В качестве сумматора используется усилитель постоянного тока с глубокой отрицательной связью. К выходу сумматора подключен блок умножения 13. С выходом накопителя соединен вход блока деления. Блок деления состоит из аттенюатора, усилителя постоянного тока, охваченного глубокой отрицательной обратной связью с регулируемым коэффнциептом усиления и нелинейного элемента, имеющего статическую характеристику в виде обратной функции. Выход блока деления подключен к блоку умножения, соединенному с регистрирующим устройством М. В качестве последнего может быть использован, напрнмер, электронный цифровой нечатающпй вольтметр ЭЦПВ-3. Питапие устройства осуществляется от блока ннтания 15.

Программа работы устройства разделяется на 2 этапа:

1.Обработка и накопление исходной информации.

В режиме обработки и накоплеппя ппформацпп па ycTpoficTBa / и 2 поступают псследусм1 1е спшал, (А п У соответствеино). 111 тег р а то р ы t: р сд п е го з i i а ч еп г. я п ходи ых устройств пр()из1и)дят иптегрировапие вход1И)1х сшпалов с весом -, в п(,)Тате че1о

Г

по истечспии времепп пптегрироваппя 7, устаповлепиого оператором, папряжеппя на выходах пптеграторов достигают велпчпп, проиорциопаль1П 1х сред1И1м зпачеппям X (//zj п } (Wy). По окопчании измереипя сред1И х значений сигналов псследуемые сигпалы поступают па усилители-сумматоры входных устройств, где опп цсптрируются отпосите,11,п() В1мчпслсппых .математических (ожида1ии1. Пзменяя коэфф1пи1е11г усилепия сум.маторов, оператор изменяет дпиампческий диапазоп входных сшчиглов до величины ±10 и. Затем происходит накоп.че)Ие псходпой пнформацпп. Спгпа.л) поступают на амилптудпые селекторы 3 и 4. Схемы амплитудпых селекторов обоих капалов пдентичпы. Уровни анализа верхних и нпж1Н1х амплитудных селекторов каждого из капалов устаповлены с поМОЩ1ИО нрецезпопных делптелей напряжения, П1ггаемых от источпика стабилпзпроваиного напряженпя, таким образом, что дипамический диапазон входных спгпа.юв ± 10в разбит па десять коридоров с шпрппой 2в. Среднее зпаче1И1е папряжепня в составляет величину, равпую полусумме пороговых папряження верхнего п нпжнего амплитудных селекторов корпдора и остается постоянным во время вычислений. В каждо.м канале амилитудшлх селекторов формируются пмиульсы напряжения, длительности которых проиорцпопальпы Bpe.Meini иребыва1Н1я входпого напряжения в пределах данного коридора. При появлении пмпу,льса па выходе I-ro канала амплитудного селектора 1-го сигнала и па выходе /-го капала амплитудного селектора 2-го сигнала схема «Я интегратора, находян 1,егося на пересечепии г-й строки н /-го столбца матрицы 5 иитеграторов дает разрешение па счет и.мпульсов, пост паюп1их с геператора 6 счетных илпг льсо в пакопнтеле inrrei-ратора (--/. Тг.ки.м образом, колпчество импульссл), накоп.лсппое в пптеграторе i-/ за все время записи исходно 11пс|)орма.и (v;y), частотс совместного оявле и я co6i)T 11, ВЫ pa неравенст ами:

: С . miiX Ь

I io,,,i,.r ,„..:,

i iiiii-, 0 in i i n-.ji-м и мальпь е и макcHMaJ b ij e ограп1 чен я I-ro и /-го ce.ieKiopoB.

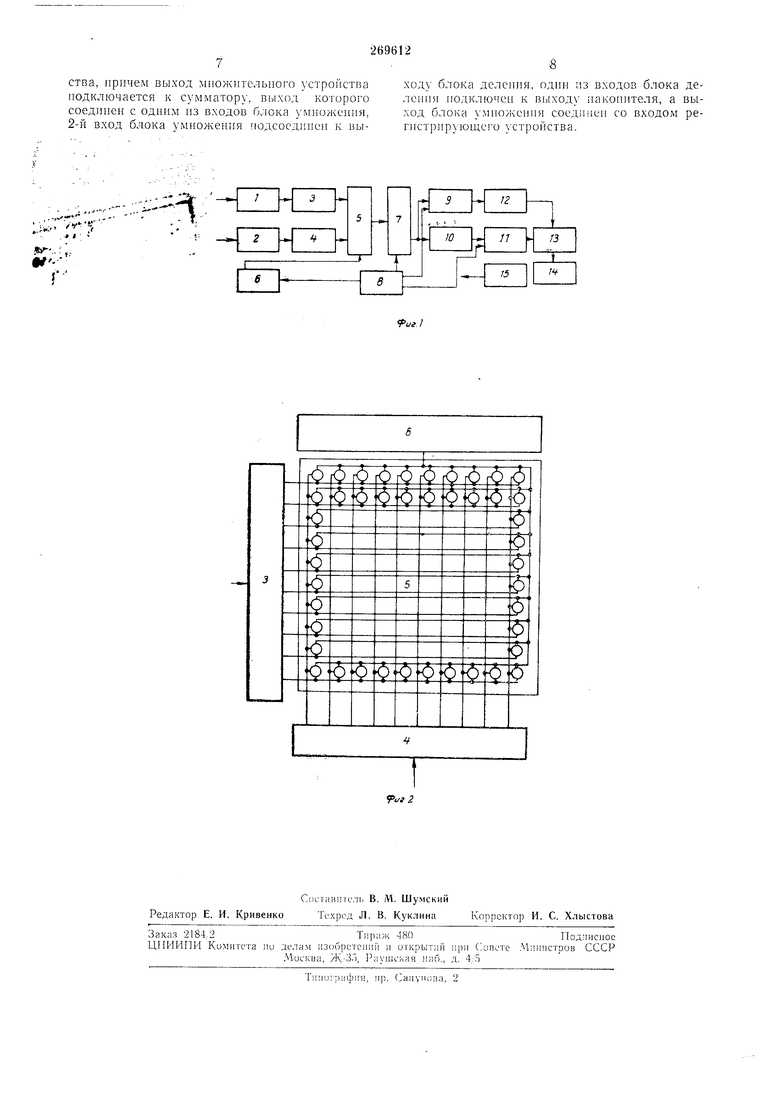

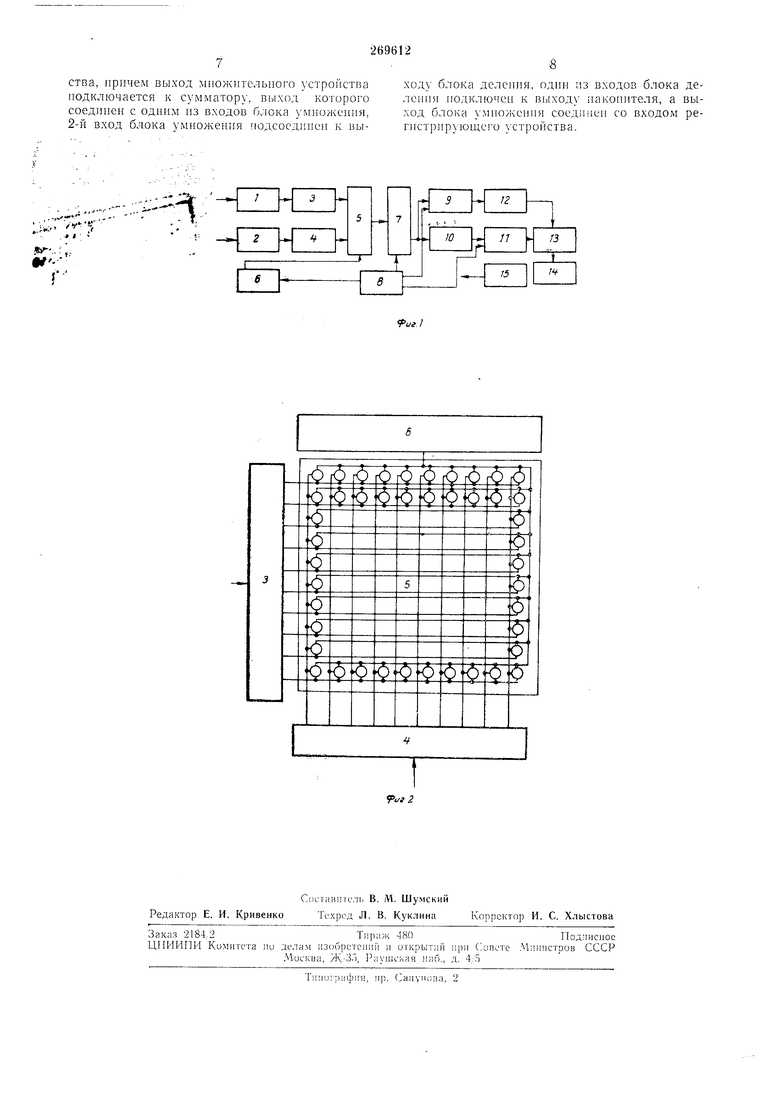

вычисления ус; О15нь х с)едних значеи)Й случа 1 ых с1ПпалоБ заключается в следую.е. В чпсле 1ия perjjeccHH У относнаналогичным образом, поэтом} prioory устройства рассмотрим на иримеос вычисления рс-грессин У отпоситс:1ьио X (). Вычисление ироизводится но 10 1 Г . V J. t ; ; : I - У. и /-1 АГа -коэффициент усиления сигнала 1 во входном ycTpoiiCTBe; Yj-среднее значение наиряження j-ro 15 коридора амилитудиого селектора -/. 5 10 По команде xCTpoikTisa ;.ра;;ле1Н1я начи1;аег работу ;;ом мхтатор 7. ;-;(Морыи иоеледо1 ате;1ьно один :К1 дхл- лючает выходы ИИ гегра гор;) иерной строки iaтpицы, иачииая с первого HHTerjiaTopa. ко г ходам множительиого устр{111етиа 9 и накоиитсля 10. В мно/кнте.твиом ycTpoiiCTBC выходное паиря/кеиие иитегратора матрицы 5 усиливас1ея в У,- раз, и иа выходе его в ;омеит иодк.иочеиня к BI Iходу 1-/ появляется иа11ря кен11е. нроиорцнонал1 ное 15еличнне ) j , . Коэффиниеит тиления мнс/1 н1ел1ииг -о устooiiCTBa изменяется устройством унравления в зависимости or HOMcjUi столбца лиычшиы /, в KoroiioM )асио;10 кеи итсгр;гго 1 в еоотвегст: ип с таблинс.

Сигнал, пронорциональиый Yfij иоступает в сумматор 12. В момент нодключеиия десятого интегратора первой строки матрииы 25 в сумматоре накаиливается иаиряжеине, иро2 ЭТОМУ момеит порциональиоенапряжение в накоиителе составит ве.чичииу 30 2 i;- ). Это наиряжение иосле обхода ком/ 1мутатором всех интеграторов iiepBoii строки через аттенюатор и усилитель блока деления 35 // поступает ио устройства уиравления иа нелинейный элемент. Обнип коэффициент усиления звена аттенюатор - сил 1тель, устанавливаемый оператором после изменения динамического диапазоиа входного 40 сигнала,составляет величииу - ( коэффициентусиления входиого устройства). Такимобразом, на блок ум11ожения 13 но- 45 стунают паи ряже ИИ я, ироно1)ииоиа.тьиые у.--. YJ -ij с В1)1хода сум.матора и У-1 вв1хода блока делеиия. Блок 50 умпожения осуществ.чяет аиеранию нел1П1ейного нреобразова1Н1я а.М(а + 3)-(а-3). Полученное ироизведение поступает иа регистрируюи1,ее устройство 14 ооход И1ггсграторов z-u cipOKii матрииы и вычисляется услог иое средиее Iv. . Процесс В 141 слеии1: :;а; аи- 1|в:;егся после рс|исг;) значении ),,,, В1,1числе1нп1 регресснн Л относнтельно ) хом.мукпор 7 осуществляет иодк;иочеиие иитег})1торов матрицы к наконителю но сто.тбиа.лк начиная с ннTerpaiopa иер)Н1го столбца. П р е д м е т и з о б р с г е и и у. cтpolicтвo д.тя оценк в.срояти ости о-статистических характеристик л,ииа ;ических ироцессов. состоя1цее из 2-х г.ходиых устпо1;сгв, гснерагора счет1н 1х имиу/л сог, 2-х амилит лН1 1х селекторов, устройстр.а: И1;1Г,:е.ия. множите.ишсич) стр(), иа коии гсл Si, схчмато)а, бл1)ка де,1еиии, блока у лК/ чення, ре Ч1стрнруюн1е1о устро1 СИ5а и ци1ания, (ггли/aiotitdCf те.м. что, с це.тыо пО.: ;енн5 ус.ювИ1)1Х статистичеекнх xapa;-:iepiicTm. оно С1:абжеио матрице ишчччшторов. строчные и СТОлби01И 1е ВХОДЬ KOTOpOil НОД,ТК)ЧСНЫ к В)1ходам амилнтудн х селск-чгюв. а каждвЙ из ннтеграторов ее нодк.почен к генератора сче1Ч11,1х HMiiy.iiHoii, ко которого цод1,1юче11 один из В15 ходоз стройства уирав., 3 .других ,ixo;ui KOiiipcTX) соеди.иены с блоком дс,. лм1ож гк,;ьц1 1м устройством н коммутат(11и)л , а (iibi Л1атр|;ц1 подключены к roii. соедцлеииому ео входами накоиите, ц MHO.KiiTi-.i;,:ioro хстройства, причем выход миожптельпого устропства подключается к сумматору, выход которого соедипеи с одним пз входов блока улгножеиия, 2-й вход блока умноженпя юдсосдлиеп к вы

.

;.-,;ГТ

ходу блока делеппя, одпп из входов блока деЛС1ИИГ иодключеп к выходу пакопнтеля, а выход блока у.лиюженпя соеди 1еп со входом регистрируюпдсго устройства.

Даты

1970-01-01—Публикация