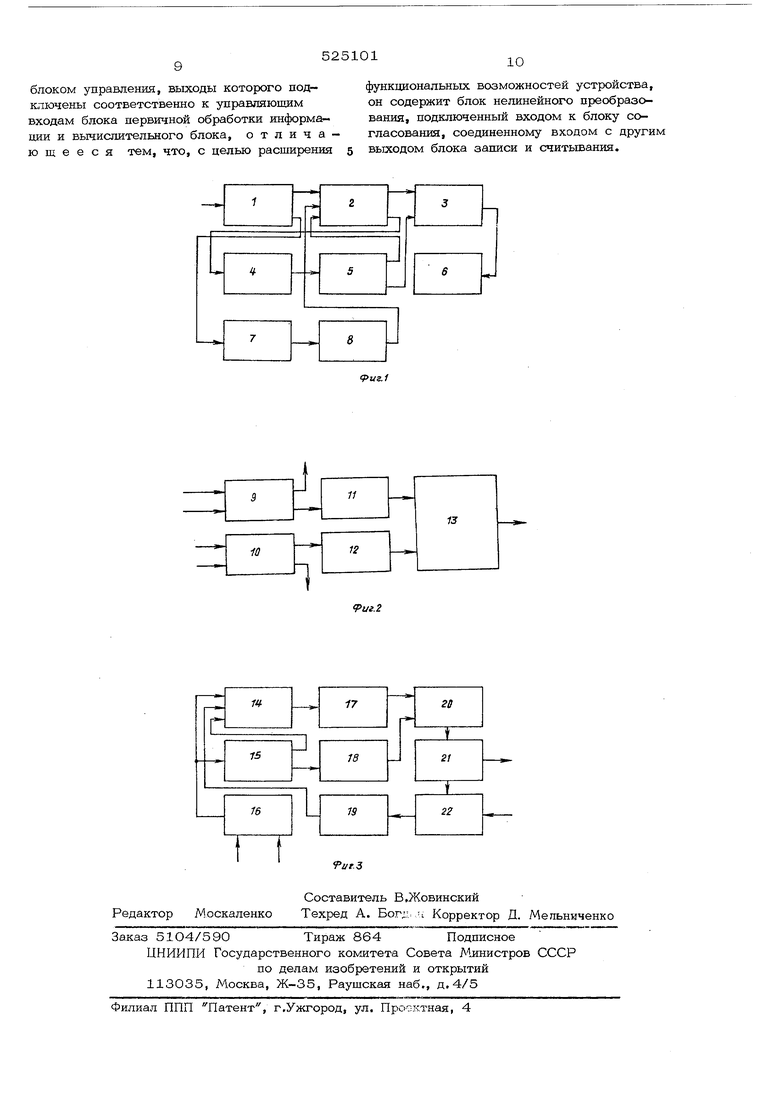

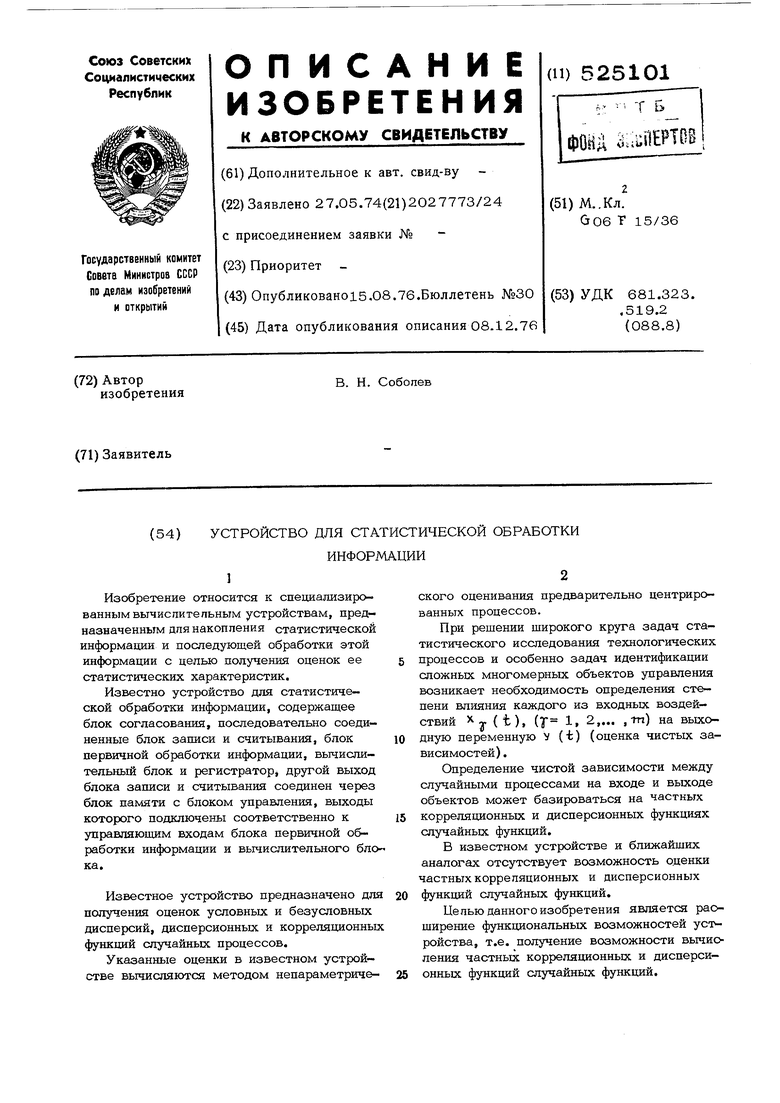

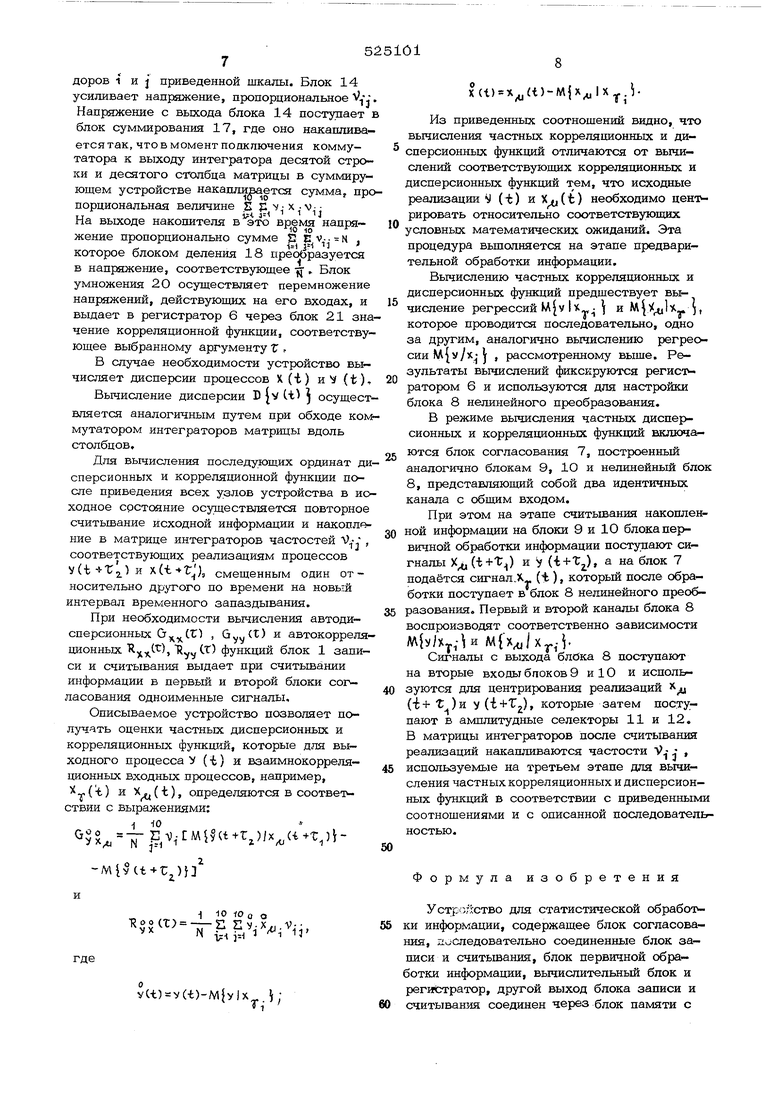

(54) УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОЙ ОБРАБОТКИ Эта цель достигается тем, что устройство содержит блок линейного преобразова ния, подключенный входом к блоку согласо вания, соединенному входом с другим вых дом блока записи и считывания. Предлагаемое устройство поясняется во можным вариантом технической реализаци блок-схема которого представлена на фиг. На фиг. 2 приведена блок-схема одного из вариантов блока первичной обработки инфо маци на фиг. 3 - блок-схема вычислител ного блока. Блок 1 записи и считывания (см.фиг.1 совместно с подключенным к его выходу блоком 2 первичной обработки информации составляет устройство накопления и первичной обработки информации, выходы котор го соединены со входами вычислительного блока 3, и через блок 4 памяти - с блоком управления 5. Выходы блока управления 5 соединены с блоками 2 и 3. Выход блока 3 связан со входом регистратора 6, а выход блока 1 записи и считывания через блок согласования 7 и блок 8 нелиней ного преобразования соединен со входом блока 2. Блок первичной обработки информации (с1уг.фиг.2) состоит из блоков согласования 9, 1О, амплитудных селекторов 11, 12 и матрицы 13 интегралов. Вычислительный блок (см.фиг.З) включает в себя блок умножения 14, блок накопления 15, коммутатор 16J блок суммирования 17, блок деления 18, квадратор 19, блок умножения 2О, блок памяти 21 и блок суммировашет 22. Программа работы устройства подразделяется на три этапа: накопление исходной информации; считывание накопленной информации с носителей и первичная обработка считанной информации; вычисление оценок статистических характеристик случайных процессов. На этапе накоплен ш исходной информации случайные процессы, подлежащие обработке, подаются на блок 1, представляющий собой типовое многоканальное устройство записи и считывания на магнитной ленте, обеспечивающее возможность введения изменяемого при считывании временного сдви га реализаций случайных цроцессов. Блок 1 осуществляет запись исходных реаггизаций случайных процессов. При работе устройства на втором и третьем этапах при вычислении условных и безусловных математических ожиданий и дисперсий, а также корреляционных и дисперсионных функций случайных процессов, блок согласования 7 и блок нелинейного преобразования 8 при этом отключаются. На втором этапе работы исходная, информация из блока 1 поступает в блок 2 пернвичной обработки информации. При считывании исходной информации в каналах считььвания процессов, например X (t) и J/ (t) (для простоты обозначим (t) и v (i) вводятся временные запаздывания П и , обеспечивающие временной сдвиг исходных реализаций величины C C:.г,-T Блок 2 имеет два канала (по числу обрабатываемых реализаций). В каждом последовательно соединены входное устройство с амплитудным селектором, выход которого подключен к матрице 13 интеграторов. В блоках согласования 9 и 1О, каждый из которых, в свою очередь, состоит из интеграторов средних значений и сумматора, построенных на усилителях постоянного тока, осуществляется центрирование методом скользящей средней исходных реализаций считываемых процессов. Текущие оценки математических ожиданий случайных процессов, определяемые во входных устройствах, поступают на входные интеграторы блока 4 памяти для усреднения текущих оценок математических ожиданий на всем интервале наблюдения и запоминания их с целью последующих вычислений. Центрированные реализации процессов подвергаются в усилителях блоков согласования 9 и 10 сжатию так, что на входах амплитудных селекторов действуют сигналы. динамический диапазон которых -iQ В. Коэффициенты усиления усилителя сигнала (t) и К2усилителя сигнала У (i) при этом фиксируются Амплитудные селекторы 11 и 12 преобразуют сигналы, поступающие на их входы, в импульсы напряжения, длительность которых пропорциональна времени пребьтания сигналов в пределах коридоров амплитудных селекторов. Эти имцульсы поступают на входы матрицы 13. Каждый интегратор матрицы имеет типовую диодную ячейку И со строчным и столбцевым входами и накопитель импульсов со входом для счетных импульсов, поступающих с генератора счетных импульсов блока управления 5. Строчные входы интеграторов, расположенных в одной и той же строке матрицы, подключены к входной щине строки соответствующего канала амплитудного селектора сигнала X {i), а столбцевые входы интеграторов, расположенных в одноименном столбце матрицы интегратоов, подключены к входной щине столбца, вязанной с соответствующим выходом аМгплитудного селектора сигнала V (t). Осуществлением данной коммутации выходов амплитудных селекторов с матрицей интеграторов обеспечивается в процессе считывания исходной информации интегрирование счетных импульсов в матрице, т.е. фиксация в интервале наблюдения час готы л) , пропорциональной времени совместного пребьшания сигнала А (t) в I -м коридоре амплитудного селектора 11 и сигнала V (-) в j -м коридоре амплитудного селектора 12, После считьтания, первичной обработки и накопления обработанной информации в матрице интеграторов вычислительный блок 3 производит вьгаисление оценок статистических характеристик случайных процессов. Вычисления начинаются с нахождения оценок условных математических ожиданий процессов. Работа устройства на примере вычисления условного математического ожидания N- TTf/i -ii где X.J и у- - величины, пропорциональные напряжениям в серединах коридоров 1- X и j - X амплитудных селекторов входных устройств, производится следующим образом. По команде управляющего устройства на чинает работу коммутатор 16, который последовательно подключает выходы интеграторов первой строки матрицы, начиная с первого интегратора, ко входам множительного устройства 14 и накопителя 15. При вычислении регрессии работает первый канал блока умножения 14 устройства. Этот канал осуществляет усиление напряжений , пропорциональных частости V , поступающих с выходов интеграторов первой строки с коэффи1щентом усиления, изменяе- мым блоком управления в соответствии с номером столбца j , в котором расположен подключаемый в данный момент интегратор матрицы. Зависимость коэффициента усиления блока умножения 14 от номера столбца матрицы (номера коридора амплитудного селектора) задается по следующей щкале: Номер коридора1234567891 Коэффициент усилия 9753113579 Таким образом, в момент подключения к выходу интегратора 1 - j на выходе бло ка умножения 14 появляется напряжение .:. Это капряжениэ поступает в блок суммирования 17, собранный на базе типового усилителя постоянного тока. В момент подключения десятого интегратора первой строки матрицы в блоке сумглирования накапливает напряжение, пропорциональное величине Sy-v-. К этому моменту сапряже ние в блоке накопления 15 составит S V . л) то напряжение через блок деления 18 потупает на вход блока умножения 0. На блок умножения 20 пост -пают напряения, пропорциональные величинам /iii p-i4Vr На выходе блока умножения появляется апряжение, пропорциональное первой точке егрессии , которое поступает в лок памяти 21 и фиксируется регистратоом 6. После этого начинается цикл вычиления условной дисперсии в соответствии формулой 102 Divlx. --|: v--MivU-i3. 1 Напряжение, пропорциональное вычисленной дисперсии, поступает через блок памяти 21 блока 3. в регистратор 6 и фиксируется. После измерения первой точки условной дисперсии начинается цикл вычислений дисперсионной функции, который производится в соответствии с формулой 1 ° lГ,/i г V -Mivct TipnN E С V-. . 1г1 jrH З По окончании данного цикла вычислений блоки памяти 21 и 4 возвращаются в начальное состояние. После этого производят ся вычисления второй и последующих точек регрессии и условной дисперсии, а также второго слагаемого в выражении для дисперсионной функции. Следующий этап работы устройства - вычисление корреляционной функции, соответствующей выбранно;у у временному сдвигу Г сигналов. Вычисления выполняются в соответствии с формулой j 10 -(О 7Г-- 1;i1 1 3 1 3 В этом цикле коммутатор осуществляет построчно, начиная с первой строки, последовательный обход всех интеграторов матрицы 13. При этом каждый раз в момент подключения интегратора i - i {i,j 1, 2.,,,., 10) блок управления 5 изменяет коэффициент усиления первого канала блока умножения 14, делай его равным величине, пропорциональной произведению V; х.- , в котором величины V ; и X принимаются равным значениям, соответствующим номерам коридоров 1 и j приведенной шкалы. Блок 14 усиливает напрзгжение, пропорциональное V -Напряжение с выхода блока 14 поступает в блок суммирования 17, где оно накапливается так, что в момент подключения коммутатора к выходу интегратора десятой строки и десятого столбца матрицы в суммирующем устройстве накапливается сумма, про порциональная величине S j i i На выходе накопителя время напряжение пропорционально сумме 3 Е - N которое блоком деления 18 гфеЪьразуется в напряжение, соответствующее - , Блок умножения 20 осуществляет перемножение напряжений, действующих на его входах, и выдает в регистратор 6 через блок 21 зна чение корреляционной функции, соответствующее выбранному аргументу Г , Б случае необходимости устройство вычисляет дисперсии процессов X (i) и V (t), Бычисление дисперсии D Jv Ci осуществляется аналогичным путем при обходе ком мутатором интеграторов матрицы вдоль столбцов. Для вычисления последующих ординат ди сперсионных и корреляционной функции после приведения всех узлов устройства в исходное состояние осуществляется повторное считьшание исходной информации и накопление в матрице интеграторов частостей л) , соответствующих реализациям процессов V (t . )J смещенным один относительно другого по времени на новый интервал временного запаздывания. При необходимости вычисления автоди- сперсионных ) , Gy,(t) и автокорреляционныхR Ct), ) функций блок 1 записи и считывания выдает при считьшании информации в первый и второй блоки согласования одноименные сигналы. Описываемое устройство позволяет получать оценки частных дисперсионных и корреляционных функций, которые для выходного процесса V (t) и взаимнокорреляционных входных процессов, например. уС) и (t), определяются в соответ ствии с выражениями: -) 10

-MivCt+r)}

1 10 о о о

Т РЛ -/1Г

где

yCi) v(t)-Mjy|x i; Ti

Формула изобретения

Устройство для статистической обработ ки информации, содержащее блок согласования, яоследовательно соединенные блок записи и считывания, блок первичной обработки информации, вычислительный блок и регистратор, другой выход блока записи и считывания соединен через блок памяти с x(t)(t)-Mjx,lx Y J. Из приведенных соотношений видно, что вычисления частных корреляционных и ди- сперсионных функций отличаются от вычислений соответствующих корреляционных и дисперсионных функций тем, что исходные реализации ) (t) и X(t) необходимо центрировать относительно соответствующих условных математических ожиданий. Эта процедура выполняется на этапе предварительной обработки информации. Бычислению частных корреляционных и дисперсионных функций предществует вы- числение регрессий U и ,1и, которое проводится последовательно, одно за другим, аналогично вычислению регреосииМ|у/х , рассмотренному выше. Результаты вычислений фиксируются регист ратором 6 и используются для настройки блока 8 нелинейного преобразования. Б режиме вычисления частных дисперсионных и корреляционных функций включаются блок согласования 7, построенный аналогично блокам 9, 1О и нелинейный блок 8, представляющий собой два идентичных канала с общим входом. При этом на этапе считьшания накопленной информации на блоки 9 и 10 блока первичной обработки информации поступают сигналы X(-t+t) и у (i+t), а на блок 7 подаётся сигнал.Ху (t), который после обработки поступает в блок 8 нелинейного преобразования. Первый и второй каналы блока 8 воспроизводят соответственно зависимости Miv/Xy, Mfx lx -iСигналы с выхода блбка 8 поступают на вторые входы блоков 9 и 10 и используются для центрирования реализаций (i+ t )и V (t+l которые затем поступают в амплитудные селекторы 11 и 12. Б матрицы интеграторов после считывания реализаций накапливаются частости j , используемые на третьем этапе для вычисления частных корреляционных и дисперсионных функций в соответствии с приведенными соотнощениями и с описанной последовательностью.

блоком управления, выходы которого подключены соответственно к управляющим входам блока первичной обработки информации и вычислительного блока, отличающееся тем, что, с целью расширения

функциональных возможностей устройства, он содержит блок нелинейного преобразования, подключенный входом к блоку согласования, соединенному входом с другим выходом блока записи и считьшания.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1972 |

|

SU357565A1 |

| УСТРОЙСТВО ДЛЯ ОЦЕНКИ РАСПРЕДЕЛЕНИЯ ВЕРОЯТНОСТЕЙ СЛУЧАЙНЫХ ПРОЦЕССОВ | 1973 |

|

SU387391A1 |

| УСТРОЙСТВО для ОЦЕНКИ ВЕРОЯТНОСТНО- СТАТИСТИЧЕСКИХ ХАРАКТЕРИСТИК СЛУЧАЙНЫХ ПРОЦЕССОВ | 1971 |

|

SU314215A1 |

| УСТРОЙСТВО для ОЦЕНКИ ВЕРОЯТНОСТНО- СТАТИСТИЧЕСКИХ ХАРАКТЕРИСТИК ДИНАМИЧЕСКИХПРОЦЕССОВ | 1970 |

|

SU269612A1 |

| ПРЕОБРАЗОВАТЕЛЬ СТОЛБЦА ТЕПЛОВОГО ИЗОБРАЖЕНИЯ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 1999 |

|

RU2152692C1 |

| Устройство для спектрально-корреляционного анализа | 1987 |

|

SU1467557A1 |

| СПОСОБ И УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ ТЕПЛОВОГО ИЗОБРАЖЕНИЯ В ЭЛЕКТРИЧЕСКИЙ СИГНАЛ | 1999 |

|

RU2199830C2 |

| Устройство для решения интегральных уравнений | 1988 |

|

SU1608705A1 |

| Многоканальный знаковый коррелятор | 1976 |

|

SU590763A1 |

| Коррелометр | 1988 |

|

SU1674165A1 |

Авторы

Даты

1976-08-15—Публикация

1974-05-27—Подача