Устройство относится к области моделирования.

Известны аналоговые вычислительные устройства последовательного действия для моделирования динамических процессов в системах, описываемых обыкновенными дифференциальными уравнениями, содержащие блок программного управления с подключенными по заданной программе коммутирующими элементами и блоками, а также блок решения уравнений связи, к которому через блоки запоминающих исполнительных органов и коммутирующие элементы подключены прямые или инвертированные выходы запоминающих интегрирующих блоков на операционных усилителях с конденесаторами в цепи обратной связи и через коммутирующие блоки присоединены последовательно включенные запоминающие устройства с инверторами или без них на входе и запоминающие интегрирующие блоки правых частей.

Предложенное устройство отличается тем, что оно содержит блоки делителей напряжений с параллельно включенными потенциометрами, выходы которых -через нормально разомкнутые коммутирующие элементы блока программного управления подключены к входным резисторам двух групп запоминающих интегрирующих блоков с включенными в их входные цеш соответственно нормально

разомкнутыми и нормально замкнутыми коммутирующими элементами. Причем часть блоков делителей, подключенных к запоминающим интегрирующим блокам первой группы, присоединена входами к выходам запоминающих интегрирующих блоков правых частей, а через другие нормально разомкнутые переключающие элементы соединены непосредственно или через инверторы с выходами интегрирующих запоминающих блоков той же группы. Входы блоков делителей, подключенных к запоминающпм интегрирующим блокам второй группы, соединены через нормально замкнутые коммутирующие элементы с их выходами и через инверторы подключены ко входам начальных условий соответствующих запоминающих интегрирующих устройств первой группы.

Эти особенности позволили уменьшить требуемое число решающих элементов, повысить точность и обеспечить устойчивость.

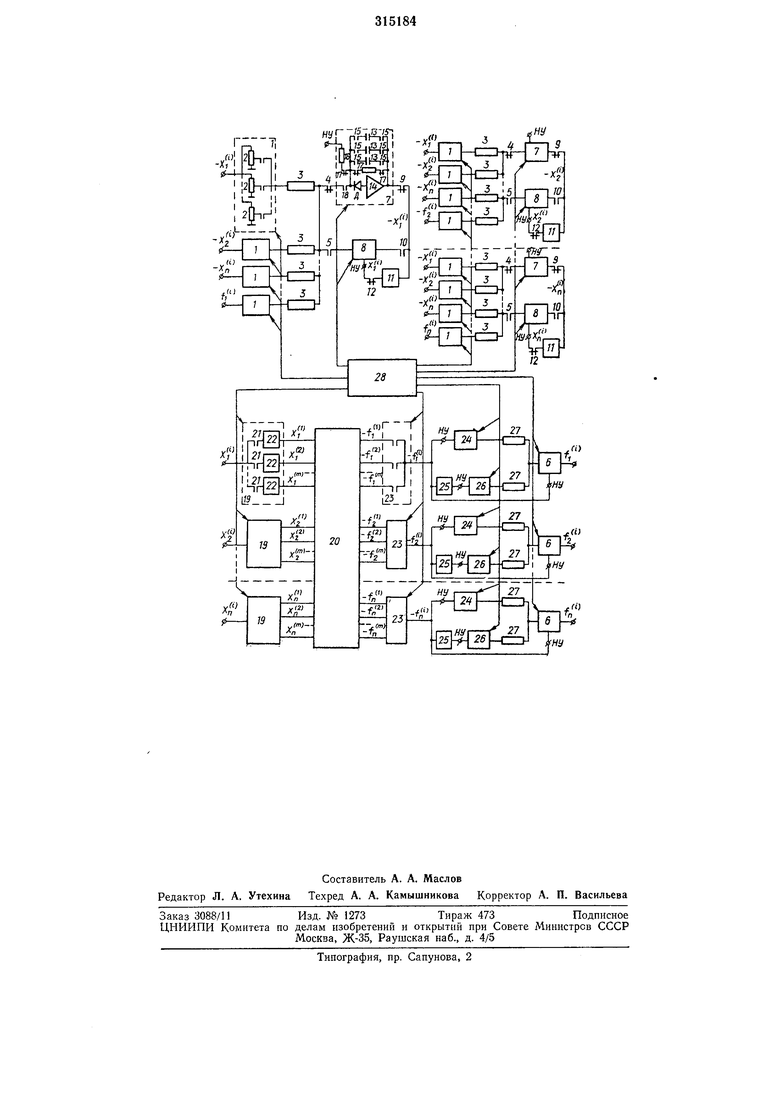

На чертеже приведена блок-схема устройства.

Устройство предназначено в общем случае, для решения систем обыкновенных дифференциальных уравнений вида: f (О 2 где й()аС) лСО/тСО 5() , 2,...,от; т - количество однотипных объектов входящих в сложную систему; п - порядок дифференциальных урав нений одного объекта. Переменные X/); Х,..,, Х(/ подключены ко входам блоков делителей 1, на которых устанавливаются соответствующие коэффициенты матриц A В каждом блоке делителей 1 имеется т параллельно соединенных потенциометров или трехдекадных делителей напряжения 2, выходы которых через коммутирующие элементы соединены в один узел и подключены через резисторы 3 к общим выводам коммутирующих элементов 4 и 5. К этим выводам через делители 1 и резисторы 3 подключены также выходы запоминающих интегрирующих блоков 6 правых частей. К свободным выводам элементов 4 и 5 подключены запоминающие интегрирующие блоки 7 и 8, выходы которых через коммутирующие элементы 9 и W подключены ко входам инверторов 11 и блоков соответствующих делителей 1. Выходы инверторов 11 через коммутирующие элементы 12 подключены ко входам начальных условий (НУ) блоков 8. В запоминающих интегрирующих блоках 6-8 запоминание осуществляется конденсаторами 13, которые могут быть подключены в обратную связь усилителя 14 посредством коммутирующих элементов 15. Для установки начальных условий (НУ) на конденсаторах 13 Предусмотрены резисторы 16, которые через нормально замкнутые коммутирующие элементы 17 подключаются на вход и в обратную связь усилителя 14. Интегрирование осущ.ествляется замыканием коммутирующих элементов 13, к которым подключены вторые выводы коммутирующих элементов 4 и 5, при наличии в обратной связи усилителя 14 одного из конденсаторов 13. W Выходы инверторов 11 подключены ко входам блоков запоминающих исполнительных органов 19, выходы которых подключены ко входам блока 20 рещения уравнений связи (2). В блоках запоминающих - исполнительных органов 19 величины переменных через коммутирующие элементы 21 поступают на входы запоминающих - исполнительных органов 22 для каждой переменной х (в одном блоке 19 имеется т таких органов). Выходы блока 20 через коммутирующие блоки 23 подключены ко входам начальных условий (НУ) запоминающих устройств 24 и 6, и через инверторы 25 - ко входам запоминающих устройств 26. Выходы запоминающих устройств 24 и 26 через резисторы 27 подключены к коммутирующим элементам 18 запоминающих интегрирующих блоков правых частей. В запоминающих устройствах 24 и 26 входы интегрирования отсутствуют. Управление работой блоков и элементов 1, 4, 5, 6, 7, 8, 9, 10, 12, 19, 23, 24 и 26 осуществляется по командам, поступающим из блока программного управления 28. Решение дифференциальных уравнений (1) осуществляется по усоверщенствованному методу Эйлера-Коши. Так как метод ЭйлераКоши принадлежит к числу методов последовательных интервалов, то при рещении уравнений по этому методу процесс рещения необходимо делить на равные интервалы времени Ai. Алгоритм расчета уравнений заключается в следующем: Допустим, уравнения (1) рещаются для ()-го интервала времени, т. е. для интервала времени tj+i-tj. Известны значения правых частей для начала (/+1)-го интервала, т. е. в момент времени tj, которые запомнены в устройствах 6 и 24. Известны также значения переменных в момент времени tj, которые запомнены в блоках 7, S и 19. Рещение уравнений (1) производится в два тапа. В первом этапе или этапе грубого расета уравнения (1) рещаются по методу Эйера, т. е. в течение данного интервала вреени поддерлшваются постоянными праые части Р( после интегрирования уравнеий (1) в течение времени получаютя грубые значения переменных л;}+1 Для онца (/4-1)-го интервала, которые одновреенно с рещением устанавливаются на заоминающих исполнительных органах 22. В локе 20 рещаются уравнения (2) для укаанных значений xj-2i и в результате полуаются грубые значения правых частей fy+i , оторые запоминаются в запоминающих устойствах 26. изменяющиеся линейным законом от значений до fy+i т. е. по формуле pT+ nii-р Повторно проинтегрировав уравнения (1), в течение времени j+i-tj для новых значекий правых частей, получают уточненные значения переменных Ж , по которым определяются и запоминаются для дальнейшего решения уравнений (I) уточненные значения правых частей Яj)J. В исходном режиме на блоках делителей / устанавливаются соответствующие коэффициенты уравнений (1). Начальные условия переменных с учетом масштабов, устанавливаются на запоминающих интегоирующих блоках 7 и 5 поочередным подключением в обратную связь усилителей 14 соответствующих конденсаторов 13. Одновременно эти величины устанавливаются к запоминаются в запоминающих исполнительных органах 22. Переключения конденсаторов 13 в блоках 7 и 5 и исполнительных запоминающих органов 22 в блоках 19 осуществляется по командам, поступающим из блока программного управления 28. После установки начальных УСЛОВИЙ, в блоке 20 решения уравнений связи (2) получаются значения правых частей соответствующие начальному режиму. Решение уравнений связи (2) в блоке 20 можно осун1егтвить методом прямого моделирования или любым другим известным методом. Поочередным переключением соответствуюших каналов связи в КОММУТИРУЮЩИХ блоках 23 и конденсаторов обратной связи 13 в блоках 6 v( 24 производится запоминание начальных значений правых частей уравнений (1). Процесс решения начинается после нажатия кнопки «пуск на блоке программного управления 28. При этом из блока 28 поступает команда на переключение коммутирующих элементов 4 тл 5, 9, 10 -я 12. Элементы 5 и 10 замыкаются, а элементы 4, Р и /2 размыкаются. Размыкаются также коммутирующие элементы 17 в блоках 8 6. Подготавливается схема для осуществления интегрирования уравнений (1) с помощью конденсаторов (на чертеже не показаны), входящих в блоки 8, т. е. подготавливается схема лля осуществления грубого этапа расчета. По командам поступающим из блока программного управления 28 начинают поочередно подключаться в схему решения уравнений (1) соответствующие делители 2 в блоках /, конденсаторы 13 в блоках 5 и 5 и запоминающие - исполнительные органы 22 в блоках 19. Так, по нервой команде подключаются в схему решения первые делители /, нервые конденсаторы в блоках ( и 5 и первые запоминающие исполнительные органы в блоках 19, т. е. собирается блок-схема рещения уравнений первого объекта. После подготовки схемы решения поступает команда на включение коммутирующих элементов /5 в блоках 8, которые в замкнутом состоянии поддерживаются ровно в течение одной (или двух) секунд, т. е. процесс интегрирования уравнений первого объекта длится ровно одну (или две) секунду. Причем правые части fp поддерживатюся постоянными. Это время по масщтабу соответствует времени одного интервала Л. После окончания процесса интегрирования первые конденсатолы в блоках 5 запяжаются грубыми значениями JV| которые одновременно устанавливаются и на первых запоминающих исполнительных органах 22 в блоках 19. По окончании решения уравнений первого объекта схема автоматически переключается для рещения уравнений второго объекта и т. д. до последнего. Как только уравнения всех объектов для грубого этапа первого интервала решены происходит решение уравнений связи - С2) в блоке 20. После решения уравнений (2) получаются грубые значения правых частей рГ которые запоминаются на соответствующих конденсаторах (на чертеже не показаны) в блоках 26, поочередным полключением их в обратную связь усилителей 14. Таким образом, получается, что в запоминающих устройствах 24 и блоках 6 запомнены значени я пpaвlьтx чacJeй.F, , а в запоминающих устройствах 26 - значения F) После получения гпубых значений правых частей f/ первый этап расчета для первого интервяла заврпн1ается. и наптяае ся ВТОРОЙ этап расчета. ПРИ этом пячмыкяются КО ТМУтируюшие элементы 5. 10 ч КОЛ МУТИРУЮПТИР элементы 17 в блоке 7 и запоминаюнтчх устройствах 24 и 26. замыкаются КОММУТИПУЮнтие элементы 4. 9, 12 и коммутируюпше .пементы 17 в блоках 8. Подготяп.тчвается блоксхема для уточнения результатов решения первого интервала, т. е. для решения уравнений (1) по уточненным значениям правых частей. По командам, поступаюпшм из блока программного управления 28.. поочередно подключаются схемы рещения уравнений для всех т объектов. Интегрипование осуществляется конденсаторами блоков и 7. Так как на входы блоков 6 подаются разности - Fp, то в процессе интегрирования правыр части изменяются линейно от значений Р до значений Т-Р Такое изменение правых частей очень близко к действительному их изменению, потому, что кривые изменения правых частей в данном интервале времени аппроксимируются прямым линиями. вительным значениям в момент ti. Уточненные значения переменных для каждого объекта одновременно с интегрированием запоминаются в блоках 5 и в запоминающих исполнительных органах 22 блоков 19. После окончания решения уравнений (1) для всех объектов, в блоке 20 решаются уравнения связи (2), и уточненные значения правых частей для конца первого интервала поочередно запоминаются на конденсаторах запоминаюш;его интегрирующего блока 6 и запоминающего устройства 24. В этом режиме коммутирующие элементы 17 в блоке 7 и запоминающих устройствах 24 и 26 замкнуты. Для осуществления решения уравнений во втором интервале времени в качестве начальных условий используют уточненные значения переменных , запомненные в запоминающих интегрирующих блоках 7 и 5, и правых частей fp, запомненные в блоке 6 и устройстве 24. Процесс решения уравнений для второго и последующих интервалов аналогичен процессу решения первого интервала. При необходимости контролировать величины переменных и правых частей в ходе решения уравнений (1) и (2) можно предусмотреть после каждого интервала расчета автоматическую или ручную регистрадню параметров. При этом команда на начинание решения уравнений в каждом интервале поступает после окончания регистрации. Описанное устройство может быть использовано в сцециализированных вычислительных устройствах, например, для исследования переходных процессов в энергосистемах, многодвигательных электроприводов, применяемых в текстильной промышленности, в автоматических поточных линиях, в металлообрабатывающей промышленности. Предмет изобретения Аналоговое вычислительное устройство последовательного действия для моделироваНИИ динамических процессов в системах, описываемых обыкновенными дифференциальными уравнениями, содерл ащее блок программного управления с подключенными по заданной программе коммутирующими элементами и блоками, а также блок решения уравнений связи, к которому через блоки запоминающих исполнительных органов и коммутирующие элементы подключены прямые (инвертированные) выходы запоминающих интегрирующих блоков на операционных усилителях с конденсаторами в цепи обратной связи и через коммутирующие блоки присоединены последовательно включенные запоминающие устройства и запоминающие интегрирующие блоки правых частей, отличающееся тем, что, с целью уменьшения требуемого числа рещающих элементов, повышения точности и обесЦечения устойчивости, оно дополнительно содержит блоки делителей напряжений с параллельно включенными потенциометрами, выходы которых через нормально разомкнутые коммутирующие элементы блока программного управления подключены к входным резисторам двух групп запоминающих интегрирующих блоков с включенными в их входные цепи соответственно нормально разомкнутыми и нормально замкнутыми коммутирующими элементами, причем часть блоков делителей, подключенных к запоминающим интегрирующим блокам первой группы, ппйсоединена входами к йыходам запоминающих интегрирующих блоков правых частей, а через другие нормально разомкнутые переключающие элементы соединена непосредственно и через инверторы с выходами интегрирующих запоминающих блоков той же группы; входы блоков делителей, подключенных к запоминающим интегрирующим блокам второй группы, соединены через нормально замкнутые коммутирующие элементы с их выходами и через инверторы подключены ко входам начальных условий соответствующих запоминающих интегрирующих устройств первой группы.

Hyrn t i Jf

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования многодвигательного электропривода | 1972 |

|

SU480091A1 |

| Генератор функций | 1984 |

|

SU1166148A2 |

| Система автоматического управления пространственным разворотом объекта | 1989 |

|

SU1679467A1 |

| Программное временное устройство | 1988 |

|

SU1647517A1 |

| Устройство для автоматизации рентгеновской съемки органов грудной клетки | 1980 |

|

SU948370A1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ПЕРЕМЕННОГО ТОКА | 2004 |

|

RU2256184C1 |

| Многоканальное устройство управления | 1986 |

|

SU1409973A1 |

| ВПТБ | 1973 |

|

SU390533A1 |

| Устройство управления буровым агрегатом | 1981 |

|

SU1086134A1 |

| Устройство для автоматизации рентгеновской съемки органов грудной клетки | 1981 |

|

SU1039481A2 |

Даты

1971-01-01—Публикация