Изобретение относится к устройствам управления и регулирования и может быть использовано в системах числового программного управления для управления исполнительными органами станков.

Цель изобретения - повышение точ- ,ности управления.

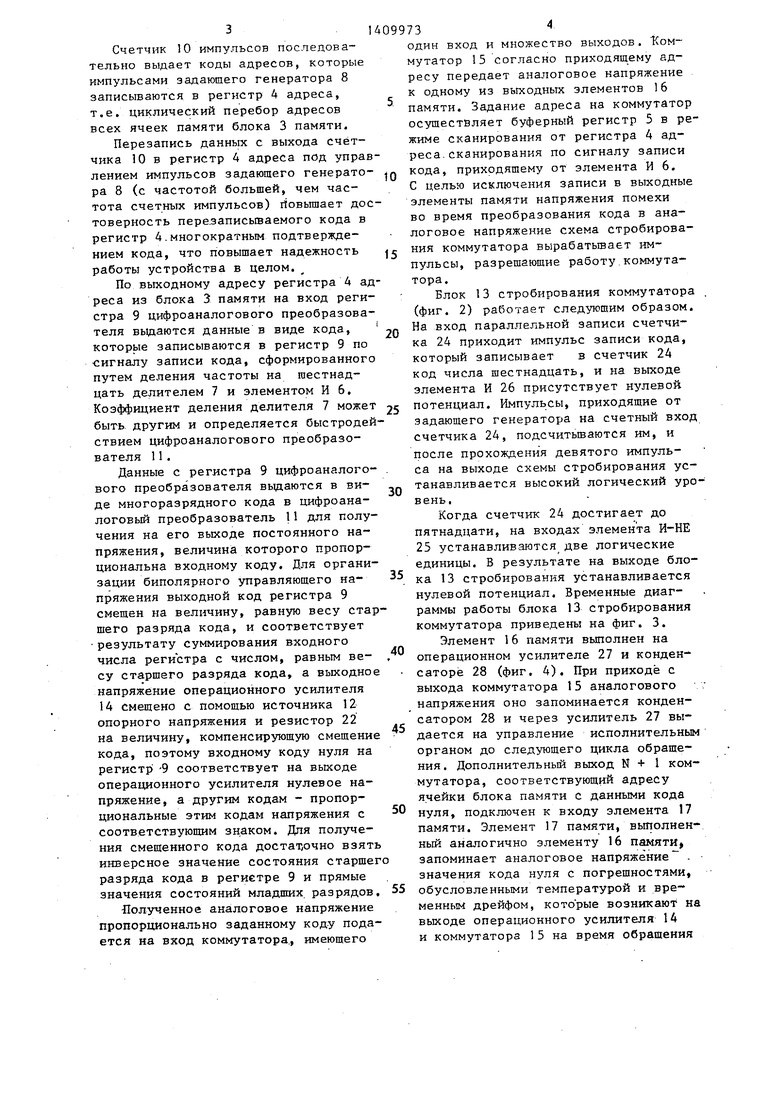

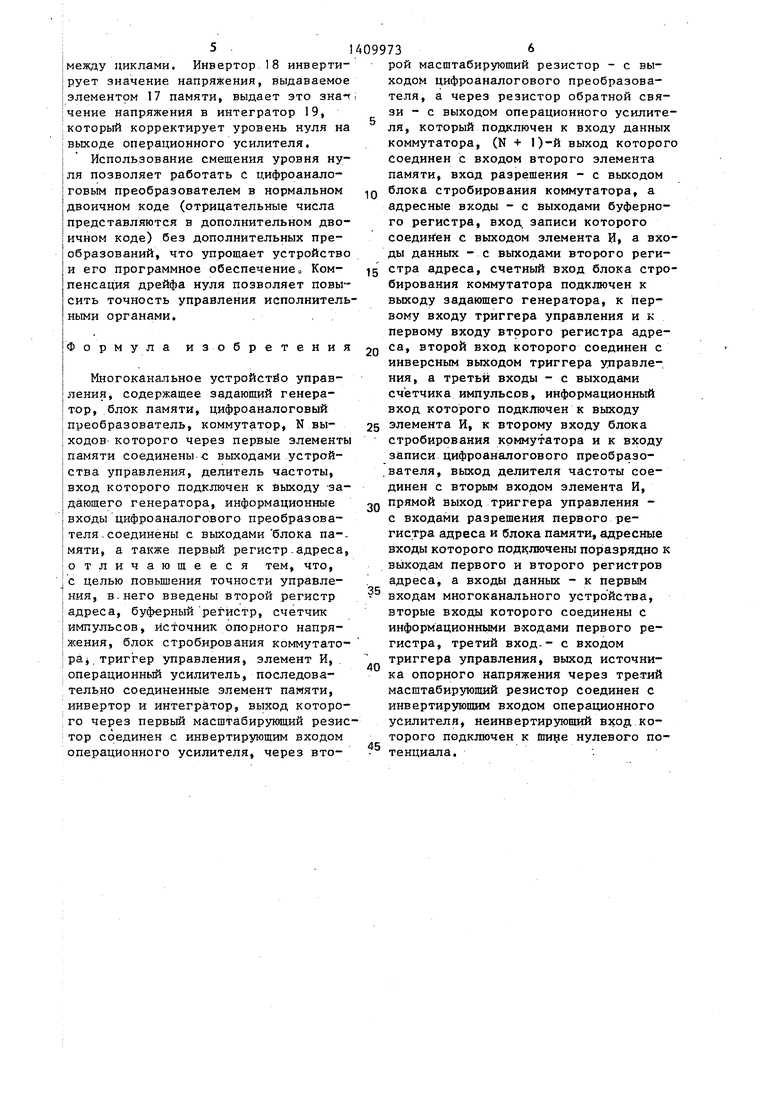

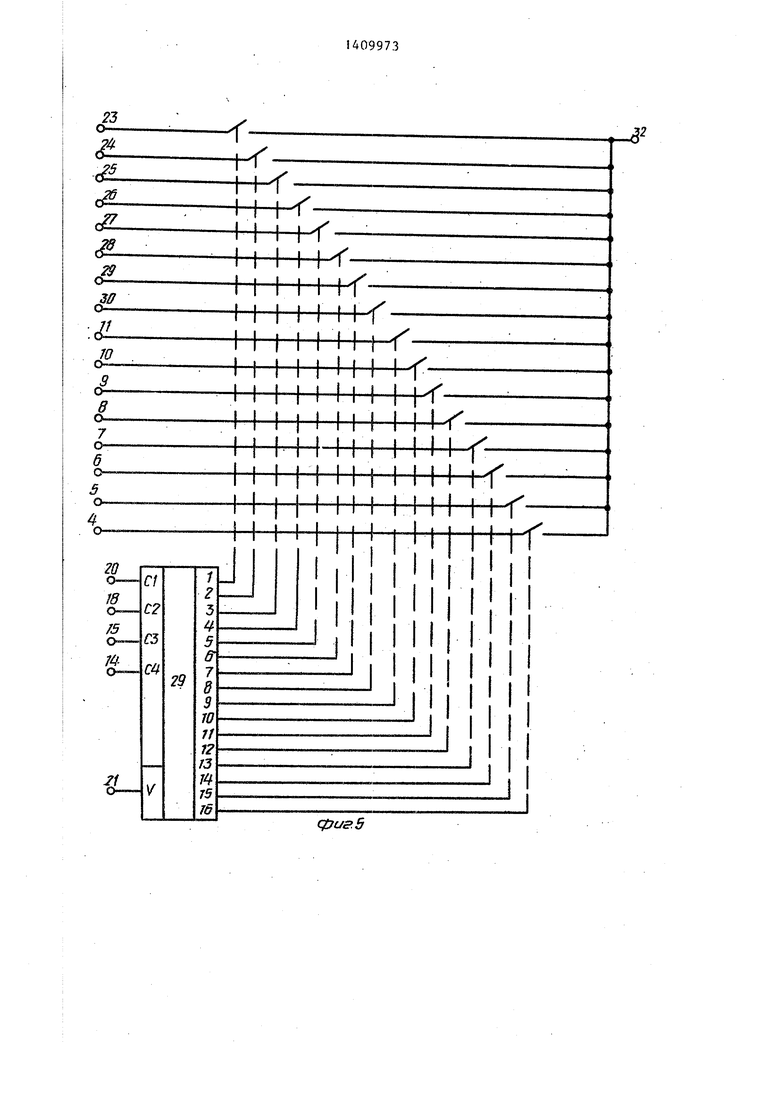

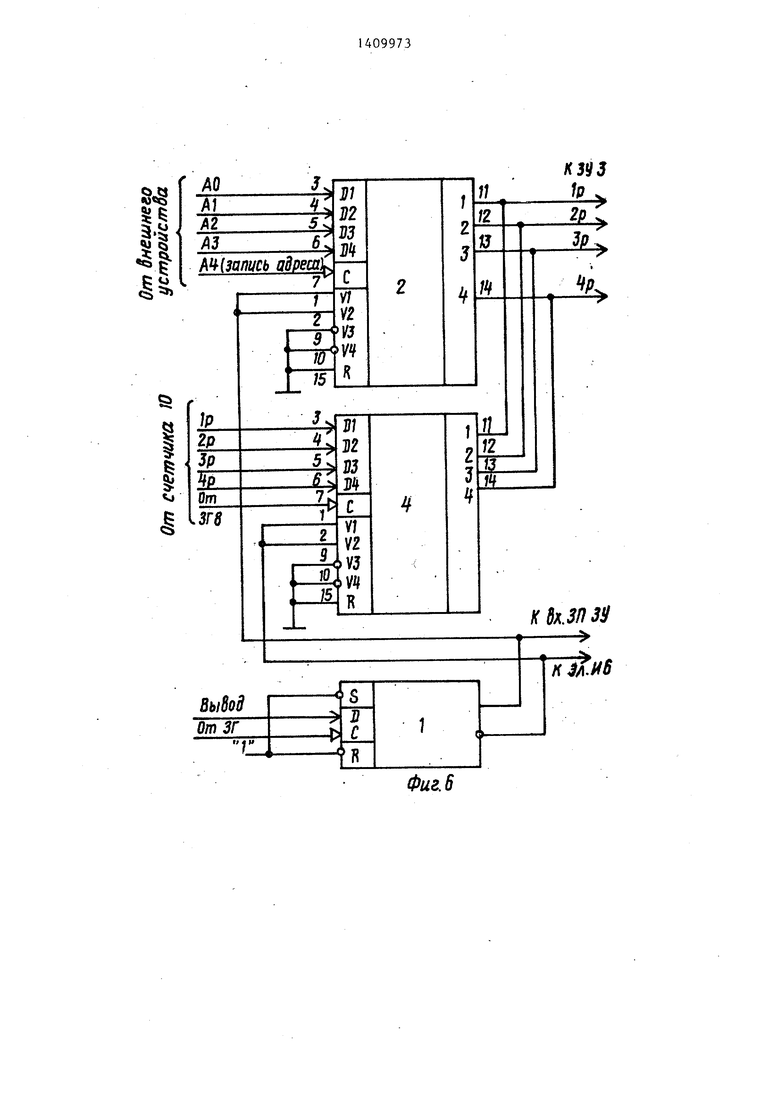

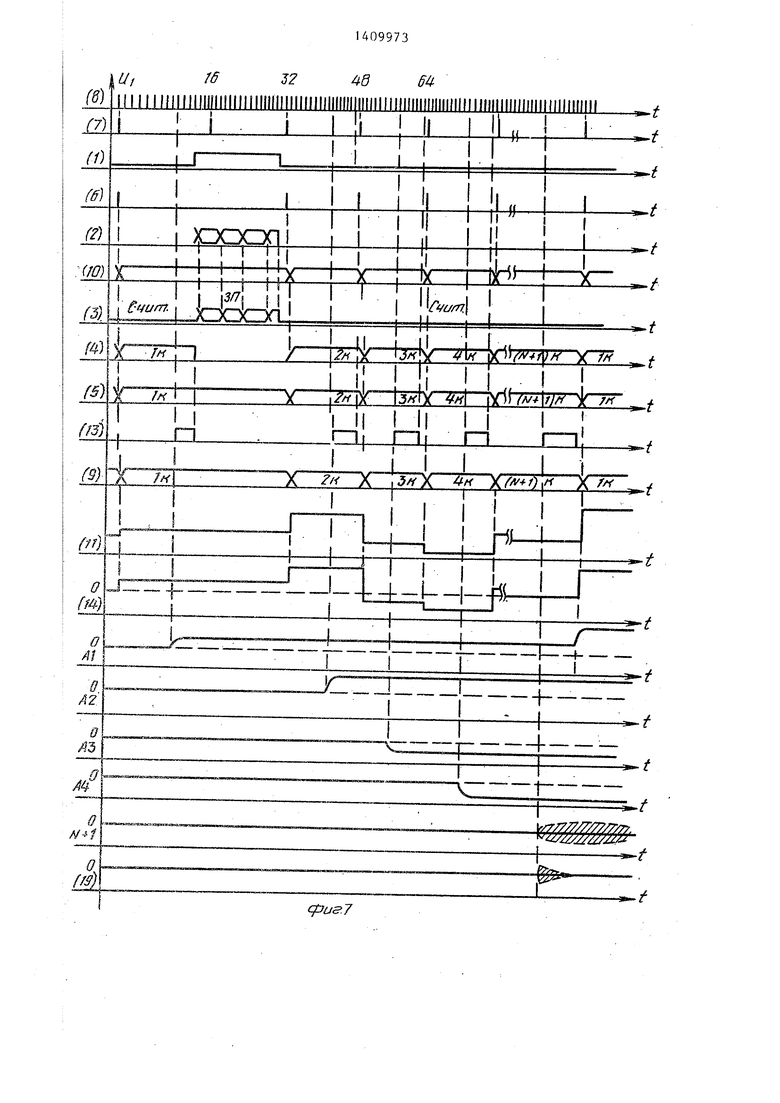

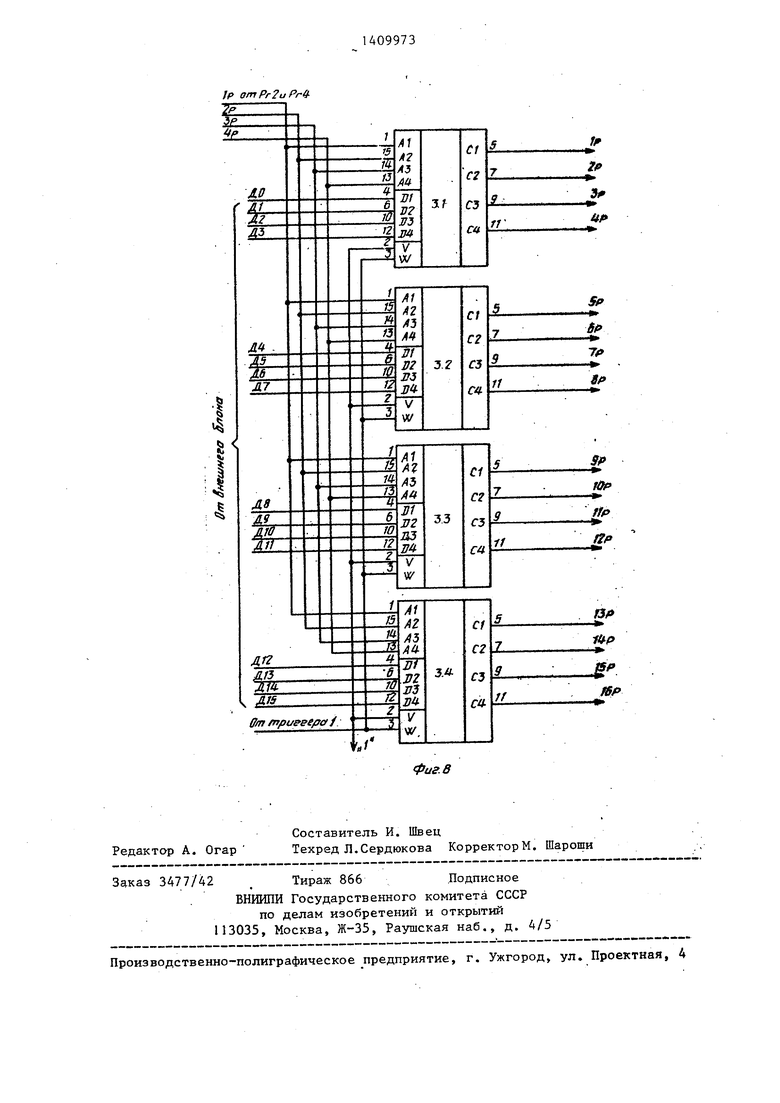

На фиг. 1 представлена функцио- нальная схема устройства; на фиг, 2- схема блока стробирования коммутатора; на фиг. 3 - временные диаграммы работы блока стробирования коммутатора; на фиг. 4 - схема элемента памя- ти; на фиг. 5 - схема коммутатора; на фиг. 6 - уточненная схема соединения первого и второго регистров и триггера управления; на фиг. 7 - временные диаграммы работы устройства; на фиг, 8 - структурная схема блока памяти.

Многоканальное устройство управления (фиг, S) содержит триггер 1 управления, первый регистр 2 адреса, блок 3 памяти, (ЗУ), второй регистр 4 адреса, буферный регистр 5, элемен И 6, делитель 7 частоты, задагоший генератор 8, регистр 9 цифроаналогово- го преобразователя, счетчик 10 им- пульсов, цифроаналоговый преобразователь 11, источник 12 опорного напряжения, блок 13 стробирования коммутатора, операционный усилитель 14, коммутатор 15, первые 16 и второй 17 элемент,ы памяти, Инвертор 18, ин- тегра тор 19, первый масштабирующий резистор 20, регистр 21 обратной связи, третий 22 и второй :23 масштабирующие резисторы.

На фиг. 2 обозначены счетчик 24, элемент И-НЕ 25 и элемент И 26, на фиг, 4 - операционный усилитель 27 и конденсатор 28, на фиг. 5 - счетчик 29.

Устройство работает следующим образом.

Триггер управления записью-считыванием по сигналу Вывод от внешнего устройства отключает выходы регистра 4 адреса сканирования от адрес- ньк входов блока 3 памяти путем перевода регистра 4 в третье состояние,- через элемент И 6 запрещает выдачу импульсов с выхода делителя частоты на счетный вход счетчика 10, на вход разрешения записи регистра 9 цифро- аналогового преобразователя, на вход буферно1-о регистра 5, а также на

Q 5 0

5 о

0 5

5

0

5

вход блока 13 стробирования коммутатора. Одновременно триггер 1 подключает выходы регистра 2 адреса записи к адресным входам блока 3 памяти и разрешает запись данных в него. Получаемые цифровые данные записываются в блок 3 памяти, хранящий указанные данные в определенных ячейках памяти, определяемых приходящим адресом (А.1...Ап) на вход регистра 2 адреса.

После окончания передачи данных в блок 3 памяти сигнал Вьш од снимается , триггер 1 разрешает прохождение импульсов через элемент И 6 на счетный вход счетчика 10, блок 13 стробирования коммутатора, буферный регистр 5, регистр 9 цифроаналогово- го преобразователя, отключает выходы адреса регистра 2 адреса записи от входов блока 3 памяти переводом его в третье состояние, запрещает запись данных и подключает выходы регистра 4 адреса к адресным входам блока памяти путем вьгоода его из третьего состояния.

Регистр 4 адреса транслирует па- ,раллельно сигналы с выходов счетчика 10 поразрядно к входам буферного регистра 5. Перевод регистра 4 адреса из состояния, когда выходы отключены от адресных входов блока 3 памяти и буферного регистра 5 (выходы регистра 4 находятся в третьем состоянии, т.е. их вькодное сопротивление велико и не мешает работать . аналогичному регистру 2 адреса записи), осуществляется, с помощью входа разрешения выборки выходов. Когда на вхо разрешения выборки выходов регистра 4 с инверсного выхода триггера 1 управления приходит высокий логический уровень, выходы регистра 4 адреса подключены, к адресным входам блока 3 памяти. Когда на вход разрешения выборки выходов регистра 4 с инверсного выхода триггера 1 управления приходит низкий логический уровень, выходное сопротивление повышается (переход в.третье состояние), а следовательно, сигналы с выхода счетчика 10 не проходят на адресные входы блока 3 памяти. В это время благодаря установке логической единицы на первом (прямом) выходе триггера 1 управления разрешена работа регистру 2 адреса записи, ко- торый вьтолнен аналогично.

Счетчик )0 импульсов последовательно выдает коды адресов, которые импульсами задающего генератора 8 записываются в регистр 4 адреса, т.е. циклический перебор адресов всех ячеек памяти блока 3 памяти.

Перезапись данных с выхода счётчика 10 в регистр 4 адреса под управлением импульсов задающего генерато- pa 8 (с частотой большей, чем частота счетных импульсов) йовьплает достоверность перезаписываемого кода в регистр 4-Многократным подтверждением кода, что повышает надежность работы устройства в целом.

По выходному адресу регистра 4 адреса из блока 3 памяти на вход регистра 9 цифроаналогового преобразователя выдаются данные в виде кода, которые записываются в регистр 9 по сигналу записи кода, сформированного путем деления частоты на шестнадцать делителем 7 и элементом И 6. Коэффициент деления делителя 7 может быть другим и определяется быстродействием цифроаналогового преобразователя 11 .

Данные с регистра 9 цифроаналогового преобразователя вьщаются в виде многоразрядного кода в цифроана- логовый преобразователь 11 для получения на его выходе постоянного напряжения, величина которого пропорциональна входному коду. Для организации биполярного управляющего напряжения выходной код регистра 9 смешен на величину, равную весу стар шего разряда кода, и соответствует результату суммирования входного числа регистра с числом, равным ве- су старшего разряда кода, а выходное напряжение операционного усилителя 14 смещено с помощью источника 12 опорного напряжения и резистор 22 на величину, компенсирующую смещение кода, поэтому входному коду нуля на регистр -9 соответствует на выходе операционного усилителя нулевое напряжение, а другим кодам - пропорциональные этим кодам напряжения с соответствующим знаком. Для получения смещенного кода достат/очно взять инверсное значение состояния старшег разряда кода в регистре 9 и прямые значения состояний младших, разрядов.

Полученное аналоговое напряжение пропорционально заданному коду подается на вход коммутатора., имеющего

20

25

Q

09973

один вход и множество выходов. Коммутатор 15 согласно приходящему адресу передает аналоговое напряжение к одному из выходных элементов 16 памяти. Задание адреса на коммутатор осуществляет буферный регистр 5 в режиме сканирования от регистра 4 адреса-сканирования по сигналу записи кода, приходящему от элемента И 6. С целью исключения записи в выходные элементы пам.яти напряжения помехи во время преобразования кода в аналоговое напряжение схема стробирова- ния коммутатора вырабатьшает импульсы, разрешающие работу.коммутатора.

Блок 13 стробирования коммутатора (фиг. 2) работает следующим образом. На вход параллельной записи счетчика 24 приходит импульс записи кода, который записывает в счетчик 24 код числа шестнадцать, и на выходе элемента И 26 присутствует нулевой потенциал. Импульсы, приходящие от задающего генератора на счетный вход счетчика 24, подсчитьтаются им, и после прохождения девятого импульса на выходе схемы стробирования устанавливается высокий логический уровень,

Когда счетчик 24 достигает до пятнадцати, на входах элемента И-НЕ 25 устанавливаются две логические единицы. В результате на выходе блока 13 стробирования устанавливается нулевой потенциал. Временные диаграммы работы блока 13 стробирования коммутатора приведены на фиг. 3,

Элемент 16 памяти выполнен на операционном усилителе 27 и конденсаторе 28 (фиг. 4). При приходе с выхода коммутатора 15 аналогового напряжения оно запоминается конденсатором 28 и через усилитель 27 выдается на управление исполнительным органом до следующего цикла обраще ния. Дополнительный выход N + 1 коммутатора, соответствующий адресу ячейки блока памяти с данными кода нуля, подключен к входу элемента 17 памяти. Элемент 17 памяти, выполненный аналогично элементу 16 памяти запоминает аналоговое напряжение - значения кода нуля с погрешностями, обусловленными температурой и вре- менньм дрейфом, которые возникают на выходе операционного усилителя 14 и коммутатора 15 на время обращения

30

35

40

45

50

5

51

между циклами. Инвертор 18 инвертирует значение напряжения, выдаваемое элементом 17 памяти, выдает это знат чение напряжения в интегратор 19, который корректирует уровень нуля на выходе операционного усилителя.

Использование смещения уровня нуля позволяет работать с цифроанало- говым преобразователем в нормальном двоичном коде (отрицательные числа представляются в дополнительном двоичном коде) без дополнительных преобразований, что упрощает устройство и его программное обеспечение Компенсация дрейфа нуля позволяет повысить точность управления исполнительными органами..

Формула изобретения

Многоканальное устройство управления, содержащее задающий генератор, блок памяти, цифроаналоговый преобразователь, коммутатор, N выходов которого через первые элементы памяти соединены с выходами устройства управления, делитель частоты, вход которого подключен к йыходу -задающего генератора, информационные входы цифроаналогового преобразователя . соединены с выходами блока па-- мяти, а также первый регистр.адреса, отличающееся тем, что, с целью повышения точности управления, В-него введены второй регистр адреса, буферный регистр, счетчик импульсов, источник опорного напряжения, блок стробирования коммутатора j. триггер управления, элемент И, операционный усилитель, последовательно соединенные элемент памяти, инвертор и интегратор, выход которого через первьш масштабирующий резистор соединен с инвертирующим входом операционного усилителя, через вто099736

рой масштабирующий резистор - с выходом цифроаналогового преобразова- теля, а через резистор обратной связи - с выходом операционного усилителя, который подключен к входу данных коммутатора, (N + 1)-й выход которого Соединен с входом второго элемента памяти, вход разрешения - с выходом

Q блока стробирования коммутатора, а адресные входы - с выходами буферного регистра, вход записи которого соединген с вьпсодом элемента И, а входы данных - с выходами второго реги 5 стра адреса, счетный вход блока стробирования коммутатора подключен к выходу задающего генератора, к первому входу триггера управления и к первому входу второго регистра адре2Q са, второй вход которого соединен с инверсным выходом триггера управления, а третьи входы - с выходами счетчика импульсов, информационный вход которого подключен к выходу

25 элемента И, к второму входу блока стробирования коммутатора и к входу записи цифроаналогового преобразо- .вателя, выход делителя частоты соединен с вторым входом элемента И,

2Q прямой выход триггера управления - с входами разрешения первого регистра адреса и блока памяти, адресные входы которого под1 лючены поразрядно к выходам первого и второго регистров адреса, а входы данных - к первым входам многоканального устро йства, вторые входы которого соединены с информационными входами первого регистра, третий вход-- с входом триггера управления, выход источника опорного напряжения через третий масщтабирующий резистор соединен с инвертирующим входом операционного усилителя, неинвертир1пощий вход которого подключен к Шщ1е нулевого пс35

40

45

тенциала.

фие.г

1 2 Ъ t 5 6 7 8 3 го Г1 1 fj Щ.

-/

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОРРЕЛЯЦИОННОЙ ФУНКЦИИ | 1992 |

|

RU2037198C1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Многоканальное устройство ввода аналоговой информации | 1986 |

|

SU1403057A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

| Многоканальное устройство ввода аналоговой информации | 1987 |

|

SU1418726A1 |

| Функциональный аналого-цифровой преобразователь | 1985 |

|

SU1260979A1 |

| Устройство для ввода информации | 1983 |

|

SU1145336A1 |

Изобретение относится к области управления и регулирования и предназначено для использования в системах число вого программного управления металлорежущими станками. Целью изобретения является повьшение точности управления. В устройство для числового программного управления, содержащее задающий генератор 8, триггер управления 1 регистр адреса 2, регистр адреса 4, блок памяти 3, регистр цифроаналогового преобразо- . .вателя 9, цифроаналоговый преобразователь 11, операционный усилитель 14, коммутатор 15, элемент памяти 17, ДО...Л15 e, число которьвс определяется количеством исполнительных органов станка, делитель частоты 7, элемент И 6, буферный регистр 5, счетчик импульсов 10, введены источник опорного напряжения 12, блок стробирования коммутатора 13, инвертор 18, интегратор 19, Кроме того, вход старшего разряда цифро- аналогового преобразователя соединен с инверсным выходом старшего разряда регистра цифроаналогового преобразователя. Взаимодействие блоков и узлов организовано таким образом, что цифровые данные, получаемые от внешнего блока, записьтаются в запоминающее устройство по ячейкам, соответствующим адресам управления по каналам А1...Ап, считьшаются под управлением регистра адреса сканирования и после преобразования в аналоговое напряжение положительной или отрицательной полярности, скорректированное по уровню нулевого значения его величины, коммутатором распределяются по своим элементам памяти, с которых происходит управление соответствуй- щим исполнительным органом станка. 8 ил. It i (Л С со со ч СО фигЛ

Sxoff

Фиг. 5

ригА

§ ,

P S

1|

CcS

V)

Фиг. 6

/4

M

(риг7

V

-fe

/77777/77/7/7У7У

W2m 22Xi .

IP o/npr2uPrf

| Цифро-аналоговый преобразователь | 1981 |

|

SU1050108A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для разматывания лент с семенами при укладке их в почву | 1922 |

|

SU56A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1988-07-15—Публикация

1986-06-13—Подача