Изобретение относится к области импульсной техники и может быть использовано для передачи сообщений в системах связи.

Известны устройства для передачи сообщений с адаптивной дискретизацией, основанные на использовании предсказателя нулевого порядка.

Целью изобретения является сокращение избыточности в исходных сообщениях при обработке участков, в пределах которых сигнал изменяется с конечной скоростью. Достигается это тем, что логический узел предлагаемого устройства выполнен с тремя входами и выходами, первый из которых подсоединен к выходу синхронизатора, второй--к выходу последовательно соединенных коммутатора и преобразователя аналог-ход и третий-к первому выходу запоминающего блока контрольных величин. Первый выход логического узла подключен к параллельно соединенным входам схемы формирования оценочных значений сигнала и схемы выдачи, второй-ко вторым входам схемы формирования оценочных значений сигнала и схемы выдачи и третий выход-к третьему входу упомянутой схемы формирования оценочных значений сигнала, два выхода которой подключены к двум входам запоминающего блока контрольных величин, а четвертый вход-ко второму выходу запоминающего блока контрольных величин.

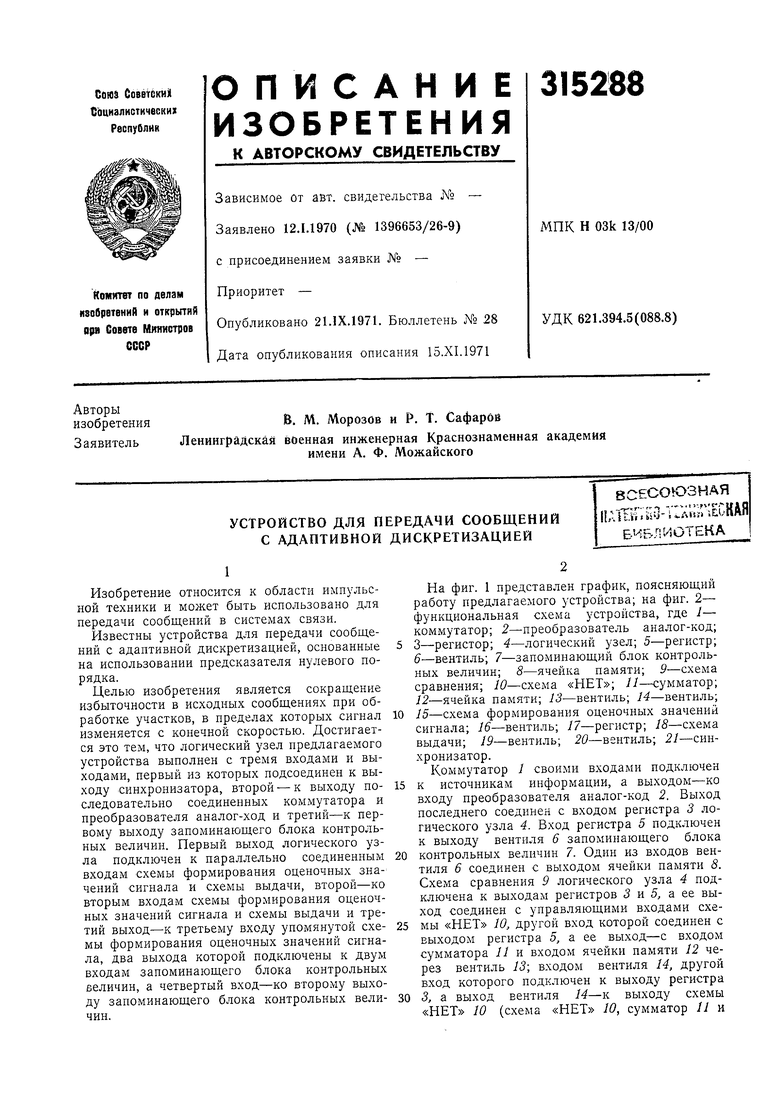

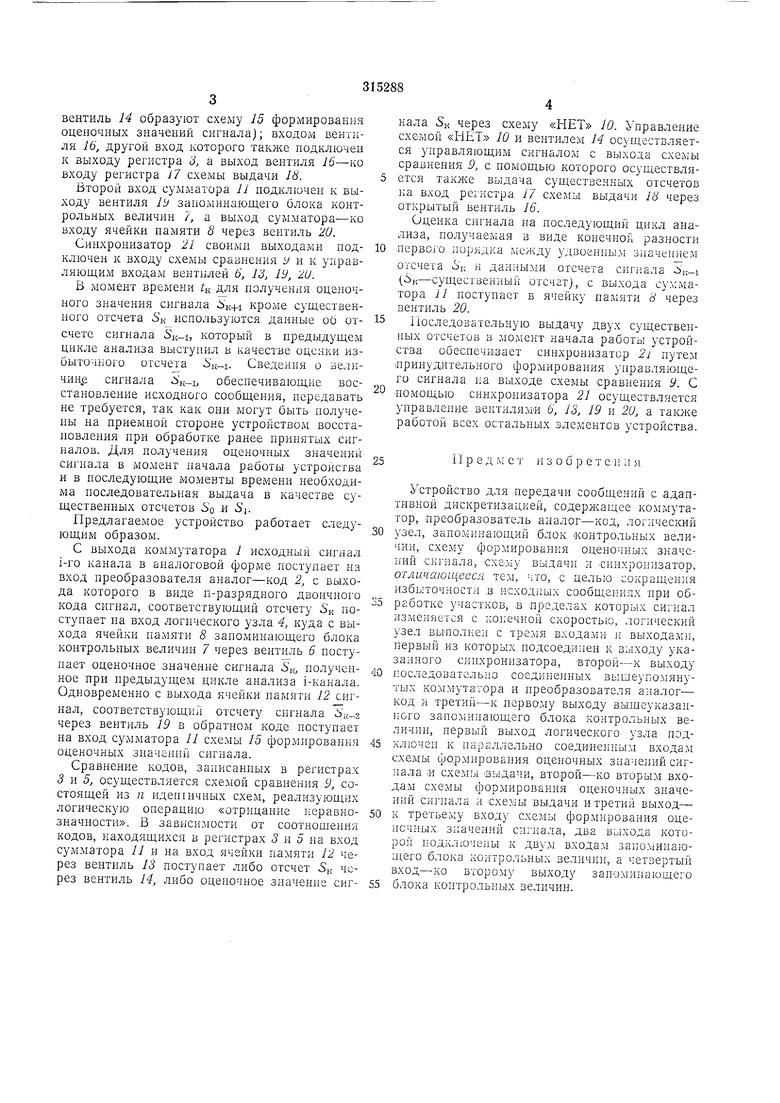

На фиг. 1 представлен график, поясняющий работу предлагаемого устройства; на фиг. 2- функциональная схема устройства, где 1- коммутатор; 2-преобразователь аналог-код;

3-регистор; 4-логический узел; 5-регистр; 6-вентиль; 7-запоминающий блок контрольных величин; 8-ячейка памяти; 9-схема сравнения; 10-схема 11-сумматор; 12-ячейка памяти; 13--вентиль; 14-вентиль;

15-схема формирования оценочных значений сигнала; 16-вентиль; 17-регистр; 18-схема выдачи; 19-вентиль; 20-вентиль; 21-синхронизатор.

Коммутатор / своими входами подключен

к источникам информации, а выходом-ко входу преобразователя аналог-код 2. Выход последнего соединен с входом регистра 3 логического узла 4. Вход регистра 5 подключен к выходу вентиля 6 запоминающего блока

контрольных величин 7. Один из входов вентиля 6 соединен с выходом ячейки памяти 8. Схема сравнения 9 логического узла 4 подключена к выходам регистров 3 и 5, а ее выход соединен с управляющими входами схемы «НЕТ 10, другой вход которой соединен с выходом регистра 5, а ее выход-с входом сумматора 11 и входом ячейки памяти 12 через вентиль 13; входом вентиля 14, другой вход которого подключен к выходу регистра

вентиль 14 образуют схему 15 формирования оценочных значений сигнала); входом вентиля 16, другой вход которого также подключен к выходу регистра 3, а выход веитиля 16--ко входу регистра Г/ схемы выдачи 18.

Второй вход сумматора 11 подключен к выходу вентиля УУ запоминающего блока контрольных величин 7, а выход сумматора-ко входу ячейки памяти 8 через вентиль 20.

Синхронизатор 21 своими выходами подключен к входу схемы сравнения У и к управляющим входам веитилей 6, 13, 19, 2U.

В молмент времени IK для нолучеиия оценочного значения сигнала 5к+1 кроме существенного отсчета 5к используются данные об отсчете сигнала 5к-1, который в предыдущем цикле анализа выступил в качестве оценки избыточного отсчета -Ьк-. Сведения о величин е сигнала бк-ь обеспечивающие восстановление исходного сообщения, передавать не требуется, так как они могут быть получены на приемной стороне устройством восстановления при обработке ранее принятых сигналов. Для получения оценочных значений сигнала в молшнт начала работы устройства и в последующие моменты времени необходима последовательная выдача в качестве существенных отсчетов 5о и Si.

Предлагаемое устройство работает следующим образом.

С выхода коммутатора 1 исходный сигнал i-ro канала в аналоговой форме поступает на вход преобразователя аналог-код 2, с выхода которого в виде п-разрядного двоичного кода сигнал, соответствующий отсчету 5к поступает на вход логического узла 4, куда с выхода ячейки памяти 8 запоминающего блока коптрольпых величин 7 через вентиль 6 поступает оценочное значение сигнала SK полученное при предыдущем цикле анализа i-канала. Одновременно с выхода ячейки памяти 12 сигнал, соответствующи отсчету сигнала через вентиль 19 в обратном коде поступает на вход сумматора // схемы 15 формирования оценочных значений сигнала.

Сравнение кодов, записаниых в регистрах 3 и 5, осуществляется схемой сравнения 9, состоящей из п идентичных схем, реализующих логическую операцию «отрицапие неравнозначности. В зависи.лшсти от соотнощения кодов, находящихся в регистрах 3 и 5 па вход сумматора 11 и на вход ячейки памяти 12 через вентиль 13 поступает либо отсчет SK через вентиль 14, либо оценочное значение сигнала SK через схему «НЕТ 10. Управление схе.мой «НЕТ 10 и вентилем 14 осуществляется управляющим сигналом с выхода схемы сравнения 9, с помощью которого осуществляется также выдача суп1ественных отсчетов на вход регистра 17 схемы выдачи 18 через открытый вентиль 16.

Оценка сигнала на последующий цикл анализа, получаемая в виде конечной разности

первого порядка между удвоенным значением отсчета бк и данными отсчета сиг1- ала (6к-существенный отсчет), с выхода сумматора 11 поступает в ячейку памяти 8 через вентиль 20.

Последовательную выдачу двух существенных отсчетов в момент начала работы устройства обеспечивает синхронизатор 2i путем ирииудительного формироваиия управляющего сигнала на выходе схемы сравнения 9. С

номощью синхронизатора 21 осуществляется управлеиие вентилями 6, 13, 19 и 20, а также работой всех остальных зле.ментов устройства.

Пр

:ет изооретения

Устройство для передачи сообщений с адаптивной дискретизацией, содержащее коммутатор, преобразователь аналог-код, логический

узел, запоминающий блок -контрольных величин, схему формирования оценочных значений сигнала, схему выдачи и синхронизатор, отличающеес.ч тем, что, с целью сокращения избыточности ,в исходных сообщениях при обработке участков, в пределах которых сигнал изменяется с тсоиечной скоростью, логический узел выполнен с тремя входами к выходами, первый из которых подсоединен к выходу указанного синхронизатора, второй-к выходу

последовательно соединенных вышеупомянутых коммутатора и нреобразователя аналог- код и третий-к нервому выходу выщеуказаппого запоминающего блока контрольных величии, первый выход логического узла подключей к параллельно соединепны.м входам схемы формирования оценочных зпачений сигнала и схемы Выдачи, второй-ко вторым входам схемы формирования оценочных значений сигнала и схемы выдачр и третий выход-

к третьему входу схе.мы формирования оценочных зиачепий сигнала, два выхода которой подкл;очепы к дву.л входам запоминающего блока контрольных величин, а четвертый вход-ко второму выходу заномипающего

блока коптрольпых величи}.

sai

,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сжатия сообщений | 1972 |

|

SU473308A1 |

| УСТРОЙСТВО для СЖАТИЯ СООБЩЕНИЙ | 1973 |

|

SU365847A1 |

| Устройство для передачи сообщений со сжатием данных | 1977 |

|

SU748485A1 |

| Устройство для передачи сообщений с адаптивной диксретизацией | 1976 |

|

SU640444A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Устройство передачи данных | 1977 |

|

SU634459A2 |

1 L

Даты

1971-01-01—Публикация