Изобретение может быть использовано в системах связи и передачи данных.

Известно устройство сжатия сообщений, передаваемых в присутствии помех при ограниченных априорных сведениях о сигнале и помехах, содержащее схемы вычисления характеристик помех и оценки интервалов корреляции входных сигналов, входы которых соединены параллельно и подключены к выходу коммутатора, а выходы - к соответствующим входам вычислительного блока, первый выход которого через сумматор подключен к первому входу логического блока, ко второму входу которого подключен выход первой ячейки памяти, вход которой соединен параллельно со входом регистра выдачи и подключен к выходу логического блока, причем выход второй ячейки памяти подключен ко входу вентиля, управляющий вход которого подключен ко второму выходу вычислительного блока.

Однако при сжатии сообщений от многоканального источника в запоминающем блоке контрольных величин для каждого i-того канала требуется выделять ( ячеек памяти, из которых N{ ячеек используются для хранения предыдущих отсчетов 5ft; (, 2, ..., Лг). Максимальное значение Ni

определяется предельными характеристиками сигналов и помех.

Цель изобретения - упрощение устройства. Предлагаемое устройство отличается тем,

что первый выход вычислительного блока подключен ко входу сумматора через схему умножения, ко второму входу которой подключен выход коммутатора, а к третьему входу - выход вентиля; при этом выход сумматора подключен ко входу второй ячейки памяти.

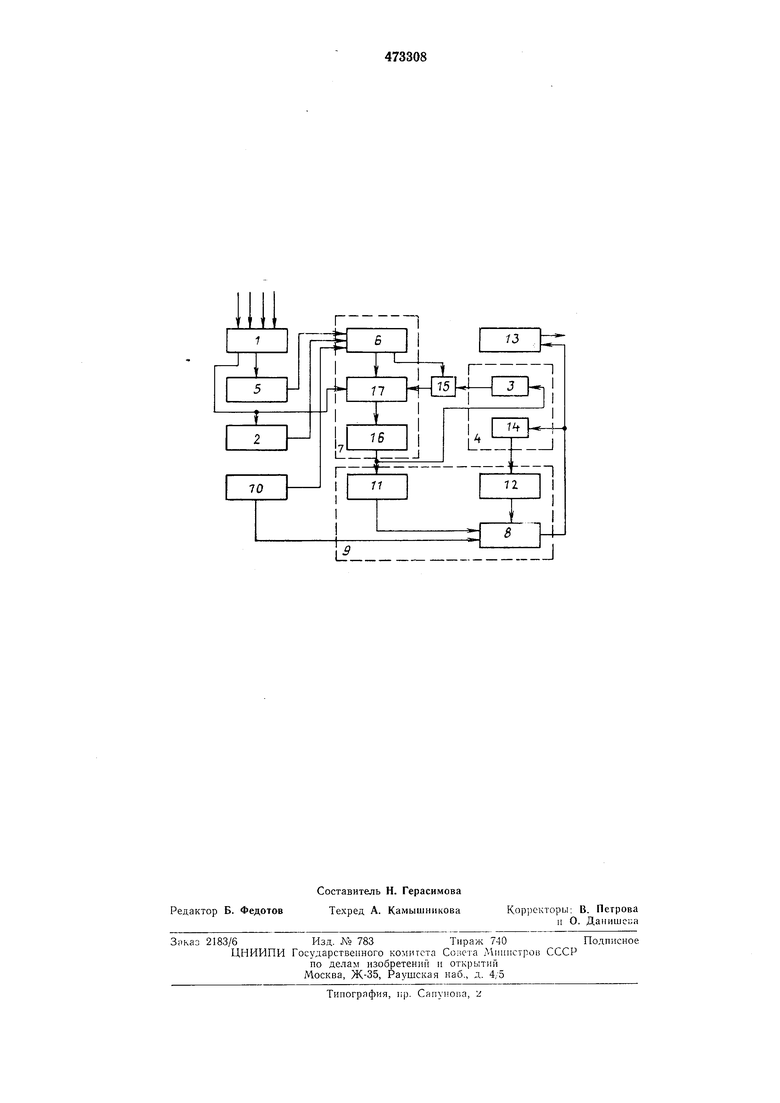

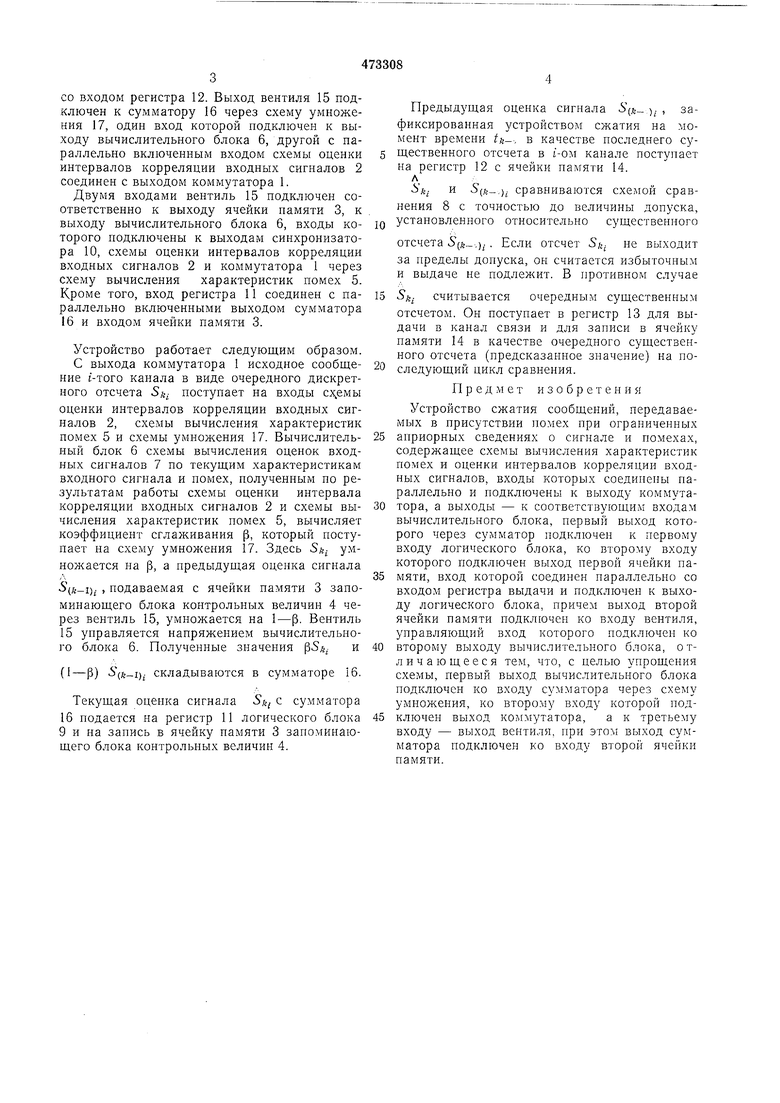

Па чертеже показана функциональная с.хема описываемого устройства.

Коммутатор 1 входами подключен к источникам сообщений, а одним выходом - ко входу схемы оценки интервалов корреляции входных сигналов 2. Вход ячейки памяти 3 (вторая ячейка памяти) запоминающего блока контрольных величин 4 и выход схемы

вычисления характеристик помех 5 подключены к соответствующим выходу и входу вычислительного блока 6 схемы вычисления оценок входных сигналов 7. Схема сравнения 8 логического блока 9 одним входом подключена к выходу синхронизатора 10, другим - к выходу регистра И, третьим - к выходу регистра 12, а выходом - ко входам регистра выдачи 13 и ячейки памяти 14 (первая ячейка памяти), выход которой соединен со входом регистра 12. Выход вентиля 15 подключен к сумматору 16 через схему умножения 17, один вход которой подключен к выходу вычислительного блока 6, другой с параллельно включенным входом схемы оценки интервалов корреляции входных сигналов 2 соединен с выходом коммутатора 1. Двумя входами вентиль 15 подключен соответственно к выходу ячейки памяти 3, к выходу вычислительного блока 6, входы ко- ю торого подключены к выходам синхронизатора 10, схемы оценки интервалов корреляции входных сигналов 2 и коммутатора 1 через схему вычисления характеристик помех 5. Кроме того, вход регистра 11 соединен с па- 15 раллельно включенными выходом сумматора 16 и входом ячейки памяти 3. Устроиство работает следующим образом. С выхода коммутатора 1 исходное сообще- 20 ние с-того канала в виде очередного дискретного отсчета S поступает на входы оценки интервалов корреляции входных сигналов 2, схемы вычисления характеристик помех 5 и схемы умнол ения 17. Вычислитель- 25 ный блок 6 схемы вычисления оценок входных сигналов 7 по текущим характеристикам входного сигнала и помех, полученным но результатам работы схемы оценки интервала корреляции входных сигналов 2 и схемы вы- 30 числения характеристик помех 5, вычисляет коэффициент сглаживания р, который поступает на схему умножения 17. Здесь 5й у.множается на р, а предыдущая оценка сигнала S(k-i)f , подаваемая с ячейки памяти 3 запоминающего блока контрольных величин 4 через вентиль 15, умножается на 1-р. Вентиль 15 унравляется напряжением вычислительного блока 6. Полученные значения pS и (1-р) ); складываются в сумматоре 16. Текущая оценка сигнала с сумматора 16 подается на регистр 11 логического блока 45 9 и на запись в ячейку памяти 3 запоминающего блока контрольных величин 4. 5 35 40 Предыдущая оценка сигнала (k , зафиксированная устройством сжатия на момент времени , в качестве последнего существенного отсчета в f-OM канале поступает на регистр 12 с ячейки памяти 14. Ski -(й- )( сравниваются схемой сравнения 8 с точностью до величины допуска, установленного относительно существенного отсчета 5(&,,).. Если отсчет 5,, не выходит за пределы допуска, он считается избыточным и выдаче не подлежит. В противном случае 5 считывается очередным существенным отсчетом. Оп поступает в регистр 13 для выдачи в канал связи и для записи в ячейку памяти 14 в качестве очередного существеп„ого отсчета (предсказанное значение) на последующий никл сравнения, Предмет изобретения Устройство сжатия сообщений, передаваемых в присутствии помех при ограниченных априорных сведениях о сигнале и помехах, содержащее схемы вычисления характеристик помех и оценки интервалов корреляции входных сигналов, входы которых соединены нараллельно и подключены к выходу коммутатора, а выходы - к соответствующим входам вычислительного блока, первый выход которого через сумматор подключен к первому входу логического блока, ко второму входу которого подключен ВЕЯХОД первой ячейки памяти, вход которой соединен параллельно со входом регистра выдачи и подключен к выходу логического блока, причем выход второй ячейки памяти подключен ко входу вентиля, управляющий вход которого подключен ко второму выходу вычислительного блока, отличающееся тем, что, с целью упрощения схемы, первый выход вычислительного блока подключен ко входу сумматора через схему умножения, ко второму входу которой подключей выход коммутатора, а к третьему входу - выход вентиля, при этом выход сумматора подключен ко входу второй ячейки памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для СЖАТИЯ СООБЩЕНИЙ | 1973 |

|

SU365847A1 |

| Устройство для передачи сообщений со сжатием данных | 1977 |

|

SU748485A1 |

| УСТРОЙСТВО для ПЕРЕДАЧИ СООБЩЕНИЙ С АДАПТИВНОЙ ДИСКРЕТИЗАЦИЕЙ8СЕСОК>&ЗНАЯ1!ДТЕй7КО-Т1лКгГ1ЕСКАЯБИБЛИОТЕКА | 1971 |

|

SU315288A1 |

| Цифровой коррелятор | 1976 |

|

SU610117A1 |

| Цифровой измеритель коэффициента корреляции случайного сигнала | 2020 |

|

RU2747725C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460224C1 |

| Устройство компенсации влияния эксцентриситета прокатных валков на прокатываемую полосу | 1982 |

|

SU1041187A1 |

| Групповой приемник сигналов управления и взаимодействия с адаптивной дифференциальной импульсно-кодовой модуляцией | 1991 |

|

SU1829126A1 |

| Устройство для оценки параметров многолучевого канала связи | 1991 |

|

SU1781828A1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

Авторы

Даты

1975-06-05—Публикация

1972-08-02—Подача