Изобретение относится к области вычислительной техники и может быть использовано при проектировании внешних устройств цифровых- вычислительных машин, имеющих буферное запоминающее устройство.

В настоящее время внешние устройства вычислительной техники имеют буферные запоминающие устройства, запись и считывание информации в которых осуществляются в параллельном посимвольном коде, когда каждому символу информации отводится адресная ячейка памяти. Применение буферных запоминающих устройств с параллельным посимвольным хранением информации вызвано экономичностью построения адресной системы при использовании принципа выборки «совпадением полутоков и схемы записи считывания информации при малом количестве разрядов символа. При считывании информации с буферного запоминающего устройства в некоторых случаях приходится формировать строку (позицию) информации, в которую входит информация одного разряда всех символов. Сформированная строка информации при помощи усилителей включает электромагниты печати или перфорации. Для контроля хранения информации в буферном запоминающем устройстве используются схемы контроля символа считанной информации по нечету. Контроль по нечету осуществляется

при помощи регистра считанного символа с дешифратором четности, выходы которого объединяются сборкой. Для возможности контроля информации по нечету код символа имеет избыточный контрольный разряд, дополняющий количество единиц в коде символа до нечетного.

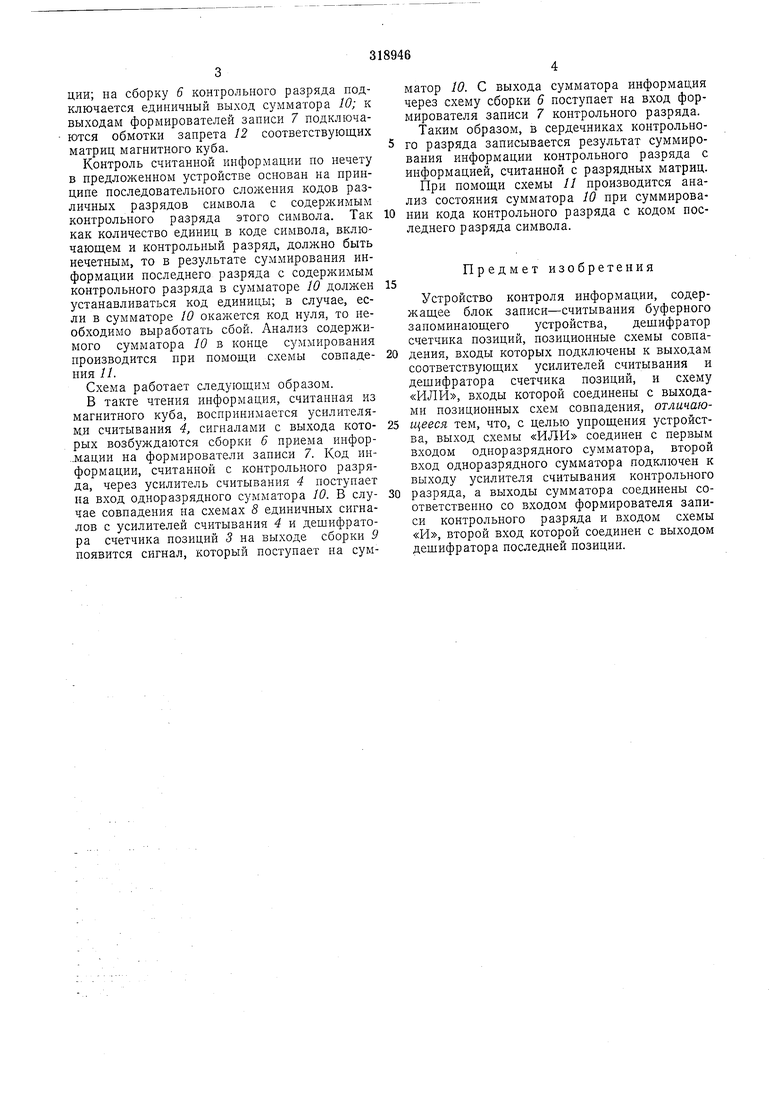

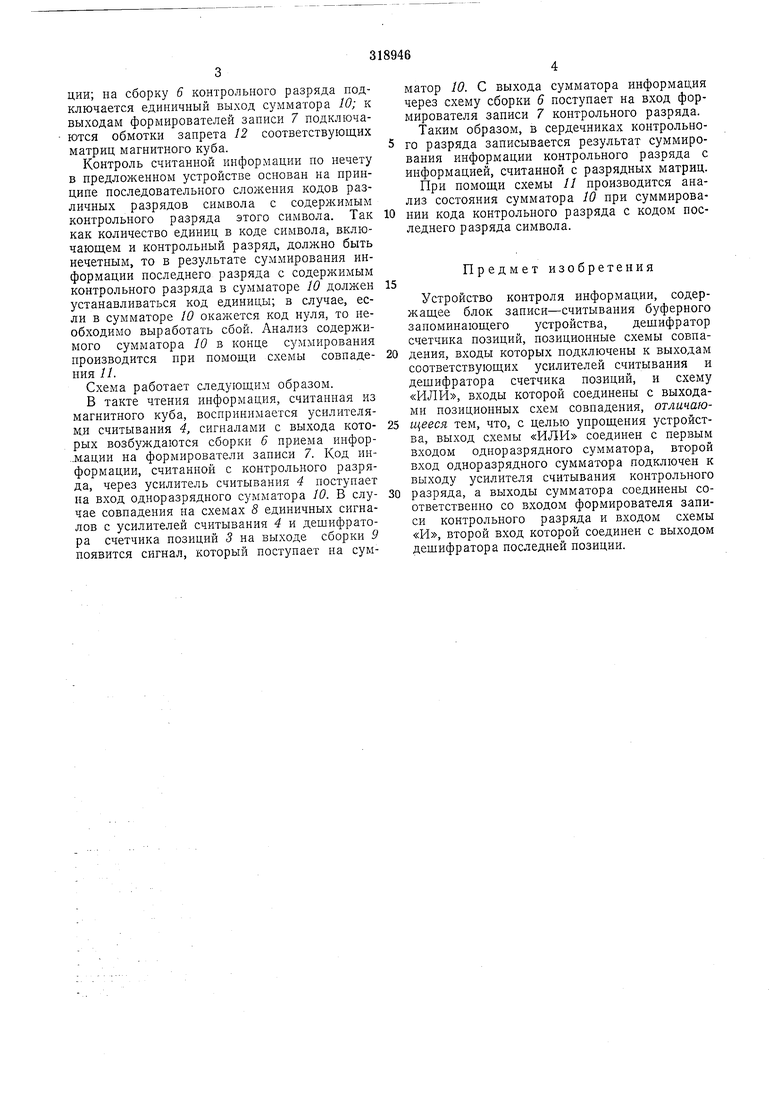

На чертеже изображена блок-схема предложенного устройства контроля информации.

Для упрощения чертежа представлена схема чтения записи четырехразрядного буферного запоминающего устройства.

На схеме изображены: счетчик позиций, состоящий из триггеров 1, 2, выходы которых

соединяются со входами дешифратора счетчика позиций 3; усилители считывания 4, входы которых соединены с обмотками считывания 5 матриц магнитного куба, выходы усилителей считывания соединяются со входами

сборки 6 формирователей записи 7 и со входами позиционных схем совпадения 8, на вторые входы которых подаются соответствующие выходы дешифратора позиций 3; выходы позиционных схем совпадения 5 объединяются при помощи сборки 9; одноразрядный сумматор 10, входы которого соединяются с выходом сборки 9 и выходом усилителя 4 контрольного разряда; схема совпадения //, фиксирующая сбой, входы схемы 11 соединяются

ции; на сборку 6 контрольного разряда подключается единичный выход сумматора 10; к выходам формнрователей записи 7 подключаются обмотки запрета 12 соответствующих матриц магнитного куба.

Контроль считанной информапии по нечету в предложенном устройстве основан на принципе последовательного сложения кодов различных разрядов символа с содерн имым контрольного разряда этого символа. Так как количество единиц в коде символа, включающем и контрольный разряд, должно быть нечетным, то в результате суммирования информации последнего разряда с содержимым контрольного разряда в сумматоре 10 должен устанавливаться код единицы; в случае, если в сумматоре 10 окажется код нуля, то необходимо выработать сбой. Анализ содержимого сумматора 10 в конце суммирования производится при помощи схемы совпадения 11.

Схема работает следующим образом.

В такте чтения информация, считанная из магнитного куба, воспринимается усилителямл считывания 4, сигналами с выхода которых возбуждаются сборки 6 приема инфор..мации на формирователи записи 7. Код информации, считанной с контрольного разряда, через усилитель считывания 4 поступает на вход одноразрядного сумматора 10. В случае совпадения на схемах 8 единичных сигналов с усилителей считывания 4 и дешифратора счетчика позиций 3 на выходе сборки 9 появится сигнал, который поступает на сумматор 10. С выхода сумматора информация через схему сборки 6 поступает на вход формирователя записи 7 контрольного разряда.

Таким образом, в сердечниках контрольного разряда записывается результат суммирования информации контрольного разряда с информацией, считанной с разрядных матриц.

При помощи схемы // производится анализ состояния сумматора 10 при суммироваНИИ кода контрольного разряда с кодом последнего разряда символа.

Предмет изобретения

15

Устройство контроля информации, содерл ащее блок записи-считывания буферного запоминающего устройства, дещифратор счетчика позиций, позиционные схемы совпадения, входы которых подключены к выходам соответствующих усилителей считывания и дешифратора счетчика позиций, и схему «ИЛИ, входы которой соединены с выходами позиционных схем совпадения, отличающееся тем, что, с целью упрощения устройства, выход схемы «ИЛИ соединен с первым входом одноразрядного сумматора, второй вход одноразрядного сумматора подключен к выходу усилителя считывания контрольного

разряда, а выходы сумматора соединены соответственно со входом формирователя записи контрольного разряда и входом схемы «И, второй вход которой соединен с выходом дешифратора последней позиции.

(Т(П:

1

HV

L)

HJ-U

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Устройство для контроля информации | 1972 |

|

SU474824A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1969 |

|

SU255993A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Устройство передачи информации | 1970 |

|

SU578648A1 |

| Устройство для поиска данных | 1990 |

|

SU1795447A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО для ПЕРЕРАБОТКИ ЧИСЛОВОЙ И БУКВЕННОЙ ИНФОРМАЦИИ | 1969 |

|

SU255656A1 |

Даты

1971-01-01—Публикация