Изобретение относится к области вычислительной техники, в частности к структуре цифровых вычислительных машин, использующих проблемно-ориентированные алгоритмические языки.

Известно вычислительное устройство для переработки числовой и буквенной информации в машине с высоким уровнем интерпретации проблемно-ориентированных алгоритмических языков, содержащее сумматор, буферный И сдвигающий регистры, регистр результата и блок управления.

Предлагаемое устройство отличается от известных тем, что оно содержит регистр типов операндов, входные цепи которого связаны с центральным устройством управления, а выходные - с местным блоком управления автоматического преобразования типов операндов и образования jwua результата; автомат образования и запоминания переносов для выполнения сложения над компонентами операндов повышенной разрядности, входные цепи которого подключены к старшему разряду, а выходные - к младшему разряду сумматора мантисс; автомат управления размещением операндов .в регистрах арифметического устройства, входные цепи которого связаны с центральным устройством управления, а выходные - с блоком управления; счетчик управления строчно-кодовыми операциями,

причем входные цепи последнего подключены через коммутирующие цепи блока управления при выполнении операций обращения к полям строк и кодов и к буферному регистру, выходные цепи счетчика управления соединены с блоком местного управления; схему сравнения, входные цепи которой соединены с регистром порядков, а выходные цепи - с блоком управления; блок инверторов для передачи прямого, обратного и сдвинутого кода второго операнда на сумматор, причем его входные цепи связаны с выходами триггеров регистра второго операнда, а выходные цепи - со входами сумматора; блок дополнительных триггеров знаков операндов и знака результата, соединенный с регистром операндов.

Это позволяет выполнять введенные для упрощения программирования и повышения

эффективности интерпретации операций над кодами, строками, целыми, действительными и комплексными числами, при любом сочетании этих операндов, включая действительные и комплексные числа произвольной длины, а

также получать при этом высокое быстродействие и максимально использовать оборудование.

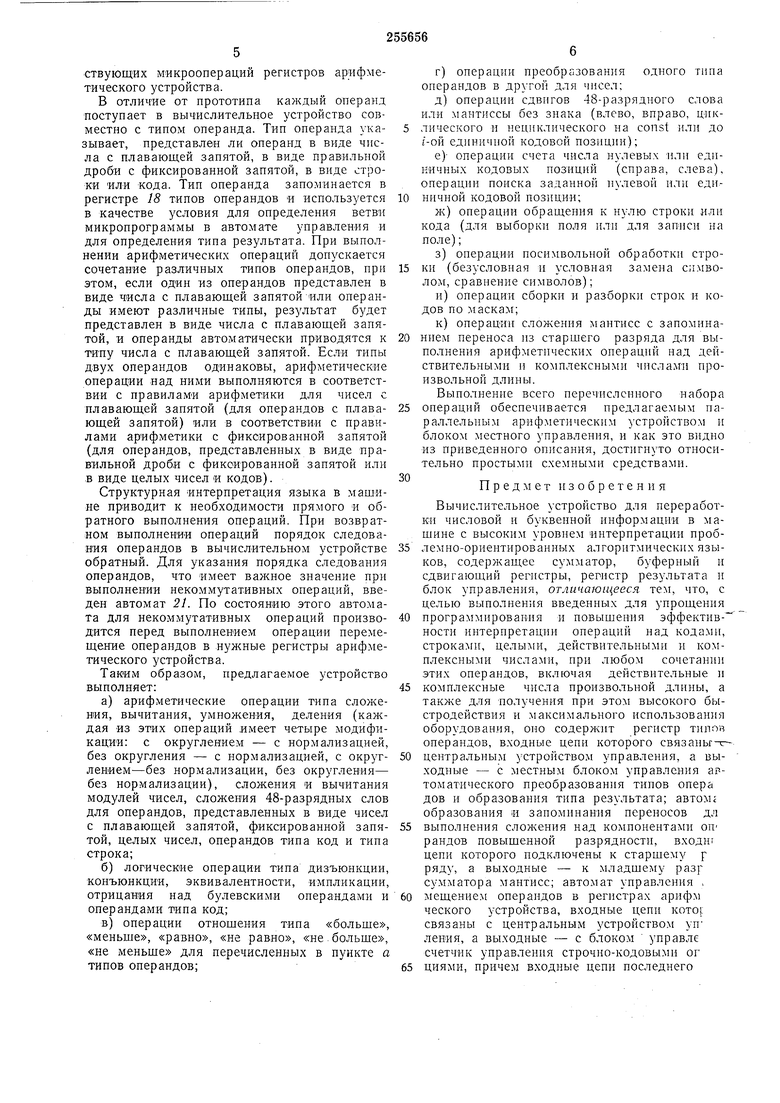

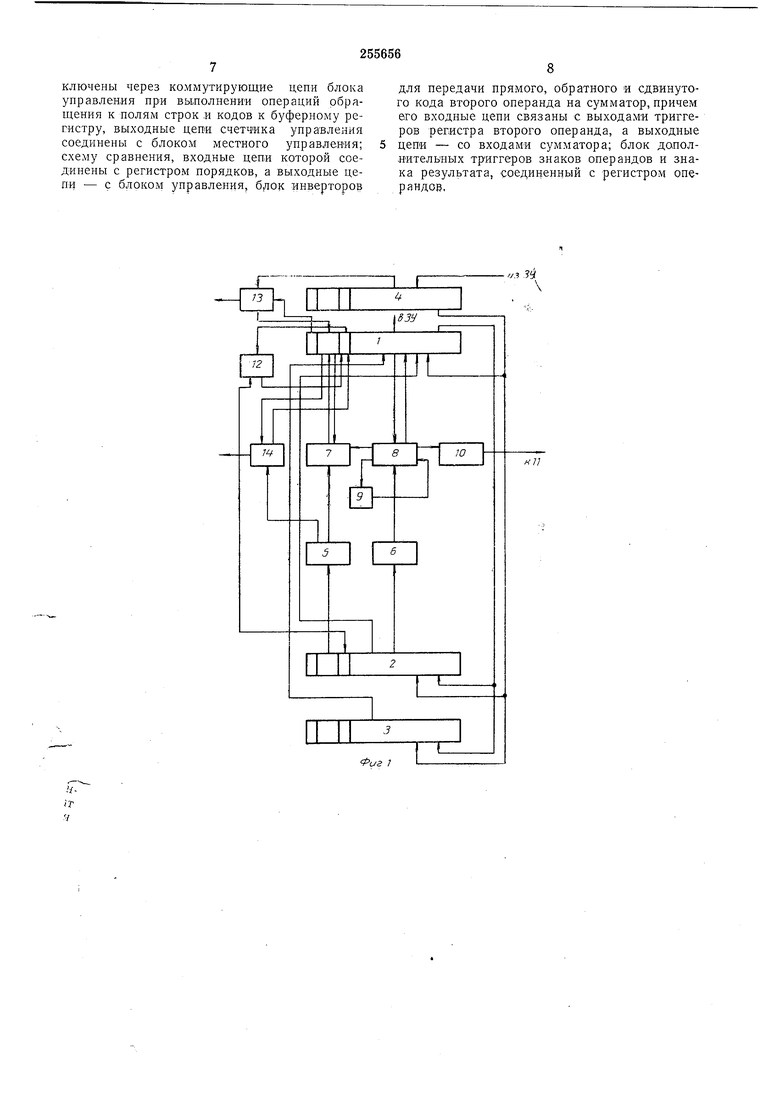

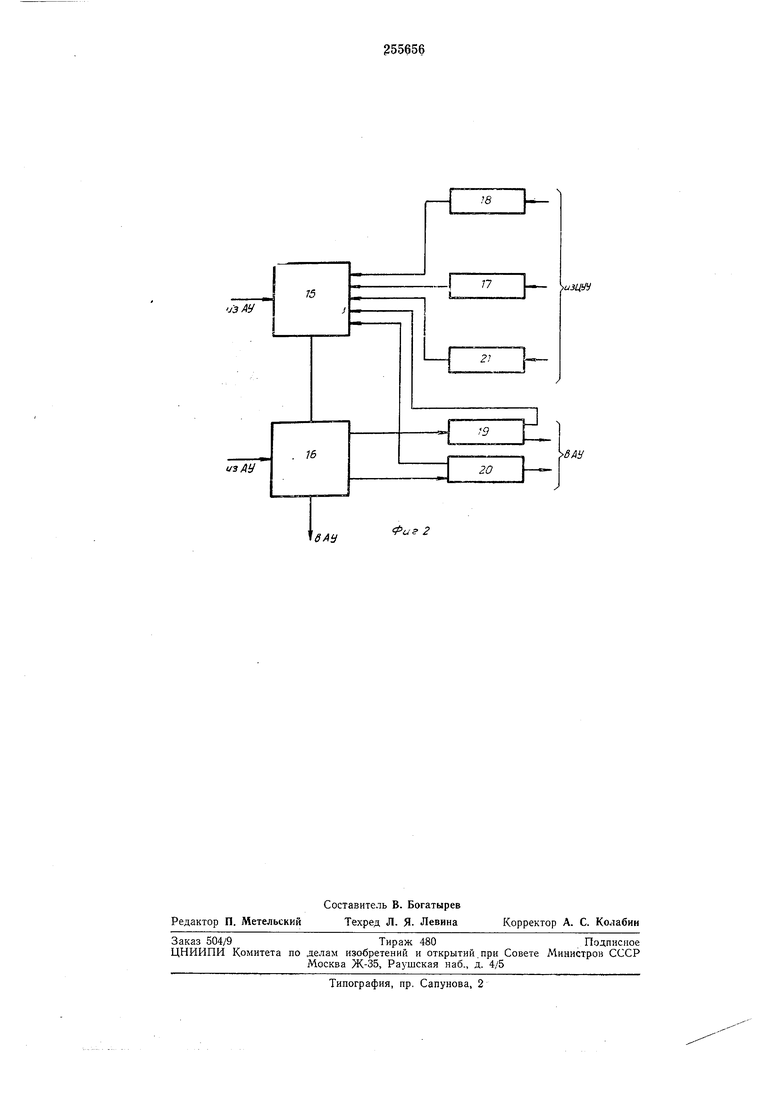

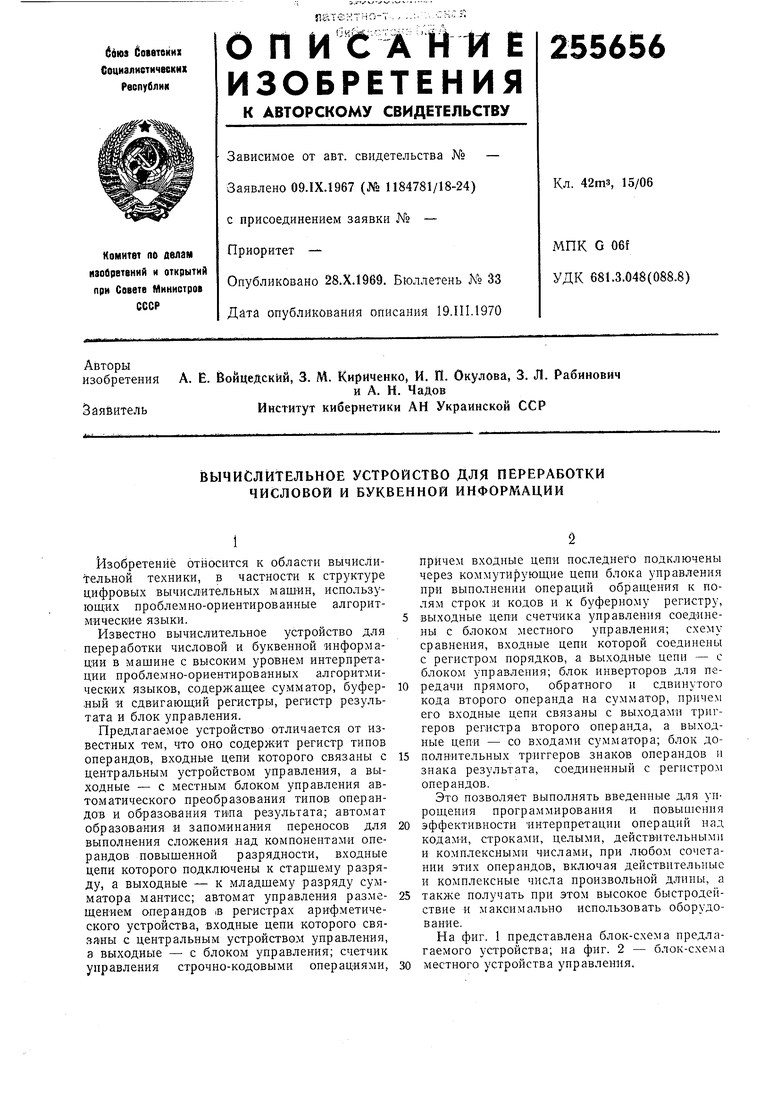

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - блок-схема Устройство состоит из трех 48-разрядных сдвигающих регистров / 2 и 5 и буферного регистра 4 совмещения выполнения заданной операции в вычислительном устройстве с выборкой нового операнда из ЗУ. Регистр 1 является регистром результата и выходными щинами связан с ЗУ. Все регистры связаны между собой для передачи операндов из одного регистра в другой. Регистры У и 5 связаны общими цепями сдвига, объединяющими их в один 96-разрядный регистр для выполнения операций сдвига 48-разрядного слова с сохранением разрядов, вышедших за пределы разрядной сетки, и для выполнения операции лад строками и кодами в случаях, когда поле строки или кода располагается в двух ячейках памяти. Порядки операндов, представленных в виде чисел с плавающей запятой, располагаются в 8 разрядах регистров (8-й разряд - знак порядка), в остальных 40 разрядах расположены мантиссы операндов (40-й разряд - знак мантиссы). Операнды, представленные в виде правильной дроби с фиксированной запятой или в виде целых чисел, располагаются в разрядах, отведенных для мантисс. Онеранды типа «строка и код занимают в регистрах вычислительного устройства 48 разрядов. Регистр 1 иепосредственно выходными шинами, а регистр 2 через блоки 5 и 6 инверторов связан с параллельным комбинационным сумматором 7 порядков, сумматором 8 мантисс. Эти два сум.матора объединяются общей цепью переносов только для выполнения обработки строк и кодов, в остальных случаях это два самостоятельных сумматора со своими ценями циклических переносов. Для разрыва цепи циклического переноса в сумматоре 8 в случае операции с повышенной точностью используется автомат 9 запоминания циклического переноса, который выходными шинами связан с младшим разрядом сумматора мантисс. Сумматоры 7 и S связаны с регистром 1 результата. Дополнительное сокращение времени суммирования в сравнении с прототипом достигнуто введением схемы-блока 10 анализа операндов. Блок 10 выходными шинами связан с блоком // местного управления для выработки сигнала окончания суммирования. Блоки 5 и 5 инверторов введены для получения прямого, обратного и сдвипутого кода операнда, расположенного в регистре 2. Выходными шинами блок инверторов связан с сумматором. Введение этого блока позволило уменьшить время суммирования за счет отсутствия дополнительного времени на инзертирование кода второго операнда и за счет освобождения входов сумматора, которые используются для организации схемы ускорения переносов. Сдвинутый код второго операнда, получаемый в блоке 6, используется для ускорения операции умножения (умножение производится начиная с младших разрядов множителя, с анализом двух разрядов множителя, с прибавлением прямого, обратного или прямого сдвинутого кода множимого к частичным произведениям и сдвигом множителя на два разряда). Арифметические операции производятся над операндами без знаков (знаковые разряды регистров 1, 2 W. 4 перед выполиением арифметических операций устанавливаются в нулевое состояние). Знаки операндов запомипаются в блоке 12, в этом же блоке образуется зпак результата арифметических операций, который передается в знаковый разряд регистра результата после выполнения операции. Введение этого блока позволило при выполнении арифметических операций использовать обратый код только второго операнда независимо от знака первого операнда. При сложении и вычитании обратный код второго операнда используется, если сумма по mod 2 знаков двух операндов-слагаемых равна единице (операции вычитания заменены операцией сложения уменьшаемого с вычитаемым, знак которого изменяется на противоположный в блоке 12). В отличие от прототипа операций обращения к нулю строки или кода и операции посимвольной обработки строк осуществляются на блоках вычислительного устройства, перерабатывающих и числовую информацию. Операции обращения к полям строк и кодов позволяют выполнить выборку кодов или символов с ПОЛЯ цеременной или записать на поле новые значения кодовых позиций или символов. Для управления этими операциями введен счетчик 13 управления строчно-кодовыми операциями. Операции посимвольной обработки строк позволяют осуществить перемещение и замену символов в пределах строки. Обращение к полям выполняется с помощью операций линейных, циклических и посимвольных (на 8 разрядов) сдвигов, осуществляемых в числовых. регистрах устройства, где размещаются обрабатываемые коды и строки. Посимвольная обработка строк осуществляется в арифметическом устройстве 14 порядков, где производится сравнение сим1волов и в зависимости от результата сравнения выполняется замена символом обрабатываемой строки. Блок // местного управления (фиг. 2) состоит из автомата 15 управления, блока 16 микроопераций, регистра 17 операций, регистра /8 типов операндов, двух 8-разрядных Счетчиков 19 и 20. Выполнение любой операции начинается с установки триггера соответствующей опера ции в регистре операций сигналом из центрального устройства и запуска соответствующей микропрограммы автомата управления. Последовательность микроопераций, соответствующих этой микропрограмме, вырабатываствующих микроопераций регистров арифметического устройства. В отличие от прототипа каждый операнд поступает в вычислительпое устройство совместно с типом операнда. Тип операнда ука-5 зывает, представлен ли операнд в виде числа с плавающей запятой, в виде правильной дроби с фиксированной запятой, в виде строки или кода. Тип операнда запоминается в регистре 18 типов операндов и используется10 Б качестве условия для определения ветви микропрограммы в автомате управления и для определения типа результата. При выполнении арифметических операций допускается сочетание различных типов операндов, при 15 этом, если один из операндов представлен в виде числа с плавающей запятой или операиды имеют различные типы, результат будет представлен в виде числа с плавающей заиятой, и операнды автоматически приводятся к 20 тииу числа с плавающей запятой. Если типы двух операндов одинаковы, арифметические операции над ними выполняются в соответстВИИ с правилами арифметики для чисел с плавающей запятой (для операндов с плава- 25 ющей запятой) или в соответствии с правилами арифметики с фиксированной запятой (для операндов, представленных в виде правильной дроби с фиксированной запятой или В виде целых чисел и кодов).30 Структурная -интерпретация языка в мащине приводит к необходимости прямого и обратного выполнения операций. При возвратном выполнении операций порядок следования операндов в вычислительном устройстве 35 обратный. Для указания порядка следования операндов, что имеет важное значение при выполнении некоммутативных операций, введен автомат 21. По состоянию этого автомата для некоммутативных операций произво- 40 дится перед выполнением операции перемещение операндов в нужные регистры арифметического устройства. Таким образом, предлагаемое устройство выполняет; а) арифметические операции типа сложения, вычитания, умножения, деления (каждая из этих операций имеет четыре модификации; с округлением - с нормализацией. без округления - с нормализацией, с округ- 50 лением-без нормализации, без округления- без нормализации), сложения и вычитания модулей чисел, сложения 48-разрядных слов для операндов, представленных в виде чисел с плавающей запятой, фиксированной запя- 55 той, целых чисел, операндов типа код и типа строка; б)логические операции типа дизъюнкции, конъюнкции, эквивалентности, импликации, отрицания над булевскими операндами и бо операндами типа код; в)операции отношения типа «больше, «меньше, «равно, «не равно, «не.больше, «не меньше для перечисленных в пункте а типов операндов; 65 45 г)операции преобразования одного типа операндов в другой для чисел; д)операции сдвигов 48-разрядного слова или мантиссы без зиака (влево, вправо, циклического и нециклического на const или до г-ой единичной кодовой позиции); е)- операции счета числа нулевых или единичных кодовых иозиций (справа, слева), операции поиска заданной нулевой или единичной кодовой позиции; ж) операции обращения к нулю строки или кода (для выборки поля или для записи на поле); з) опер.ации пocи Lвoльиoй обработки строки (безусловиая и условная замена символом, сравнение символов); и) оиерации сборки и разборки строк и кодов по маскам; к) операции сложения мантисс с запомиианнем переноса из cTapaiero разряда для выполнения арифметических операций над действительными и комплексными числами произвольной длины. Выполнение всего перечисленного набора операций обеспечивается предлагаемым параллельным арифметическим устройством и блоком местного управления, и как это видно из приведенного описания, дост 1гнуто относительно простыми схемными средствами. Предмет изобретения Вычислительное устройство для иереработки числовой и буквенной информации в машине с высоким уровнем интерпретации проблемно-ориентированных алгоритмических языков, содержащее сумматор, буферный и сдвигающий регистры, регистр результата и блок управления, отличающееся тем, что, с целью выполнения введенных для упрощения программирования и повышения эффектив- ности интерпретации оиерации над кодами, строками, цельв и, действительными и комплексными числа: ги, при любом сочетании этих операндов, включая действительные и комплексные числа произвольной длины, а также для получения при этом высокого быстродействия и максимального использования оборудования, оно содержит регистр типов операндов, входные цепи которого связаны-сцентральным устройством управления, а выходные - с местным блоком управления артоматического преобразования типов опера дов и образования типа результата; автомг образования и запоминания переносов дл выполнения сложения над компонентами оп рандов повыщенной разрядности, входн цепи которого подключены к старшему р ряду, а выходные - к младшему разр сумматора мантисс; автомат управления , мещением операндов в регистрах арифм ческого устройства, входные цепи связаны с центральным устройством уи ления, а выходные - с блоком управле счетчик управления строчно-кодовыми ог циями, причем входные цепи последнего

ключены через коммутирующие цепи блока управления при выполнении операций обращения к полям етрок и кодов к буферному регистру, выходные цепи счетчика управления соединены с блоком местного управления; схему сравнения, входные цепи которой соединены с регистром порядков, а выходные цепи - с блоком управления, инверторов

для передачи прямого, обратного и сдвинутого кода второго операнда на сумматор, причем его входные цепи связаны с выходами триггеров регистра второго операнда, а выходные цепи - со входами сумматора; блок дополнительных триггеров знаков операндов и знака результата, соединенный с регистром операндов.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| ЦИФРОВАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1971 |

|

SU302002A1 |

| ПРОЦЕССОР С ПЛАВАЮЩЕЙ ЗАПЯТОЙ С ПОНИЖЕННОЙ ПОТРЕБЛЯЕМОЙ МОЩНОСТЬЮ ДЛЯ ВЫБИРАЕМОЙ СУБТОЧНОСТИ | 2007 |

|

RU2412462C2 |

| Арифметическое устройство для обработки комплексных чисел | 1984 |

|

SU1223249A1 |

| Арифметическое устройство | 1978 |

|

SU809169A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Устройство для суммирования чисел в дополнителььном коде с плавающей запятой | 1991 |

|

SU1833864A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО | 1972 |

|

SU429423A1 |

-{

Т

у.э ЗЛ

Фиг

SAy

иЗЦУУ

ВАУ

Фиг 2

Авторы

Даты

1969-01-01—Публикация