Изобретение относится к импульсной технике и может быть использовано для согласования вычислительных устройств с управляемыми объектами.

Известен счетчик импульсов в циклическом коде, выполненный по схеме двоичного т-разрядного счетчика с дополнительным триггером минус первого разряда.

Наличие дополнительного триггера минус первого разряда усложняет счетчики снижает его быстродействие.

Цель изобретения - упрощение счетчика и увеличение его быстродействия.

Это достигается использованием алгоритма, при котором производится поразрядное сложение ПО модулю два исходного двоичного кода с тем же «одом, но сдвинутым на один разряд влево, лричем младший разряд сдвинутого кода исключается при суммировании.

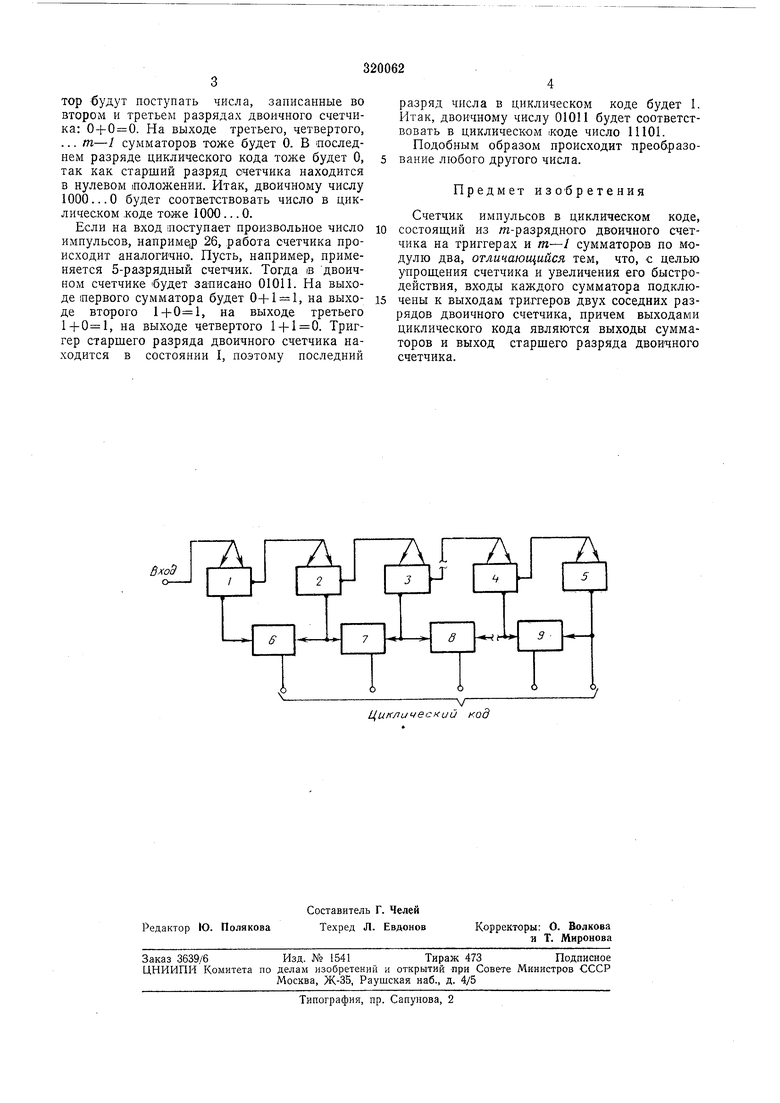

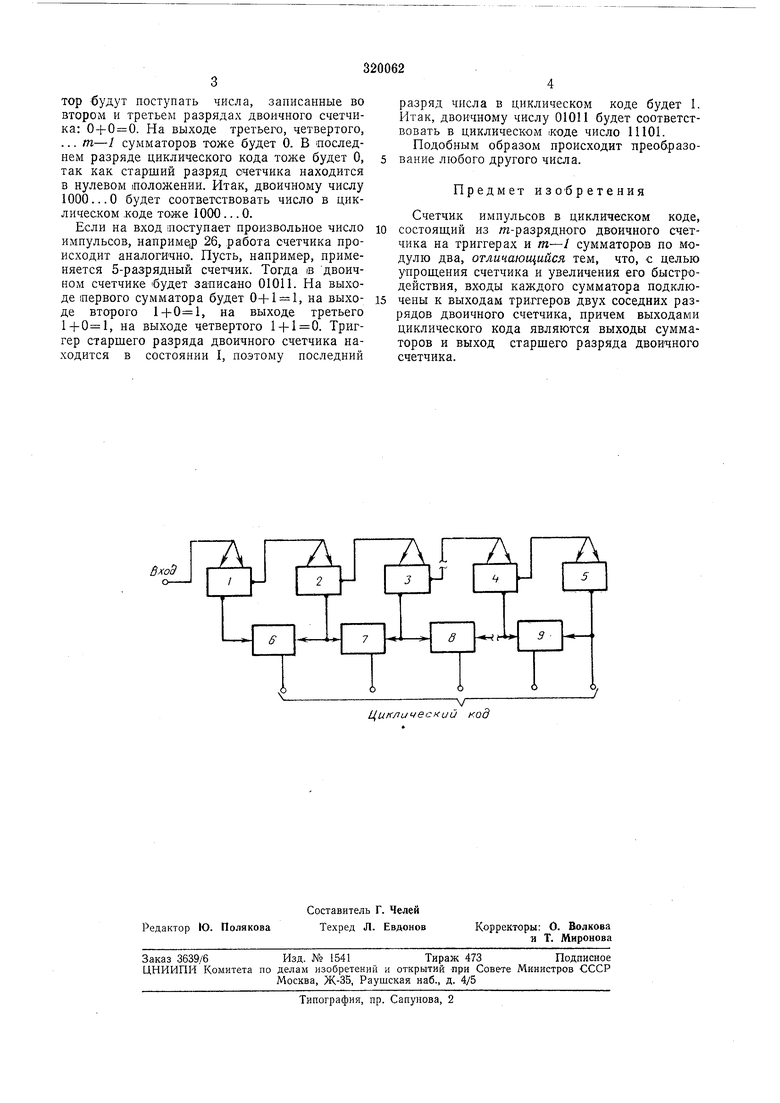

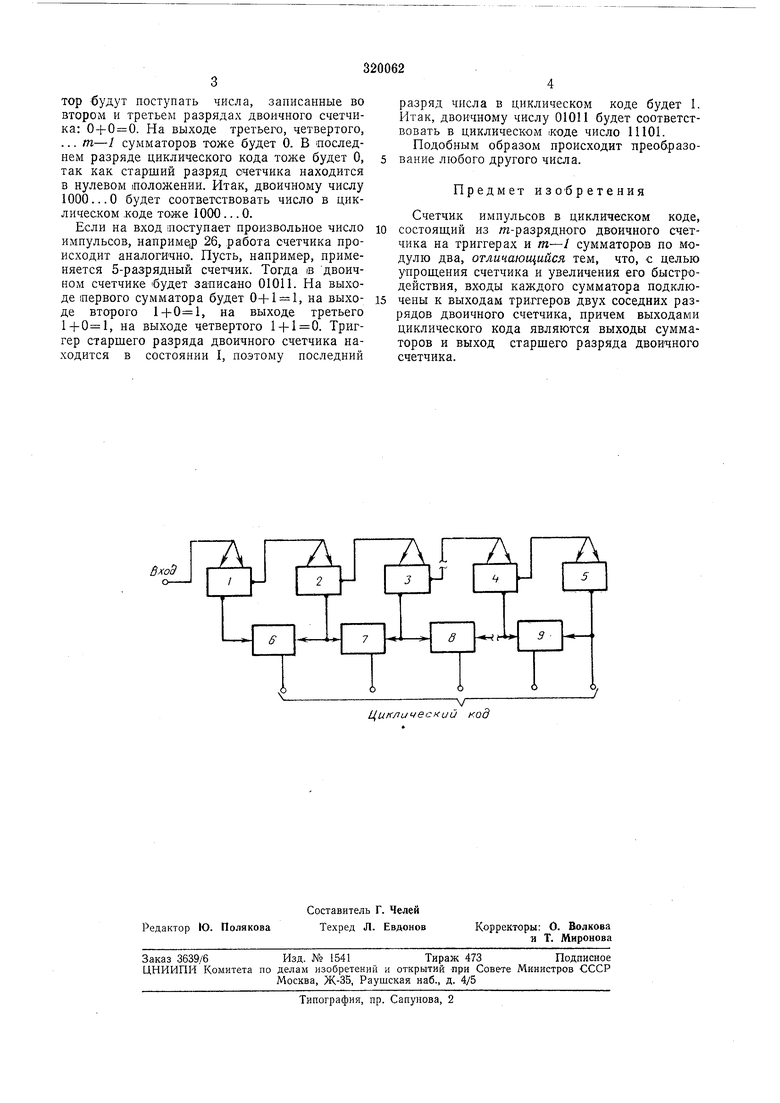

Для получения т-разрядного счетчика импульсов в циклическом коде по вышеуказанному алгоритму входы каждого из т сумматоров по модулю два подключены к выходам триггеров двух соседних разрядов двоичного счетчика, а выходами циклического .кода являются выходы сумматоров и выход старшего разряда двоичного счетчика.

триггерах /, 2, 3...4, 5 и т-1 сумматоров по модулю два 6, 7, 8.. .9. Входы каждого сумматора подключены « выходам триггеров двух соседних разрядов двоичного счетчика,

а -выходами циклического кода являются выходы сумматоров и выход старшего разряда двоичного счетчика.

Счетчик имцульсов в циклическом коде работает следуюш,им образом. В исходном соетоянии все триггеры 1, 2, 3 ... 4, 5 сброшены, т. е. в них записано число 000 ... 0. Первый разряд циклического кода получается на выходе первого сумматора 6, суммируюшего по модулю два числа, записанные в триггерах

первого и второго разрядов двоичного счетчика. В исходном состоянии на выходе первого сумматора будут 0 + , здесь « + - суммирование по модулю два. Аналогично на выходах второго, третьего .... (т-1)-го сумматоров будет тоже 0. Последний разряд циклического кода снимается с триггера старшего разряда двоичного счетчика, в исходном состоянии он тоже будет 0. Итак, исходному состоянию соответствует число в циклическом

коде 000 ... 0.

Если на вход поступает один импульс, то в двоичном счетчике будет записано число 1000...0. Иа первый сумматор будут поступать числа 1+0 1, поэтому лервый разряд

тор будут поступать числа, записанные во втором и третьем разрядах двоичного счетчика: 0+0 0. На выходе третьего, четвертого, ... т-/ сумматоров тоже будет 0. В последнем разряде циклического кода тоже будет О, так как старший разряд счетчика находится в нулевом лоложении. Итак, двоичному числу 1000...О будет соответствовать число в циклическом .коде тоже 1000... 0.

Если на вход поступает произвольное число импульсов, например 26, работа счетчика происходит аналогично. Пусть, например, применяется 5-разрядный счетчик. Тогда в двоичном счетчике будет записано 01011. На выходе первого сумматора будет 0+1 1, на выходе второго , на выходе третьего , на выходе четвертого 1 + . Триггер старшего разряда двоичного счетчика находится в состоянии I, поэтому последний

разряд числа в циклическом коде будет I. Итак, двоичному числу 01011 будет соответствовать в циклическом «оде число 11101.

Подобным образом происходит лреобразование любого другого числа.

Предмет изобретения

Счетчик импульсов в циклическом коде, состоящий из т-разрядного двоичного счетчика на триггерах и т-1 сумматоров по модулю два, отличающийся тем, что, с целью упрощения счетчика и увеличения его быстродействия, входы каждого сумматора подключены к выходам триггеров двух соседних разрядов двоичного счетчика, причем выходами циклического кода являются выходы сумматоров и выход старшего разряда двоичного счетчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор ортогональных сигналов | 1982 |

|

SU1073766A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоично-К-ичного кода в двоичный код | 1983 |

|

SU1126946A1 |

| Арифметико-логическое устройство для сложения и вычитания чисел по модулю | 2017 |

|

RU2639645C1 |

| Генератор тестовой псевдослучайной двоичной последовательности | 1987 |

|

SU1640699A1 |

| @ -Разрядный счетчик в коде Грея | 1982 |

|

SU1070695A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

| ГЕНЕРАТОР ДУГ ОКРУЖНОСТЕЙ | 1973 |

|

SU397902A1 |

8тЭ

Циклический код

Даты

1971-01-01—Публикация