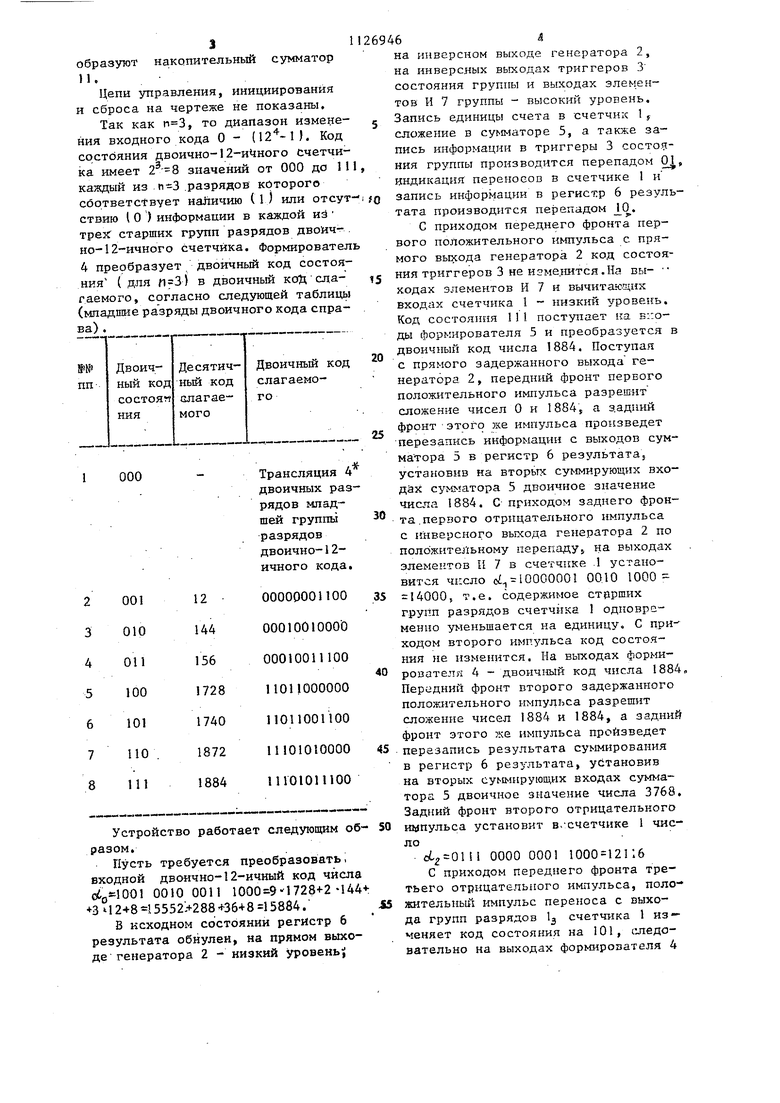

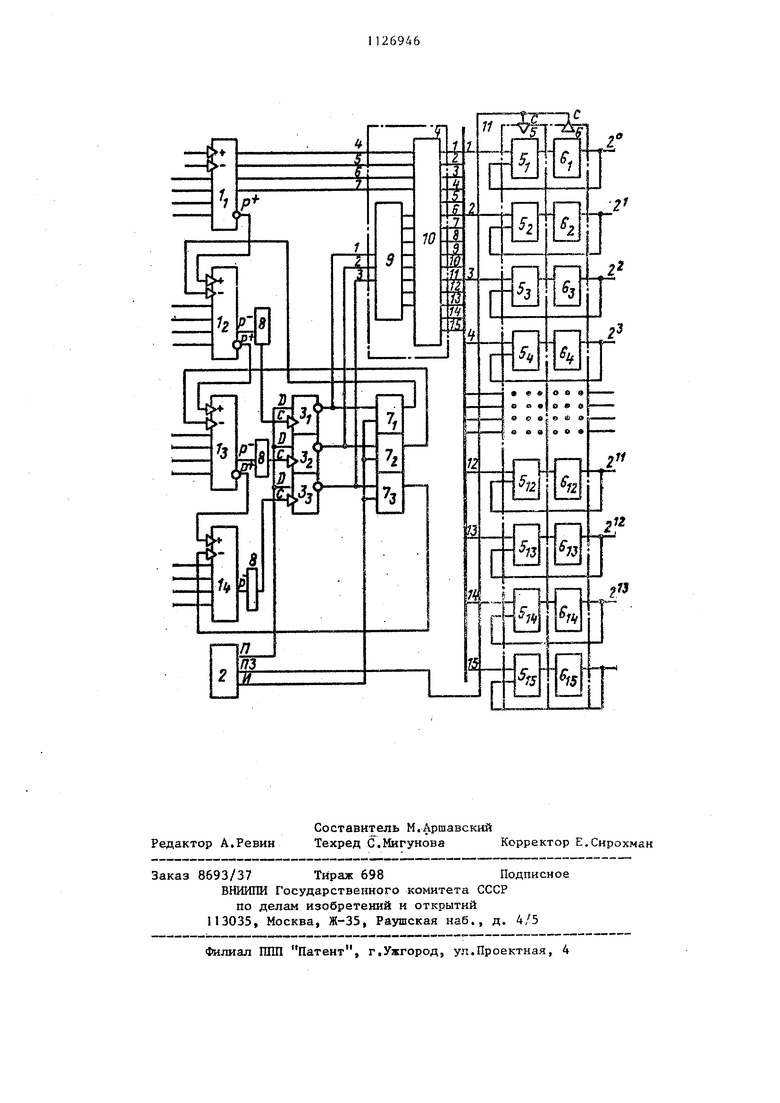

1 Изобретение относится к вычислигтельной технике, а именно к устройствам преобразонания а кодирования информации и может быть использовано в специализированных цифровых системах измерения, обработки н пер дачи информации. Известен, преобразователь двоично ,1 -ичного кода, основанный на параллелБном счете двоично- -ичного счет чика на сложение, содержащий группы двоичных разрядовреверсивного двои но-К-ичного счетчика, схему сравнения и генератор импульсов Г . Недостатками известного устройства являются низкое быстродействие .(время преобразования зависит от ве личины преобразуемого кода и максимально может быть равно двум тактам и отсутствие возможиости введения по правок в коде, Наиболее близким к предлагаемому является преобразователь непозицион ного кода в двоичный код, содержащий группу разрядных счетчиков, генератор импульсов, группу элементов И, группу триггеров состоянияj группу элементов И, форъшрователь эквивалентов и накопительный сумматор, входы которого соединены с выходами формирователя эквивалентов ,входы которого соединены с выходами триггеров состояния группы, а ВЫХОДЫ элементов И группы соединены с счетными входами разрядных счетчико.в группы 1,21, Недостаток данного преобразователя - относительно низкое быстро-, действие, связанное с последователь ным способом преобразования отдельных К-ичных разрядов, . Цель изобретения - повышение .быс тродействия преобразователя в Поставленная цель достигается .тем, .что в преобразователь двоичноХ-ичного кода в двоичный код,, содер жащий группу разрядных счет.чиков, генератор импульсов, группу элементоБ- И, группу триггеров состояния, формироват€;ль зквивал€;нта и накопи тельйый сумматор J выходы .которого являются выходами преобразователя а вхо,цы соединены с соответствующими выходами формирователя эквивален та, -первая группа входов когорого соединена с выходами соответству ощих триггеров состояния группы и с первыми входами соочветствующих элементов И группы выходы которых 62 соединены с счетными входами счетчиков соответствующих разрядов, кроме счетчика йладшего разряда группы, введена группа дешифраторов нуля5 а формирователь эквивалентасодержит дешифратор и шифратор, первая группа входов которого соединена с соответствующими выхо.дами дешифратора, а вторая группа входов шифратора соединена с второй группой входов формирователя эквивалента и соответствующими выходами счётчика младшего разряда группы, разрядные выходы всех разрядных счетчиков, кроме счетчика младшего разряда группы, соединены с входами дешифраторов нуля группы, выходы которых соединены с синхровходамл соответствующих триггеров состояния группы5 В-входы которых соединены с ПРЯМЫМ, генератора импульсов, пр.ямой задержанный которого соединен с :синхровходом накопительного сумматора, а инверсный выход генератора импульсов соединен с вторыми входами элементов И группы, информационные входы разрядlikx счетчиков группы являются входами преобразователя, выходы шифратора являются выxoдa ш формирователя эквивалента, а входы дешифратора являются первой группой входов формирователя эквивалента. На -чертеже приведена блок-схема предлагаемого устройства, гп 3, где п- число К--ИЧНЫХ разря- дон.. Преобразователь двоично-К-ичного кода в двоичный код содернснт :г руппу разрядных счётчиков 1, генератор 2 иютульсов, содержащий прямой П, . прямой задержанный ПЗ и инверсный; И выходы, группу триггеров 3 .(текуще.го). Состояния, формирователь 4 эквивалент.; комбинационный двоичный сумматор 5 и регистр 6 рез.ультата, группу элементов И 7 и группу деннфраторов нуля 8. . .В предлагаемом устройстве формиропатеяь 4 эквивалента выполнен j виде последовательно соединеиш-;х дшиифратора 9 и шифратора 10 и в конкретном спучае реализует функцию: S 2 Citl44-C,,4r728 3 С., С где С J С,-5 С - значения оаэрядов двоичного кода состояния, Комбинйи,иокнь й сумматор 5 и 6 результата в совокупности образуют накопительный сумматор П. Цепи управления, инициирования и сброса на чертеже не показаны. Так как , то диапазон измене ния входного кода О - (12-1). Код состояния двоично-12-ииного счетчи ка имеет значений от 000 до 1 каждый из п-3 .разрядов которого сбответствует наличию ( 1 ) или отсу ствию I О ) информации в каждой иё трехг старших групп разрядов двойчНО-12-ИЧНОГО счетчика. Формировате 4 преобразует. двоичный код состоя ния ( для ) в двоичный слагаемого, согласно следующей таблиць (мпадпше разряды двоичного кода справа) . Трансляция 4 двоичных раз рядов младшей группы разрядов двоично-12ичного кода Устройство работает следующим о разом. Пусть требуется преобразовать, входной двоично-12-ичный код числ 0010 ООП 1000 9 1728+2-14 +3 12 8 15552 288 36+8 15B84. В исходном состоянии регистр 6 результата обнулен, на прямом выхо де генератора 2 - низкий уровень ; 6Д на инверсном выходе генератора 2, на инверсных выходах триггеров 3 состояния группы и выходах элементов И 7 группы - высокий уровень. Запись единицы счета в счетчик 1f сложение в cy мaтope 5, а также запись информации в триггеры 3 cocTO.ftНИН группы производится перепадом 0, индикация переносов в счетчике 1 и запись информации в регистр 6 результата производится перепадом . С приходом переднего фронта первого положительного импульса с. прямого выхода генератора 2 код состояния триггеров 3 не изме.нится.На вы- ходах элементов И 7 и вычитак-щнх входах счетчика 1 низкий уровень. Код состояния 11 1 поступает ка Е::Оды формирователя 5 и преобразуется в двоичный код числа 1884. Поступая с прямого задержанного выхода генератора 2, передний фронт первого положительного импульса раэрешят сложение чисел О и 1884, а з.адиий фронтэтрГо же импульса произведет перезапись информации с выходов сумматора 5 в регистр 6 результата, установив на вторьтх суммирующих входах сум атора 5 двоичное значение числа 1884. С приходом заднего фронта.первого отрицательного импульса с инверсного выхода генератора 2 по положительному П8репаду5 на выходах элементов U 7 в счетчике .1 установится число ci lOOOOOOl 00.10 1000 14000, т.е. содержимое ст(1рших групп разрядов счетчика 1 одновременно уменьшается на единицу. С прн ходом второго импульса код состояния не изменится. Иа выходах формирователк 4 - двоичный код числа 1884, Передний фронт второго задержанного положительного импульса разрешит сложение чисел 1884 и 1884, а задний фронт этого же импульса произведет перезапись результата суммирования в регистр 6 результата, установив на вторых cy ниpyюш tx входах сумматора 5 двоичное значение числа 3768. Задний фронт второго отрицательного импульса установит в.-счетчике 1 число 0000 0001 1000 121:6 С приходом переднего фронта третьего отрицательного импульса, положнтельньй 1-гмпульс переноса с выхода групп разрядов 1 счетчика 1 изменяет код состояния на 101, (шедовательно на выходах формирователя 4

- s

двоичный код числа 1740, Передний фронт третьего задержанного положительного импульса разрешит сложение чисел 3768 и 1740, а задний фронт этого же,импульса установит н вторых суммирующих входах сумматора 5 двоичное значение числа 5508, Задний фронт третьего отрицательног импульса проходит на- вычитающие входы групп:разрядов Ij и 14 счетчика I в соответствии с кодом состояния и устанавливает в счетчике 1 число.

0000 0000 1000 10376

С приходом последующих шести импульсов в соответствии с кодом состояния 100 в сумматхэре 5 производится последовательное суммирование слагаемых 1728 в двоичном коде, а в старшей группе 1 счетчика 1 последовательное вычитание шести импульсов.

Та.ким образом OQOQ.OOOO

В регистре 6 результата после 9 импульсов (циклов преобразования установится двоичный код числа 15876. С приходом переднего фронта десятогоотрицательного импульса устанавливается код состояния 000. В этом случае формирователь 4 эквивалента транслирует разрядный двоичный код младшей группы разрядовЦ счетчика 1 на соответствующие четыре первых суммирующих входа сумматора 5. Передний фронт десятого задержанного положительного импульса разрешит сложение чисел 15876 и 8, а задний фронт 3 этого же импульса устанавливает двоичный код числа 15884 выходах устройства. На это процесс преобразования заканчивается

Перед каждым следующим преобразованием необходимо обнулять регистр 6 результата и счетчик j.

466,

Наличие двоично-12-ичного реверсивного счетчика обеспечивает возможность работы в счетном режиме и введения поправок, в унитарном коде

В предлагаемом устройстве возможно прямое введение поправки в двоичном коде. Для этого достаточно подключить злементы HJBi, количество которык соответствует разрядности кода поправки первыми входами к выходам формирователя4 эквивалента, а выходами - к первым информационным входам сумматора 5, Вторые входы

элементов ИЛИ являются входами соответствующих разрядов двоичного кода поправки. В соответствии со знаком кода поправки устаиавл.шают знаковый режим сумматора 5 и в регистре 6 результата по заднему фронту кмпу:льса

ввода поправки зафиксируется cyMi-ia .или разность преобразованного числа и поправки.

Быстродействие предлагаемого устройства не зависит от разрядности преобразуемого кода и определяется не .)лее К тактами преобразования ( 3 пашем случае 12, тогда как время преобразования прототипа завцсит от величины преобразуемого кода). Так, для oio 15884 i001 ООП 1000 время преобразования в предлагаемом устройстве составляет 10 так.тов, а в прототипе 22 такта.

Предлагаемое устройство по быстродействию превосходит известные устройства последовательного преобразов.ания ( в том числе и машинные ) и уступает лишь устройствам прямого преобразования, являясь проще последних по аппаратурной и алгоритмической реализации,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-К-ичного кода в двоичный код | 1990 |

|

SU1783618A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU888102A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1986 |

|

SU1368993A1 |

| Преобразователь двоичного кода в двоично-десятичный и обратно | 1982 |

|

SU1086424A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1980 |

|

SU941991A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Преобразователь двоичного кода в двоично-десятичный код угловых единиц | 1985 |

|

SU1396280A2 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-kИЧНОГО КОДА В ДВОИЧНЫЙ КОД, содержащий группу разрядных счетчиков, генератор импульсов, группу элементов И, группу триггеров состояния, формирователь эквивалента и накопи телышй сумматор, вьЬсоды которого являются выходами преобразователя, а входы соединены с соответствующими выходами формирователя эквивалента, первая группа входов которого соединена с выходами соответствующих триггеров состояния группы и с первыми входами соответствующих элементов И группы, выходы которых соединены с счетными входами -счетчиков соответствующих разрядов, кроме счетчика младшего разряда группы, о тличающ и и с я тем, что с целью повышения быстродействия, в него введена груйпа дешифраторов нуля, а формирователь эквивалента содержит дешифратор и шифратор, первая группа входов которого соединена с соответствующими выходами дешифратора, а вторая группа входов шифратора соединена с второй группой входов формирователя эквивалента и с соответствующими выходами счетчика младшего разряда группы, разрядные выходы всех разрядных счетчиков, кроме счетчика младшего разряда группы, соединены с входами дешифраторов нуля группы, выходы которых соединены с синхровходами соответствующих триперов состояния групW пы, Б-входы которых соединены с пряС мым выходом генератора импульсов, прямой задержанный выход которого с е соединен с синхровходом накопительного сумматора, а инверсный выход генератора и myльcoв соединен с вторыми входами элементов И группы, О) О) формационные входы разрядных счетчиков группы являются входами преобразователя, выходы шифраторам являются выходами формирователя эквивалента, а входы дешифратора являются первой группой входов формиров.ателя эквивалента .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Автоматические измерения и приборы | |||

| Киев, Высшая школа, 1980, с.273, рис.19 | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-11-30—Публикация

1983-07-21—Подача