(54) ПОЛУПРОВОДНИКОВАЯ ЯЧЕЙКА ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Элемент памяти | 1979 |

|

SU788175A1 |

| Ячейка памяти на мдп-транзисторах | 1975 |

|

SU533988A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU805412A1 |

| Ассоциативная ячейка памяти | 1976 |

|

SU605268A1 |

| Устройство для считывания информации из блоков памяти | 1977 |

|

SU746718A1 |

| Устройство для считывания информации из ассоциативного запоминающего блока | 1974 |

|

SU497636A1 |

| Ячейка памяти с внутренней регенерацией | 1984 |

|

SU1274001A1 |

| Ассоциативный запоминающий элемент на мдп-транзисторах | 1975 |

|

SU542243A1 |

Изобретение относится к вычислительной технике и может найти применение в ассоциативных запоминающих устройствах .

Известны полупроводниковые ячейки памяти, на которых построены ассоциативные запоминаювше устройства, не требующие специально выделять режим регенерации информации, так как хранение информации основано на постоянном протекании тока через/открытое плечо триггера. В тех случаях, когда с целью уменьшения рассеиваемой мощности используется импульсное питание нагрузочных транзисторов, регенерация информации производится независимо от режима работы ячейки (паразитная емкость закрытого плеча восстанавливает заряд при подаче открывающего импульса на затворы нагрузочных транзисторов) 1.

Такие ячейки содержат, большое количество транзисторов и занимают большую площадь, так как для устойчивой работы требуется, чтобы выдерживались определенные соотношения в крутизне, а следовательно, и размерах активных, адресных и нагрузочных транзисторов.

Наиболее близкой к предлагаемой является полупроводниковая ячейка памяти, содержащая информационный транзистор, исток которого соединен со стоком транзистора считывания сток - с одной из обкладок запоминающего конденсатора, затвор - с другой обкладкой запоминающего конденсатора и с истоком транзистора записи, затвор которого связан с первой шиной тактового питания, а сток - с истоком адресного транзистора, сток которого подключен к разрядной шине, а затвор - к а.цресной шине, причем исток адресного транзистора соединен с истоком транзистора считывания, затвор которого подключен ко второй шине тактового питания, и шину нулевого потенциала 2.

Недостаток известной ячейки состоит в том, что она может выполнять только функцию хранения информации и не способна реаэовать функг.ию ассоциативного поиска.

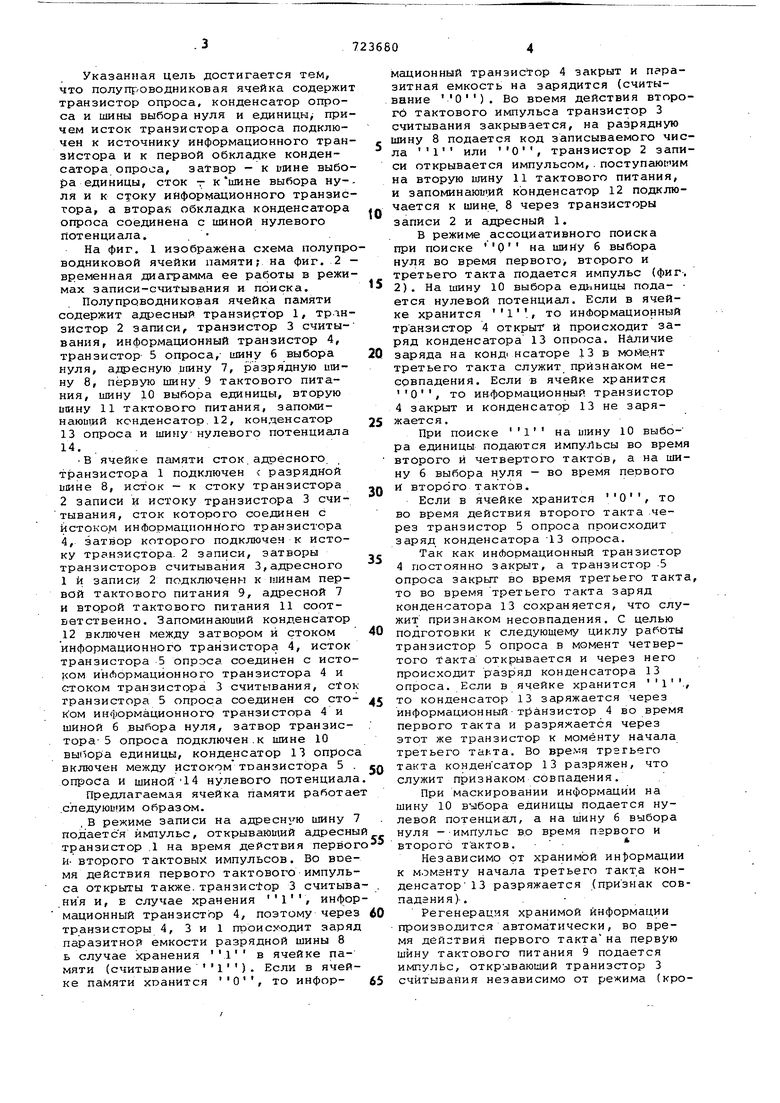

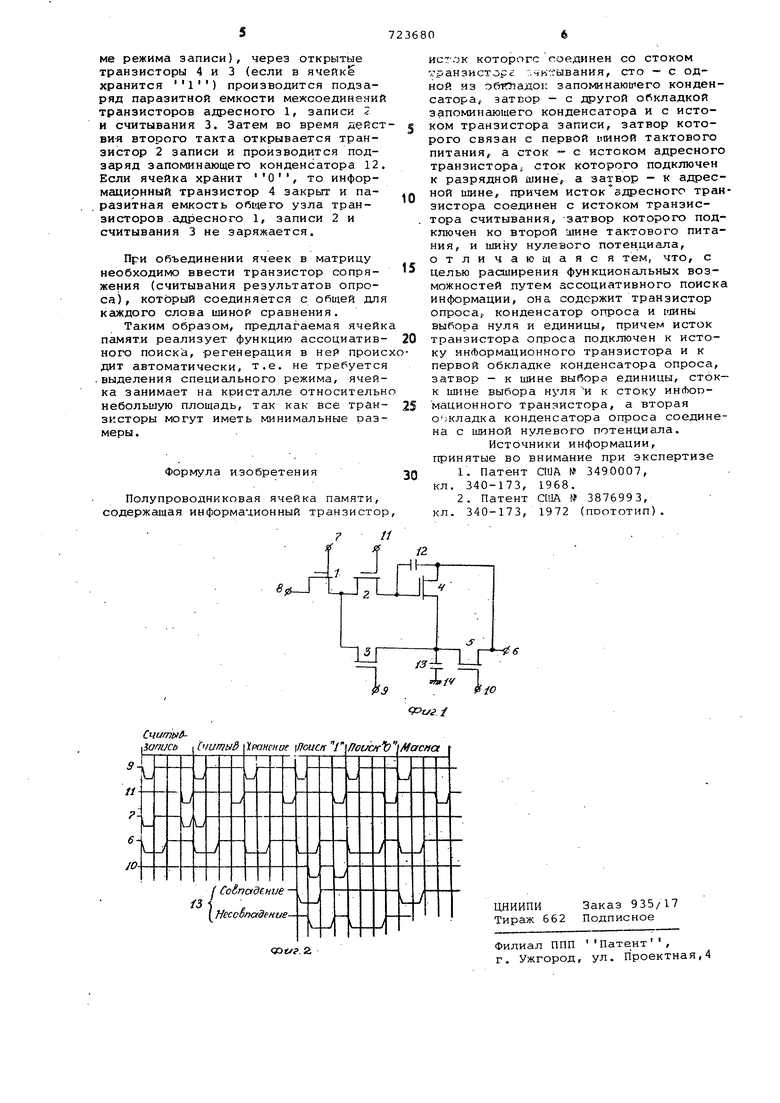

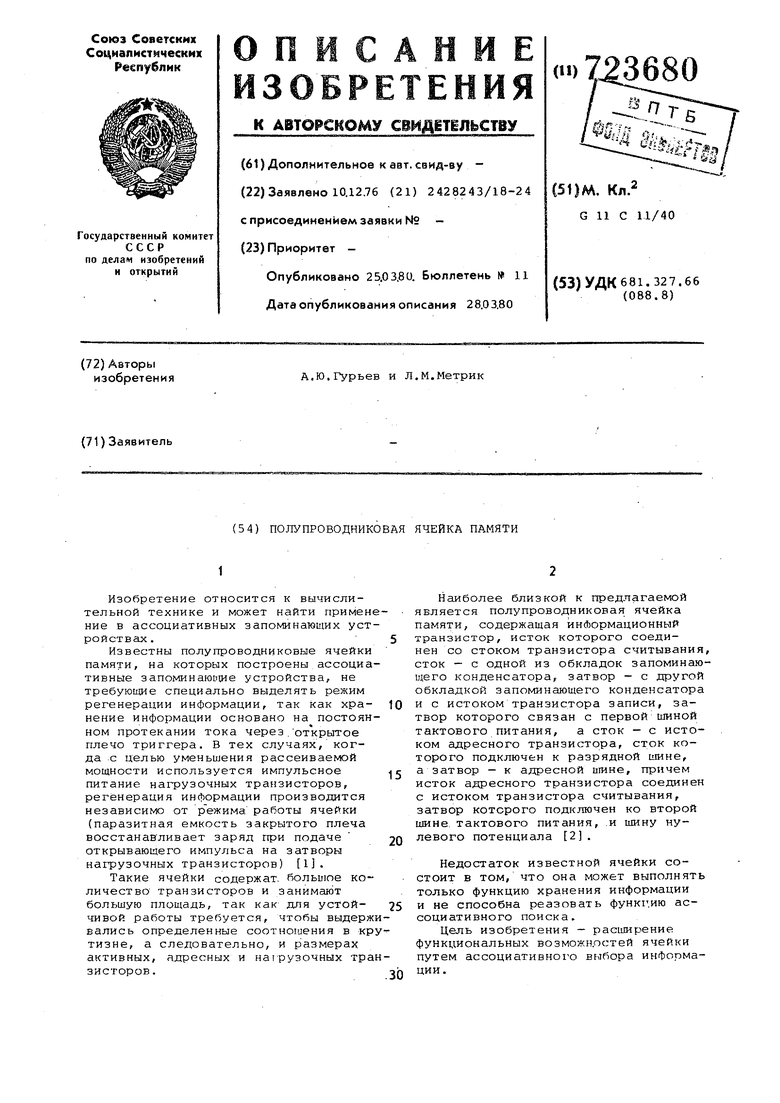

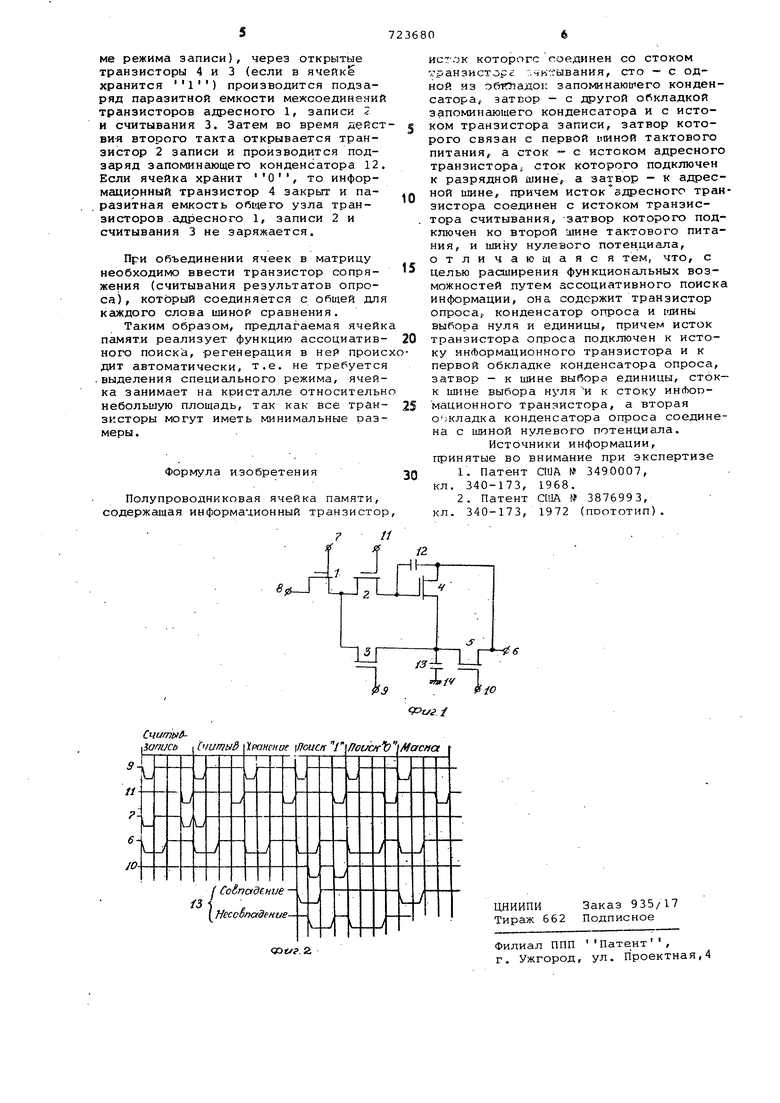

Цель изобретения - рас11Шрение функциональных возможн.остей ячейки путем ассоциативного выбора информации. Указанная цель достигается тем, что полупроводниковая ячейка содержи транзистор опроса, конденсатор опроса и шины выбора нуля и единицы при чем исток транзистора опроса подключен к источнику информационного трак зистора и к первой обкладке конденсатора опроса, затвор - к имне выбо ра единицы, сток т кшине выбора нуля и к стоку информационного транзис тора, а вторая обкладка конденсатора опроса соединена с шиной нулевого Потенциала. На фиг. 1 изображена схема полупр водниковой ячейки памяти; на фиг. 2 временная диаграмма ее работы в режи мах записи-считывания и поиска. Полупроводниковая ячейка памяти содержит адресный транзиртор 1, транзистор 2 записи, транзистор 3 считывания, информационный транзистор 4, транзистор 5 опроса,- шину 6 выбора нуля, адресную пину 7, р1азрядную ишну 8, первую шину 9 тактового питания, шину 10 выбора единицы, вторую цину 11 тактового питания, запоминаюш,ий кснденсатор. 12, конденсатор 13 опроса и шину нулевого потенциала 14. . . В ячейке памяти сток.адресного транзистора 1 подключен разрядной шине 8, исток - к стоку транзистора 2 записи и истоку транзистора 3 считывания, сток которого соединен с истоком информационного транзистора 4, затвор которого подключен к истоку транзистора. 2 записи, затворы транзисторов считывания 3,адресного 1 и записи 2 подключены к тинам первой тактового питания 9, адресной 7 и второй тактового питания 11 соответственно. Запоминающий конденсатор 12 включен между затвором и стоком информационного транзистора 4, исток транзистора 5 опрэса соединен с истоком инЛормационного транзистора 4 и стоком транзистора 3 считывания, транзистора 5 опроса соединен со стоком информационного транзистора 4 и шиной 6 выбора нуля, затвор транзистора- 5 опроса подключен.к шине 10 выСюра единицы, конденсатор 13 опрос включен между истоком транзистора 5 опроса и шиной14 нулевого потенциала Предлагаемая ячейка памяти работае .следующим образом. , В режиме записи на адресную шину 7 подается импульс, открывающий адресны транзистор .1 на время действия первог и- второго тактовых импульсов. Во воемя действия первого тактового импульса открыты также, транзис ор 3 считыва ния и, Е случае хранения , инфор мационный транзистор 4, поэтому через транзисторы 4, 3 и 1 происходит заряд паразитной емкости разрядной шины 8 ь случае хранения М в ячейке памяти (считывание 1). Если в ячейке памяти хранится О, то информационный транзистор 4 закрыт и паразитная емкость на зарядится (считывание О). Во воемя действия второго тактового импульса транзистор 3 считывания закрывается, на разрядную шину 8 подается код записываемого числа или О, транзистор 2 записи открывается импульсом, . поступаюиим на вторую шину 11 тактового питания, и запоминающий конденсатор 12 подключается к шине. 8 через транзисторы записи 2 и адресный 1. В режиме ассоциативного поиска на шийу 6 выбора при поиске нуля во время первого, второго и третьего такта подается импульс (фиг-, 2). На шину 10 выбора ед1-1ницы пода- ется нулевой потенциал. Если в ячейке хранится , то информационный транзистор 4 открыт и происходит заряд конденсатора 13 опроса. Наличие заряда на кондс нсаторе 13 в моме.нт третьего такта служит признаком несовпадений. Если в ячейке хранится О, то информационный транзистор 4 закрыт и конденсатор 13 не заряжается. При поиске на шину 10 выбо-ра единицы подаются ймпуЛьсы во время второго и четвертого тактЬв, а на шину 6 выбора нуля - во время первого и второго тактов. Если в ячейке хранится О, то во время действия второго такта .через транзистор 5 опроса происходит заряд конденсатора -13 опроса. Так как информационный транзистор 4 постоянно закрыт, а транзистор .5 опроса закрыт во время третьего такта, то во время третьего такта заряд конденсатора 13 сохраняется, что служит признаком несовпадения. С целью подготовки к Следующему циклу работы транзистор 5 опроса в момент четвертого Такта открывается и через него происходит конденсатора 13 опроса. Если в ячейке хранится ., то конденсатор 13 заряжается через информационный - транзистор 4 во время первого такта и разряжается через этот же транзистор к моменту начала третьего таьта. Во время трзгьего такта конденсатор 13 разряжен, что служит признаком совпадения. При маскировании информации на шину 10 выбора единицы подается нулевой потенциал, а на шину б выбора нуля --импульс в.о время первого и второго тактов. - Независимо от хранимой информации к моменту начала третьего такт.а конденсатор 13 разряжается (признак совпадения)-. Регенерация хранимой информации производится автоматически, во время действия первого тактана первую шину тактового питания 9 подается импульс, открывающий транизстор 3 считывания независимо от режима (кроме режима записи), через открытые транзисторы 4 и 3 (если в ячейке хранится Ч) производится подзаряд паразитной емкости межсоединений транзисторов адресного 1, записи 2 и считывания 3. Затем во время дейст вия второго такта открывается транзистор 2 записи и производится подзаряд запоминающего конденсатора 12. Если ячейка хранит О, то информационный транзистор 4 закрыт и паразитная емкость общего узла транзисторов .адресного 1, записи 2 и считывания 3 не заряжается. При объединении ячеек в матрицу необходимо ввести транзистор сопряжения (считывания результатов опроса), который соединяется с общей для каждого слова шиной сравнения. Таким образом, предлагаемая ячейк памяти реализует функцию ассоциативного поиска, -регенерация в неР проис дит автоматически, т.е. не требуется .выделения специального режима, ячейка занимает на кристалле относительн небольшую площадь, так как все транзисторы могут иметь минимальные размеры , Формула изобретения Полупроводниковая ячейка памяти, содержащая информационный транзистор которого соединен со стоком транзисторе ;;чк-:ывания, сто - с одной из о&ргнадог. запоминающего конденсатора, затвор - с другой обкладкой запоминающего конденсатора и с истоком транзистора записи, затвор которого связан с первой шиной тактового питания, а сток - с истоком адресного транзистора сток которого подключен к разрядной шине, а затвор - к адресной шине, причем исток адресного транзистора соединен с истоком транзистора считывания, затвор которого подключен ко второй шине тактового питания, и шину нулевого потенциала, отличающаяся тем, что, с целью расширения функциональных возможностей путем ассоциативного поиска информации, она содержит транзистор опроса конденсатор опроса и 1хины выбора ну.пя и единицы, причем исток транзистора опроса подключен к истоку информационного транзистора и к первой обкладке конденсатора опроса, затвор - к ишне выбора единицы, сток- к шине выбора нуля и к стоку инЛормационного транзистора, а вторая ожладка конденсатора опроса соединена с шиной нулевого потенциала. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3490007, кл. 340-173, 1968. 2.Патент CQIA № 3876993, кл. 340-173, 1972 (поототип).

Т1Г

If

io

Авторы

Даты

1980-03-25—Публикация

1976-12-10—Подача