(54) НАКОПИТЕЛЬ ДЛЯ ЗАПОМИНАЮЩЕГО УСТРОЙСТВА

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель | 1980 |

|

SU942151A1 |

| Усилитель считывания с регенерациейНА Мдп-ТРАНзиСТОРАХ | 1979 |

|

SU830575A1 |

| Усилитель считывания на мдп-транзисторах | 1978 |

|

SU721852A1 |

| Матричный накопитель для полупроводникового запоминающего устройства | 1978 |

|

SU729636A1 |

| Динамическая ячейка памяти | 1974 |

|

SU523454A1 |

| Накопитель для полупостоянного запоминающего устройства с электрической перезаписью информации | 1973 |

|

SU519760A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1531169A1 |

| Программируемый элемент памяти | 1977 |

|

SU649035A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

1

Изобретение относится к вычислительной технике и может использоваться, в частности, при построении оперативных запоминающих устройств большой информационной емкости.

Известен накопитель для запоминающего устройства, содержащий запоминающую матрицу, элементы памяти которой состоят из МДП-транзисторов и конденсаторов, при этом затворы МДП-транзисторов соединены с соответствующими адресными щинами, ю истоки с разрядными шинами, а стоки подключены к первым выводам конденсаторов. Вторые выводы конденсаторов соединены с шиной нулевого потенциала 1.

Недостатком накопителя является низ- 15 кая надежность, что обусловлено необходимостью использования высокочувствительных усилителей для считывания информации.

Наиболее близким к предлагаемому 20 является накопитель для запоминающего устройства, содержащий запоминающую матрицу, элементы памяти которой состоят из МДП-транзисторов и конденсатор1ов, при этом затворы МДП-транзисторов соединены с соответствующими адресными шинами, истоки МДП-транзисторов объединены и подключены к соответствующим разрядным щинам, стоки МДП-транзисторов соединены с первыми выводами конденсаторов, вторые выводы которых соединены с соседними адресными шинами 2.

Накопитель для запоминающего устройства характеризуется высоким быстродействием и высокой плотностью хранения информации. Однако из-за необходимости применения сверхчувствительных усилителей для считывания информации, недостатком накопителя является низкая надежность считывания.

Цель изобретения - повышение надежности накопителя для запоминающего устройства.

Поставленная цель достигается тем, что в накопитель введены предварительные усилители, а МДП-транзисторы и конденсаторы разбиты на группы, причем каждый предварительный усилитель состоит из первого и второго МДП-транзисторов, стоки которых подключены к разрядной шине, исток первого и затвор второго каждого из МДП-транзисторов соединены с истоками МДП-транзисторов каждой группы элементов памяти, стоки которых подключены к одним из выводов конденсаторов, другие выводы которых подключены к одним из адресных шин, затворы МДП-транзисторов каждой группы элементов памяти подключены к другим адресным шинам, затвор первого и исток второго МДП-транзисторов подключен к дополнительной адресной шине.

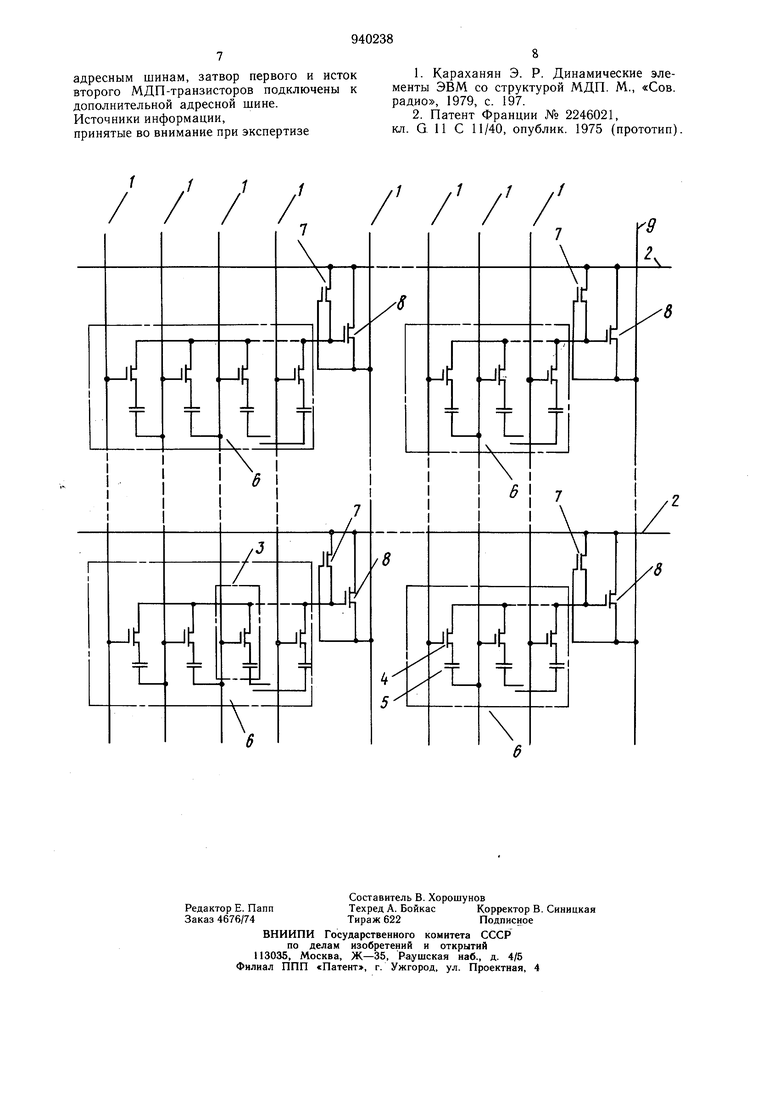

На чертеже показан накопитель для запоминаюшего устройства.

Накопитель содержит запоминаюш,ую матрицу на основе адресных шин 1, разрядных шин 2, элементов 3 памяти, каждый из которых состоит из МДП-транзисторов 4 и конденсаторов 5 и предварительных усилителей. МДП-транзисторы 4 и конденсаторы 5 разбиты на группы 6, а каждый предварительный усилитель состоит из первого 7 и второго 8 МДП-транзисторов, стоки которых подключены к разрядной шине 2. Истоки первого 7 и затвор второго 8 каждого из МДП-транзисторов соединены с истоками МДП-транзисторов 4 каждой группы 6 элементов 3 памяти, стоки которых подключены к одним из выводов конденсаторов 5, другие выводы которых подключены к одним из адресных шин 1. Затворы МДПтранзисторов 4 каждой группы 6 элементов памяти 3 подключены к другим адресным шинам 1. Затвор первого 7 и исток второго 8 МДП-транзисторов подключены к дополнительной адресной шине 9.

Накопитель для запоминаюшего устройства работает следующим образом.

В режиме записи информации на нужную дополнительную адресную шину 9 подается высокий уровень напряжения и открываются соответствующие первые МДП-транзисторы 7 предварительных усилителей. Информация, подлежащая записи, подается на разрядные шины 2 и через открытые первые транзисторы 7 поступает на объединенные истоки МДП-транзисторов 4 групп 6 элементов 3 памяти. После подачи высокого уровня напряжения на нужную адресную шину 1 открываются соответствующие МДП-транзисторы 4, и первые обкладки подключенных к ним конденсаторов 5 через открытые МДП-транзисторы 4 и первые МДП-транзисторы 7 подключаются к разрядным шинам 2.

Вторые обкладки конденсаторов 5 выбранных элементов 3 памяти подключены к одним из адресных шин (соседней строки) 1, находящимся под низким потенциалом (высокий уровень напряжения выборки подается только на одну адресную шину 1) Если на разрядную шину 2 подается уровень напряжения, соответствующий логической «1, происходит заряд до высокого уровня

напряжения конденсатора 5, выбранного элемента 3 памяти. Если на разрядную шину 2 подается уровень напряжения, соответствующий логическому «О, то выбранный конденсатор 5 разряжается до низкого уровня напряжения (или остается разряженным, если на нем хранилась информация, соответствующая логическому «О).

По окончании процесса записи на адресную шину 1 подается низкий уровень

напря)сения, и МДП-транзисторы 4 закрываются.

На разрядные шины 2 подается низкий уровень напряжения, через открытые первые транзисторы 7 осуществляется разряд объединенных истоков МДП-транзисторов 4 групп 6 до низкого уровня напряжения. После этого на дополнительную адресную шину 9 подается низкий уровень напряжения, и первые транзисторы 7 предварительных усилителей закр ываются.

На этом процесс записи завершается.

Необходимо заметить, нто подача высокого уровня напряжения на адресную шину 1 не может изменить состояние подключенного к ней запоминающего конденсатора 5 соседнего элемента 3 памяти, так как МДП-транзистор 4 указанного соседнего элемента закрыт.

В режиме хранения информации на дополнительные адресные шины 9 и адресные шины 1 подаются низкие уровни напряжений. Поэтому все МДП-транзистрры 7 и 4 закрыты.

Информация хранится в форме заряда на конденсаторах 5. При этом логической «1 соответствует заряженное состояние конденсатора 5, а логическому «О - разряженное состояние.

Объединенные области истоков МДПтранзисторов 4 групп 6 элементов 3 памяти и подключенные к ним затворы вторых МДП-транзисторов 8 предварительных усилителей разряжены до низкого уровня напряжения.

Изменение напряжения на разрядных шинах 2 не может изменить этого состояния, так как первые МДП-транзисторы 7 закрыты.

При считывании информации разрядные шины 2 заряжаются до высокого уровня напряжения. На одну из адресных шин 1 подается высокий уровень напряжения, и соответствующие МДП-транзисторы 4 открываются, подключая выбранные конденсаторы 5 к затворам вторых МДП-транзисторов 8.

Информация распознается по состоянию вторых МДП-транзисторов 8, т. е. открыты они или закрыты (на дополнительных адресных шинах 9 низкие уровни напряжений). Если второй МДП-транзистор 8, открыт что соответствует заряженному выбранному конденсатору 5, то происходит разряд

предварительно заряженной разрядной шины 2 - в данном случае считывается логическая «1.

Если МДП-транзистор 4 закрыт, что соответствует разряженному выбранному конденсатору 5, то соответствующая разряд ная шина 2 остается заряженной - в данном случае считывается логический «О.

Изменение напряжения на разрядных шинах 2 регистрируется усилителями считывания (входящими в состав ЗУ).

По окончании процесса считывания ни адресную шину 1 подается низкий уровень напряжения .

Так как в процессе хранения информации, (а также при считывании) заряженные конденсаторы 5 разряжаются, накопитель для запоминающего устройства требует периодического восстановления (регенерации) хранимой в нем информации.

Процесс регенерации осуществляется следующим образом: сначала определяется состояние конденсаторов 5, за.тем осуществляется запись считанной информации.

Информация восстановляется во всех запоминающих элементах.

В связи с тем, что при считывании информации происходит условный ( в зависимости от состояния конденсаторов 5) разряд разрядных шин 2 до низкого уровня . напряжения, обеспечивая тем самым возможность применения малочувствительных усилителей считывания и высокую надежность считывания, не хуже, чем у накопи-, телей, построенных на трехтранзисторных, запоминающих элементах.

Однако если в накопителе, построенном на базе трех транзисторных запоминающих элементов, для обслуживания запоминающего конденсатора требуется три МДПтранзистора, в предлагаемом устройстве для этой цели используется меньшее число.

Число элементов 3 памяти в одной группе 6 определяется из следующих соображений.

При открывании МДП-транзистора 4 конденсатор 5 подключается параллельно паразитной емкости, образованной истоками МДП-транзисторов 4 группы 6 элементов и затвором, и истоком соответствующих второго 8 и первого 7 МДП-транзис-торов предварительного усилителя.

При этом приращение напряжения на объединенных истоках МДП-транзисторов 4 группы 6 элементов должно быть больше порогового напряжения второго МДП-транзистора 8 для обеспечения разряда разрядной шины 2 при считывании информации.

Прирашение напряжения на объединенных истоках адресных транзисторов 4 группы 6 элементов (пренебрегая емкостью затвора второго МДП-транзистора 8 и истока первого МДП-транзистора 7) определяется выражением

ли ,

где ли - прирашение напряжения; напряжение на обкладках конденсатора 5;

Ue напряжение на объединенных истоках МДП-транзисторов группы б элементов; Cj - емкость конденсатора 5; Cg емкость объединенных истоков

МДП-транзисторов группы 6 элементов.

Так как приращение напряжения AU

должно быть больше порогового напряжения

МДП-транзисторов Unop-, и учитывая, что

Сб П-С4,

где п - число МДП-транзисторов 4 в

группе В элементов; С - емкость истока одного МДПтранзистора 4, то число п определяется величиной

„.Ci/5- /6-t/noiJ-Cs

Cjj

Так как значения Ue перед считыванием близко к нулю, то

п- CUs-UnopKi; пор С

и находится обычно в пределах от 4 до 10 (меньщее количество нецелесообразно, а подключение большего числа МДПтранзисторов приводит к необходимости, увеличения размеров конденсаторов 5).

Таким образом, накопитель для запоминающего устройства имеет высокую надежность при большой информационной плотности в интегральном исполнении.

Формула изобретения

Накопитель для запоминающего устройства, содержащий запоминающую матрицу, элементы которой состоят из МДПтранзисторов и конденсаторов, отличающийся тем, что, с целью повыщения надежности накопителя, в него введены предварительные усилители, а МДП-транзисторы и конденсаторы разбиты на группы, причем каждый предварительный усилитель состоит из первого и второго МДП0 транзисторов, стоки которых подключены к разрядной шине, исток первого и затвор второго каждого из МДП-транзисторов соединены с истоками МДП-транзисторов каждой группы элементов памяти, стоки которых подключены к одним из выводов

5 конденсаторов, другие выводы которых подключены к одним из адресных шин, затворы МДП-транзисторов каждой группы элементов памяти подключены к другим

адресным шинам, затвор первого и исток второго МДП-транзисторов подключены к дополнительной адресной шине. Источники информации, принятые во внимание при экспертизе

кл. G 11 С 11/40, опублик. 1975 (прототип).

/X///

Авторы

Даты

1982-06-30—Публикация

1980-10-08—Подача