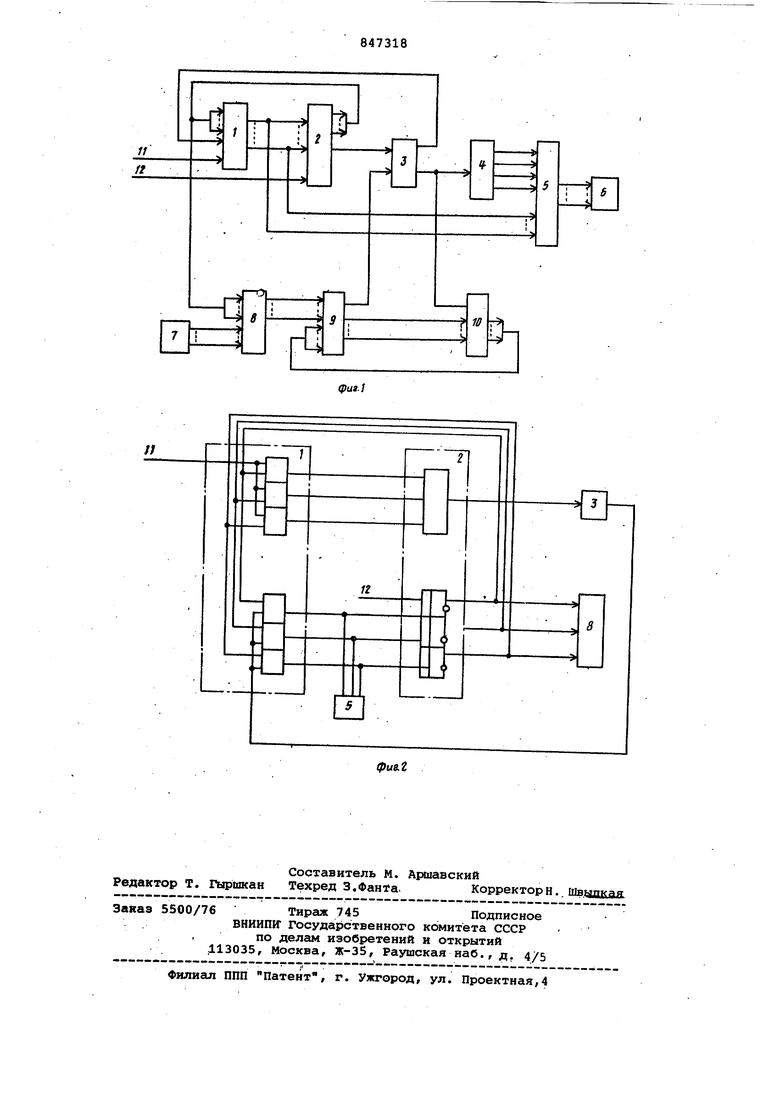

остатков, которое усложняет управление сумматором и понижает быстродействие преобразователя. Цель изобретения - повышение быстродействия и расшлрение функциональных возможностей, заключающихся в преобразовании кода с заданным koэффициeнтoм масштабирования. Поставленная цель достигается тем что в преобразователь двоичного кода .в двоично-десятичный, содержащий бло управления вычитанием., тактирующий вход которого соединен с шиной такто вых импульсов,блок формирования управляющих сигналов,установочный вход которого соединен с шиной начала пре образования,входы номера десятичного разряда блока формирования управляющих сигналов соединены с выходами блока управления вычитанием, а выход соединены со входами номера десятичного разряда блока управления вычитанием, блок анализа знака, вход опроса которого соединен с выходом сигнала продолжения преобразования блока формирования управляющих сигналов, счетчик, группу элементов И и статический регистр, входы которо соединены с выходами группы элементов И, первые входы которых соединены с выходами счетчика, а вторые входы группы элементов И соединены с выходами блока управления вычитан ем, вход счетчика соединен с выходо положительного знака блока анализа знака, выход отрицательного знака которого соединен со входом изменения номера десятичного разряда блок управления вычитанием, введены регистр масштабного коэффициента,бл формирования масштабируемых двоичны эквивалентов, комбинационный суммат и регистр остатка, информационные входы которого соединены с выходами комбинационного сумматора, вход раз решения записи которого соединен с выходом положительного знака блока анализа знака, а выходы регистра остатка соединены с первой группой входов комбинационного сумматора, вторая группа входов которого соеди нена с выходами блока масштабируемы двоичных эквивалентов, а знаковый выход комбинационного сумматора сое динен со знаковым входом блока анализа знака, выходы регистра масштаб ного коэффициента соединены со входами масштабирования блока масштаби руемых двоичных эквивалентов,входы номера десятичного разряда которого соединены с выходами блока формирования управляющих сигналов. На фиг, 1 и 2 представлен предла гаемый преобразователь двоичного кода в двоично-десятичный. 1и)еобразователь содержит блок 1 управления вычитанием, выходы которого соединены со входами блока 2 ф мирования управляющих сигналов, блок 3 анализа знака, выход отрицательного знака которого соединен со входом блока 1 управления вычитанием, а выход положительного знака соединен со счетным входом счетчика, выходы которого через группу элементов И соединены со входами соответствующих тетрад статического регистра б, регистр 7 масштабного коэффициента, выходы которого через блок 8 формирования масштабируемых двоичных эквивалентов соединены со входами первого слагаемого комбинационного сумматора 9, а выходы комбинационного сумматора 9 через регистр 10 остатка, запись которого осуществляется по заднему фронту импульса записи, соединены со входами второго слагаемого комбинационного сумматора 9, знаковый выход которого соединен с первым входол блока 3 анализа знака числа, а второй вход блока3 анализа знака числа соединен с одним из выходов блока 2 формирования управляющих сигналов, другие выходы соединены со входами блока 1 управления вычитанием и другими входами блока 8 масштабируемых двоичных эквивалентов. Временная диаграмма работы преобразователя определяется импульсами, поступающими с шины 11 тактовых импульсов, соединенной с одноименным входом блока 1 управления вычитанием, и с шиной 12 начала преобразования (12), соединенной с одноименным входом блока 2 формирования управляющих сигналов. Блок 8 масштабируемых двоичных эквивалентов формирует константы, величина которых определяется по формуле . const , m где р 0,11,12,... - порядок преобразуемого числа; m - масштабный коэффициент, вводимый через регистр 7 масштабного коэффициента. Блок 8 масштабируемых двоичных эквивалентов содержит N+K разрядов, причем N - разряды фО1Ллируют целую часть константы, а К - разряды - дробную. Количество N - разрядов соответствует разрядности преобразуемого кода, а К - разрядов - точности набора дробной части константы. Преобразователь работает следующим образом. В N - разряды регистра 10 остатка вводится преобразуемое число. С приходом сигнала на шину Начало преобразования на одном из выходов блока 2 формирования управляющих сигналов появляется сигнал, который в зависимости от масштабного коэффициента посредством блока 8 формирования масштабируемых двоичных эквивалентов формирует в дополнительном коде, позволяющим операцию вычитания заменить операцией сложения, константу старшего порядка, которая вводится в комбинационный сумматор 9. Если знак остатка комбинационного сумматора 9 положительный, то тактовый импульс с одноименной шины 11, через блок 1 управления вычитанием, блок 2 формирования управляющи Сигналов, блок 3 анализа знака числа поступает на вход четырехразрядного двоичного счетчика 4 и вход записи регистра 10 остатка. В четырехразрядный двоичный счетчик 4 записывает ся единица, а в регистр 10 остатка содержимое комбинационного сумматора 9, при этом на выходе комбинационного сумматора 9 формируется новый остаток, и если его знак положительный, то процесс повторяется. Если знак остатка комбинационного сумматора 9 отрицательный, то тактовый импульс, с выхода блока 3 анализа з-нака числа через блок 1 управления вычитанием, поступает на вход блока 2 формирования управляющих сиг налов , который вырабатывает для блока 8 формирования масштабируемых двоичных эквивалентов сигнал формирования константы следующего порядка (на единицу меньшего). Одновременно тактовый импульс, с соответствующего выхода блока 1 управления вычитанием через соответствующую группу элементов И 5, записывает в тетраду старшего порядка статического регистра 6 содержимое четырехразрядного двоичного счетчика 4. Процесс, аналогичный описанному, повторяется до тех пор, пока из четырехразрядного двоичного счетчика 4 не будет передан результат,характеризующий млад ший порядок преобразуемого двоичного кода. Использование изобретения позволя ет осуществлять непосредственный цифровой контроль за аналоговыми величинами, оцифровка которых производится устройствами, имеющими определенные величины масштабных коэффициентов. Формула изобретения Преобразователь двоичного кода в двоично-десятичный, содержащий блок управления вычитанием, тактирую щий вход которого соединен с шиной тактовых импульсов, блок формирования управляющих сигналов, установочный вход которого соединен с шиной начала преобразования, входы номера десятичного разряда блока формирования управляющих сигналов соединены с выходами блока управления вычитанием, а выходы соединены со входами номера десятичного разряда блока управления вычитанием, блок анализа знака, вход опроса которого соединен с выходом сигнала продолжения преобразования блока формирования управляющих сигналов, счетчик, группу элементов И и статический регистр, входы которого соединены с выходами группы элементов И, первые входы которых соединены с выходами счетчика, а вторые входы группы элементов И соединены с выходами блока управления вычитанием, вход счетчика соединен с выходом положительного знака блока анализа знака, . выход отрицательного знака которого соединен со входом изменения номера десятичного разряда блока управления вычитанием, отличающийс я тем, что,с целью повышения быстродействия и расширения функциональных возможностей, заключающихся в преобразовании кода с заданным коэффициентом масштабирования, в него введены регистр масштабного коэффициента, блок формирования масштабируемых двоичных эквивален-тов, комбинационный сумматор и регистр остатка, информационные входы которого соединены-с выходами комбинационного сумматора, вход разрешения записи которого соединен с выходом положительного знака блока анализа знака, а выходы регистра остатка соединены с первой группой входов комбинационного сумматора, вторая группа входов которого соединена с выходами блока масштабируемых двоичных эквивалентов, а знаковый выход комбинационного сумматора соединен со знаковым входом блока анализа знака, выходы регистра масштабного коэффициента соединены со входами масштабирования блока масштабируемых двоичных эквивалентов, входы номера десятичного разряда которого соединен с выходами блока формирования управляющих сигналов. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 525945 кл. G Об F 5/02, 1974. 2.Авторское свидетельство СССР 437069, кл. G 06 F 5/02, 1972 (прототип).

-т

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоичного кода в двоично-десятичный | 1978 |

|

SU864278A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1977 |

|

SU690474A1 |

| Цифровой фазометр | 1983 |

|

SU1187100A2 |

| Преобразователь двоичного кода в двоично-десятичный | 1972 |

|

SU437069A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ В ТРОИЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ НА НЕЙРОНАХ | 2010 |

|

RU2453900C2 |

| Интегрирующее устройство | 1990 |

|

SU1727122A1 |

//

Авторы

Даты

1981-07-15—Публикация

1979-02-26—Подача