Предлагаемое изобретение относится к цифровой вычислительной технике и может быть использовано при построении цифровы.х вычислительных машин.

Известны устройства для деления двоичных чисел, содержащие сумматор, регистр делителя, буферный регистр и схемы анализа знака.

В известном устройстве схема комбинационного сумматора для четырех разрядов с одним уровнем логики сложна и технически трудно выполнима. В таком комбинационном сумматоре много логических схем «ИЛИ с большим количеством входов, следствием чего является возрастание на элементы.

Цель изобретения - создание устройства деления двоичных чисел, в котором знак очередного остатка определяется путем анализа трех старших разрядов очередного остатка, включая первый знаковый, приведение переноса производится только в знаковом разряXX

де и анализируется код вида х, хх, где X - «О или «1, с учетом действия, в результате которого получен анализируемый остаток, причем скорость предложенной схемы равна скорости работы схемы с комбинационным сумматором на 4 разряда.

редного остатка по трем старшим разрядам этого остатка исходили из следующих соображений: если к однорядному виду приводить только знаковые разряды и анализировать

код вида XX, переносы

XXсумма,

то для такого кода: во-первых, после прибавления положительного нормализованного делителя к очередному сдвинутому остатк/

(вычитания отрицательного нормализованного делителя из очередного остатка) второй знак остатка всегда во-вторых, после вычитания положительного нормализованного делителя из очередного сдвинутого остатка

(прибавления отрицательного делителя к очередному остатку) второй знак всегда совпадает с первым.

В справедливости этого нетрудно убедиться, если перебрать комбинации кодов, дающие после приведения в 4-х старших разрядах коды:

гг%о-- ьг (т. е. коды 11,00; 11,01; 11,00 и т. д.) для отрицательного остатка и коды:

XXXX

0,00х. . . ., 00,01х. . . .; ОО.Юх. . . .; 00,Их

ложительному остатку код 11,0 х, к отрицательному код 00,1 X ..... и в результате знаковые разряды нри вести к однорядному виду.:

На основании вышесказанного можно утXX

верждать, что если для кода хх, хх в первом знаковом разряде нуль, то носледующее действие совпадает с предыдущим. Действительно, если предыдущим действием было прибавление положительного нормализованного делителя, то, поскольку в этом случае второй знак остатка всегда «I, в знаковых разрядах будет код 10,00, т. е., полученный остаток отрицателен, и следующим действием должно быть снова прибавление положительного делителя. Если предыдущим действием было вычитание положительного делителя, то, поскольку в этом случае второй знак всегда совпадает с первым, в знаковых разрядах

будет код 00,, т. е. полученный остаток

положителен и следующим действием будет опять вычитание положительного нормализованного делителя (для отрицательного делителя действия обратны вышеописанным).

Кроме того, если первый знак «1, то второй знак обязательно будет «1, т. к. код «01 в знаковых разрядах получиться не может.

Таким образом, отпадает необходимость выработки второго знака остатка, что дает возможность упростить схему приведения переносов старших разрядов остатка и схему анализа знака остатка, если при определении следующего действия учитывать, результатом какого действия является анализируемый остаток. Таким образом, схема анализа вырабатывает сигналы, онределяющие еле/чующее действие по условиям, приведенным в таблице.

В этих случаях знак остатка неизвестен и производится только сдвиг очередного остатка влево на один разряд.

На фиг. 1 приведена блок-схема предложенного устройства.

Код делимого к началу операции находится Б параллельном сумматоре / без ценей сквозного переноса. Делитель засылается на регистр 2 делителя, где хранится в течение всей операции деления. Регистр 3 - буферный регистр, на который подается либо прямой, либо дополнительный код делителя для сложения его с кодом делимого или очередного остатка.

Характером передачи кода делителя с регистра 2 на регистр 5 управляют элементы 4, 5, включающие либо схемы «И 6 для передачи делителя прямым кодом, либо схемы «И 7 для передачи делителя дополнительным кодом. На фиг. 1 условно показаны схемы передачи для одного разряда, причем каждый разряд регистра 2 может иметь парафазные выходы (либо в схемах имеются дополнительные инверторы).

Схемы 8 анализа знака определяют срабатывание либо элемента 4, либо 5. На входы схем 8 подаются сигналы с выходом двух старших разрядов мантиссы с сумматора /, сигналы с выходов знакового разряда регистра 2 делителя и сигнал с полусумматора 9. вырабатывающего сумму переноса и сигнал поразрядной суммы для первого знакового разряда. Схемы 8 работают по вышеописанному алгоритму, для запоминания предыдущего действия на их входы подаются сигналы с элементов 4, 5.

Для формирования составляющих частного служат регистры 10, 11, на входы младших разрядов которых подаются сигналы с выходов элементов 4, 5.

После получения двухрядного очередного остатка в сумматоре / в схемах 8 и 9 вырабатываются сигналы, определяющие характер передачи, за это время в сумматоре / производится сдвиг очередного остатка на один разряд влево.

По сигналам с элементов 4, 5 производит ся передача кода делителя на регистр 3, причем возможны три случая: передача прямым кодом, передача дополнительным кодом и отсутствие передачи, когда знак остатка неизвестен.

После появления на регистре 3 кода делителя производится сложение этого кода с кодом очередного остатка, в результате чего получается новый очередной остаток. Таков элементарный цикл работы устройства. После получения нового остатка цикл повторяется. Для формирования частного сигнал с выхода элемента 4 поступает на вход младшего разряда регистра 10, а сигнал с выхода элемента 5 - на вход младшего разряда регистра 11, после чего производятся сдвиги кода в регистрах W и // на один разряд влево, синхронно со сдвигом очередного остатка в сумматоре I. В конце операции после получения заданного количества цифр частного код с регистров 10 и // передается в сумматор 1, где для вычисления истинного значения частного производится сложение кода, содержащегося в регистре 10, с дополнительным кодом составляющей частного в регистре //.

Процесс определения знака очередного остатка, а следовательно, и выполнение операции деления можно существенно ускорить, если суммирование кода старших разрядов очередного остатка с кодом старщих разрядов делителя производить с опережением по отношению к суммированию полноразрядныч кодов. Для этого следует ввести дополнительные суммирующие схемы для трех старших разрядов очередного осгетка, включая два старщих разряда мантиссы и первый знаковый разряд. Эти схемы должны управлятьс-i сигналами, определяющими характер передачи кода с регистра делителя в буферпый регистр, и в зависимости от этих сигналов производить либо сложение двухрядного кода очередного остатка (в трех старших разрядах) с кодом трех старших разрядов делителя, либо вычитание кода трех старших разрядов делителя из очередного остатке , либо сдвиг кода трех старших разрядов остатка влево на одип разряд, давая ва выхоXX

дах во всех трех случаях код вида х, хх.

Применение опережающего суммирования трех старших разрядов очередного остатка з устройстве деления, выполненном на элементах с двухфазным тактированием, дает возможность за каждый период тактирующего сигнала вырабатывать новый очередной остаток. Таким образом, в таком устройстве количество тактов (такт - период тактирующего сигнала), необходимое для получения частного, равно количеству разрядов частного.

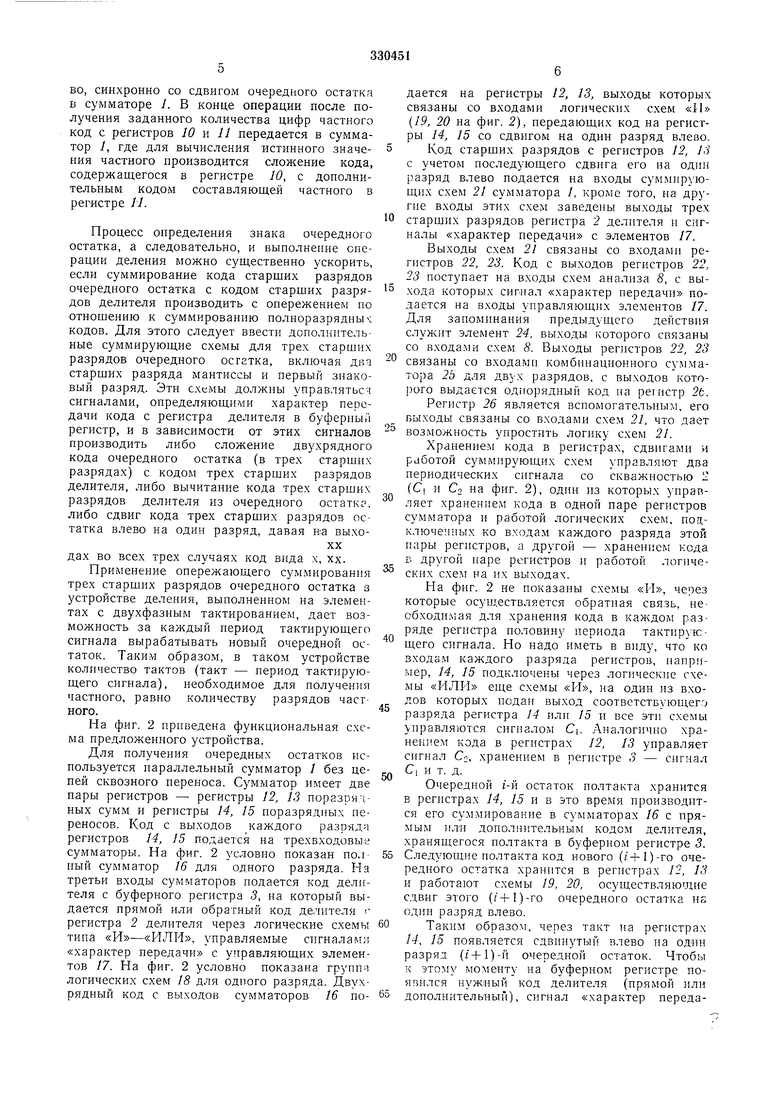

На фиг. 2 приведена функциональная схема предложепного устройства.

Для получения очередных остатков используется параллельный сумматор / без цепей сквозного переноса. Сумматор имеет две пары регистров - регистры 12, 13 поразрядных сумм и регистры 14, 15 поразрядных переносов. Код с выходов каждого разряда регистров 14, 15 подается на трехвходовые сумматоры. На фиг. 2 условно показан полный сумматор 16 для одного разряда. На третьи входы сумматоров подается код делителя с буферного регистра 3, на который выдается прямой или обратный код делителя регистра 2 делителя через логические схемы типа «И -«ИЛИ, управляемые сигналами «характер передачи с управляющих элементов 17. На фиг. 2 условно показана групп логических схем 18 для одного разряда. Двухрядный код с выходов сумматоров 16 подается на регистры 12, 13, выходы которых связаны со входами логических схем «П (19, 20 на фиг. 2), передающих код на регистры 14, 15 со сдвигом на один разряд влево.

Код старших разрядов с регистров 12, 13 с учетом последующего сдвига его на один разряд влево подается на входы сум.мирующих схем 21 сумматора /, кроме того, на другие входы этих схем заведены выходы трех старщих разрядов регистра 2 делителя и сигналы «характер передачи с элементов 17.

Выходы схем 21 связаны со входами регистров 22, 23. Код с выходов регистров 22, 23 поступает на входы схе.м анализа S, с выхода которых сигнал «характер передачи подается на в.ходы управляющих элементов 17. Для запоминания предыдущего действия служит элемент 24, выходы которого связаны со входами схем 8. Выходы регистров 22, 23 связаны со входами комбинационного сумматора 26 для разрядов, с выходов которого выдается одпорядный код на регистр 26.

Регистр 26 является вспомогательным, его выходы связаны со входами схе.м 21, что дает воз.можность упростить логику схем 21.

Хранением кода в регистрах, сдвигами и работой суммирующих схем управляют два периодически.х сигнала со скважностью 2 (С| и Со на фиг. 2), один из которых управляет хранением кода в одной паре регистров сумматора и работой логических схем, подключенных ко входам каждого разряда этой пары регистров, а другой - хранением кода D другой паре регистров и работой логических схем на их выходах.

На фиг. 2 не показаны схемы «П, через которые осуш.ествляется обратная связь, пеобходиа1ая для хранения кода в каждом разряде регистра половину периода тактирующего сигнала. Но надо иметь в виду, что ко входа.м каждого разряда регистров, например, 14, 15 подключены через логические схемы «ИЛИ еще схемы «И, на один из входов которых выход соответствующего разряда регистра 4 или 15 и все эти схемы управляются cигнaлo Сь у налогично хранением кода в регистрах /2, 13 управляет сигнал С, хранением в регнстре 3 - сигнал С) и т. д.

Очередной i-й остаток полтакта хранится в регистрах 14, 15 и в это время нроизводится его суммирование в сумматорах 16 с прямым или дополнительным кодом делителя, хранящегося полтакта в буферном регистре 3. Следующие полтакта код нового (г-|-1)-го очередного остатка хранится в регистрах 12, 13 и работают схемы 19, 20, осуществляющие сдвиг этого (г + 1)-го очередного остатка на один разряд влево.

Таким образом, через такт на регистрах 14. 15 появляется сдвинутый влево на один разряд (г+1)-й очередной остаток. Чтобы к этому моменту на буферном регистре появился нужный код делителя (прямой или дополнительный), сигнал «характер передачи, определяющий действие с (i + 1)-м очередным остатком, должен появиться на полтакта раньше, т. е. одновременно с появлением на регистрах 12, 13 еще не сдвинутого влево (t + 1)-го очередного остатка. Поскольку энак остатка (сигнал «характер передачи) определяется путем анализа неполностью приведенного кода старших разрядов остатка, то этот код вырабатывается на полтакта раньще, чем в регистрах 12, 13, т. е. схема 21 производит суммирование и неполное приведение кода трех старщих разрядов на полтакта раньше, чем сумматоры 16. Для этого код t-ro очередного остатка берется с регистров 12, 13 с учетом последующего сдвига его влево, т. е. для вычисления поразрядной суммы в п-ы разряде (i + 1)-го очередного остатка иужио сложить (или вычесть) сумму и перенос в (п-1)-м разряде L-ro очередного остатка с цифрой в п.-м разряде делителя. Для вычисления переноса в п-й разряд (i + 1)-го очередного остатка нужно сложить (или вычесть) сумму и перенос в (п - 2)-м разряде г-го остатка с цифрой в (п-1)-м разряде делителя. Поэтому на входы схем 21 подается код с разрядов регистров 12, 13, а также код с разрядов регистра делителя и сигналы «характер передачи, в зависимости от которых в схемах 21 производится либо сложение кодов старших разрядов i-ro очередного остатка с кодом старших разрядов делителя, либо вычитание кода старших разрядов делителя из кода старших разрядов t-ro очередного остатка, либо сдвиг i-ro очередного остатка на одии разряд влево.

Схемы 21 вырабатывают приведенный код в первом знаковом разряде (t+l)-ro очередного остатка, код поразрядных сумм в л-ом и (п-1)-м разрядах и код поразрядных переносов в п-й и (п-1)-й разряды (i + 1)-го очередного остатка (регистры 22, 23) через полтакта после появления кода г-го очередного остатка на регистрах 12, 13. Коды с регистров 22, 23 поступают на входы анализирующих схем 6, которые выдают сигналы «характер передачи на управляющие элементы 4 одновременно с появлением на регистpax 12, 13 полноразрядного кода (t + 1)-го очередного остатка, что дает возможность к моменту появления на регистрах 14, 15 сдвинутого (i + 1)-го очередного остатка передать прямой или дополнительный код делителя на регистр 3, после чего цикл повторяется, вырабатывается (i + 2)-и очередной остаток и т. д.

Предмет изобретения

Устройство для деления двоичных чисел без восстановления остатка, состоящее из параллельного сумматора без цепей сквозного переноса, регистра делителя, буферного регистра, включенного между сумматором и регистром делителя, схемы анализа знака очередного остатка, подсоединенной к сумматору, и регистров для формирования частного, отличающееся тем, что, с целью повышения быстродействия, сокращения оборудования я упрощения устройства, оно содержит одноразрядные полные сумматоры, выходы которых подключены ко входам первого регистра запоминания поразрядных сумм и поразрядных переносов, выходы первого регистра запоминания поразрядных сумм и поразрядных переносов соединены со входами сдвигающего регистра, выходы которого подключены ко входам второго регистра запоминания поразрядных сумм и переносов, а выходы второго регистра запоминания поразрядных сумм и переносов подсоединены ко входам полных сумматоров, выходы старших разрядов первого регистра запоминания поразрядных сумм и

0 переносов соединены с первыми входами суммирующих схем, вторые входы которых подключены к выходам старших разрядов делителя, а выходы суммирующих схем подсоединены ко входу схемы анализа знака остатка.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1983 |

|

SU1141403A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU898423A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления двоичных чисел | 1988 |

|

SU1617437A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Делительное устройство | 1984 |

|

SU1239711A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Конвейерное вычислительное устройство | 1989 |

|

SU1693601A1 |

Даты

1972-01-01—Публикация