112

Изобретение относится к области вычислительной техники и предназначено для деления чисел, представленных в системах счисления с основанием .

Цель изобретения - повьшение быстродействия ,

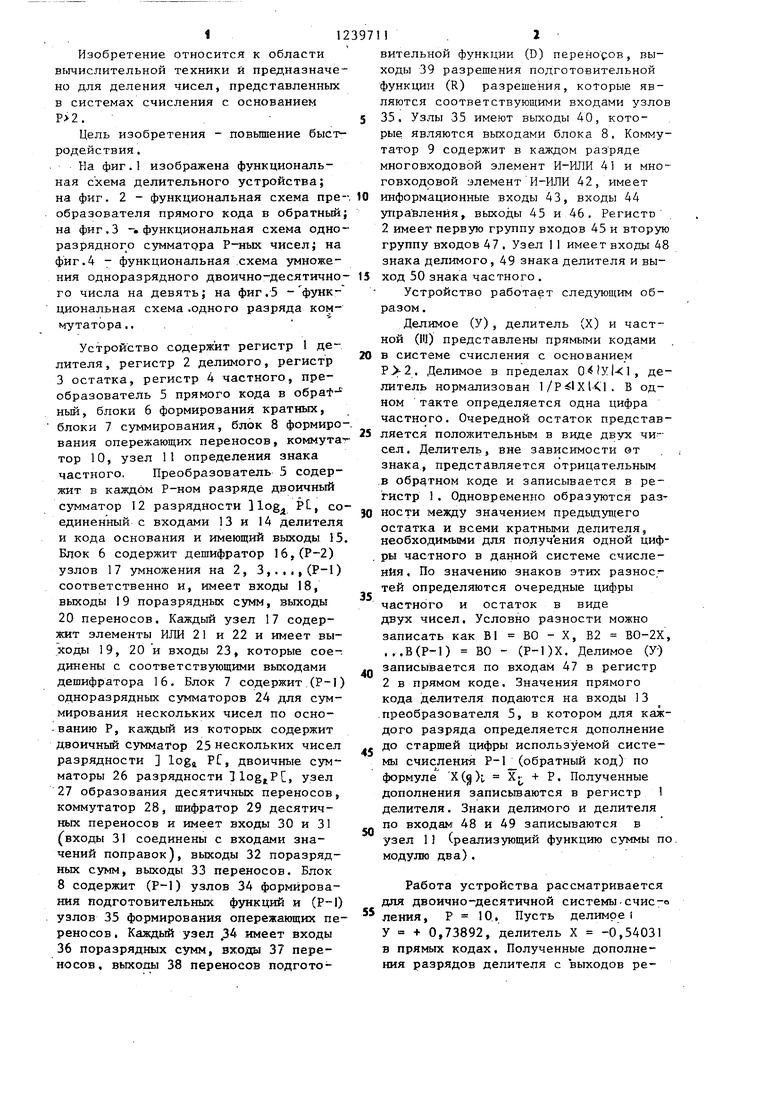

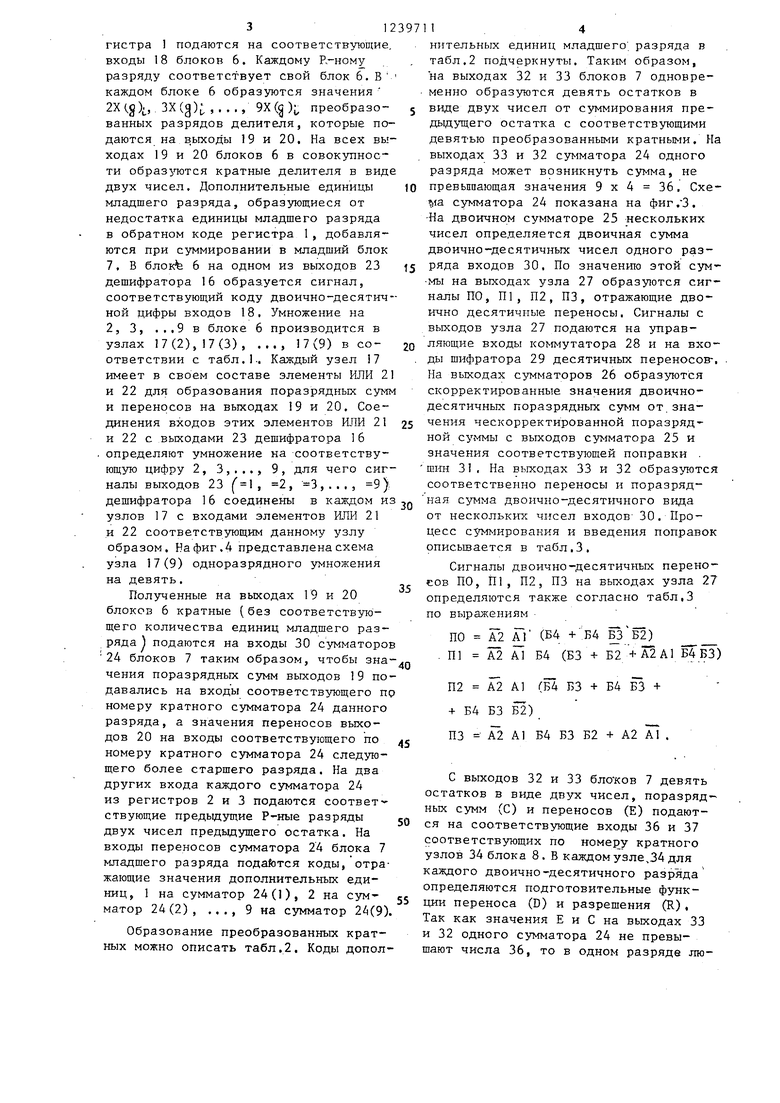

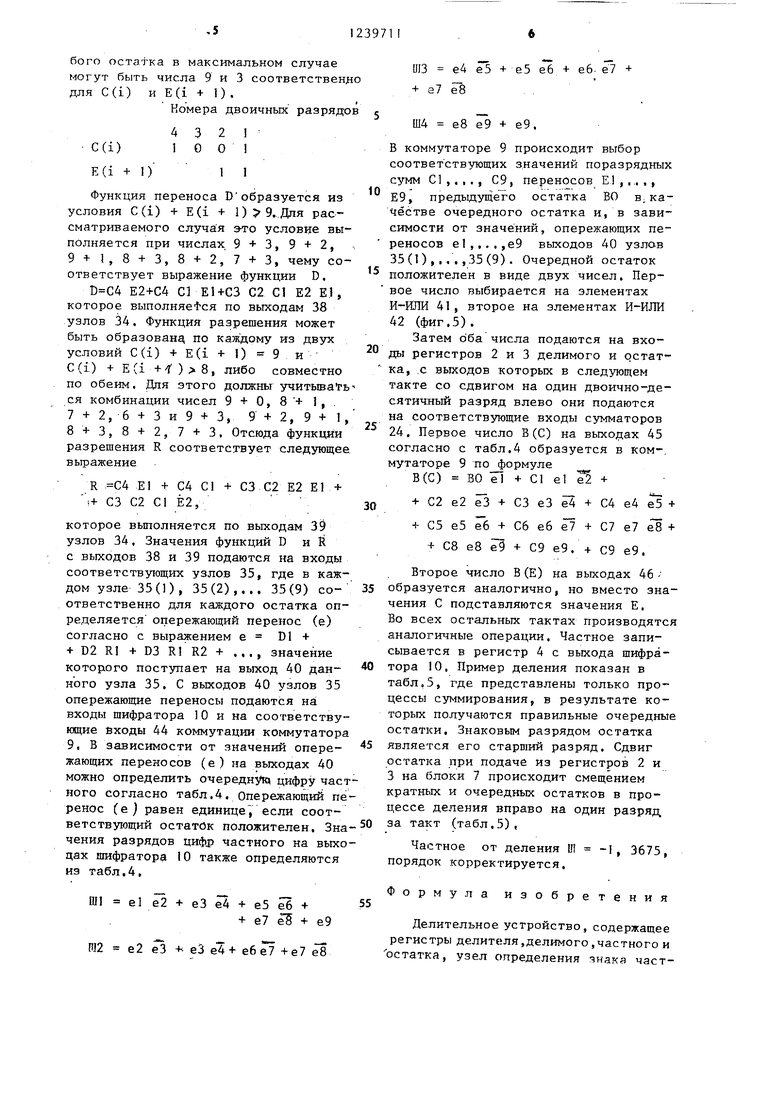

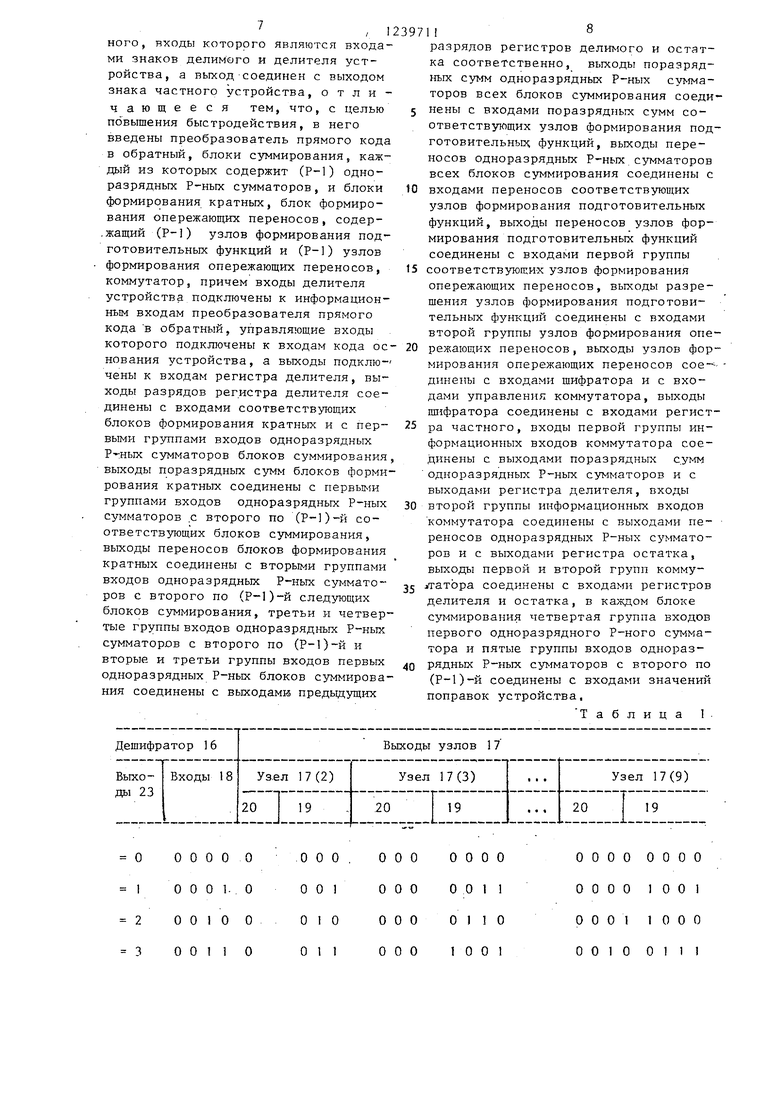

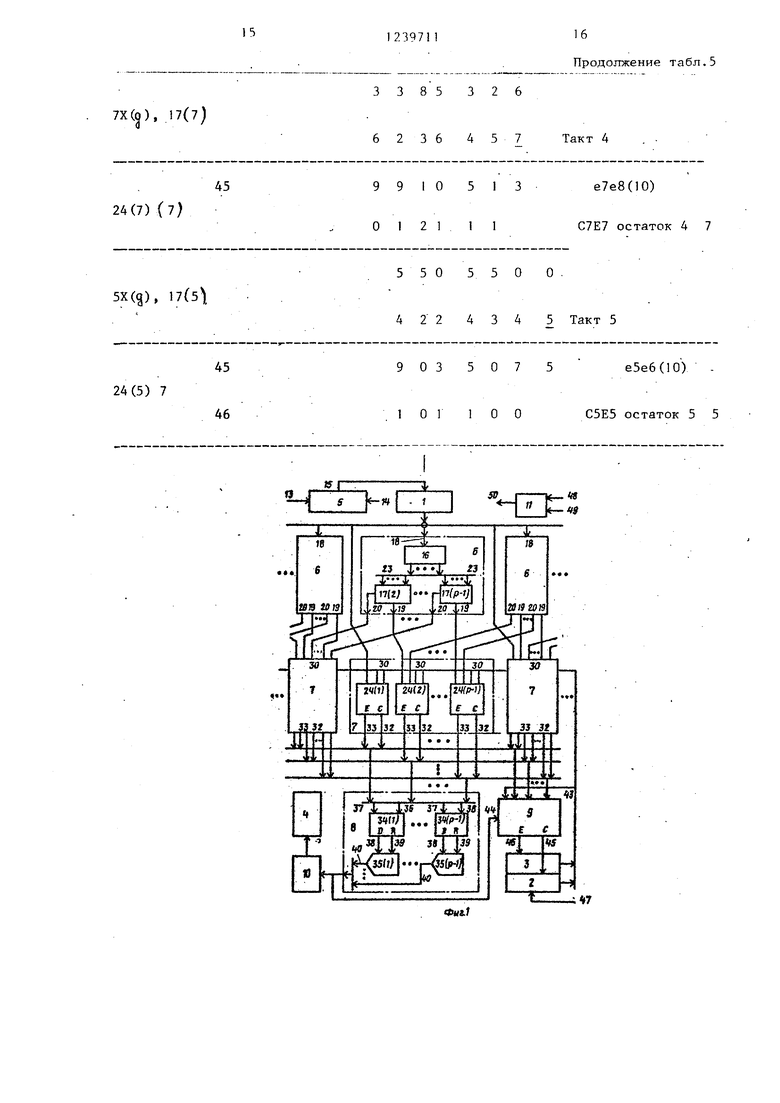

На фиг.1 изображена функциональная схема делительного устройства; на фиг. 2 - функциональная схема преобразователя прямого кода в обратный; на фиг.З -«функциональная схема одно- разрядног о сумматора Р-ных чисел; на фиг.4 - функциональная .схема умножения одноразрядного двоично-десятично- го числа на девять; на фиг.5 - функциональная схема .одного разряда коммутатора,. .

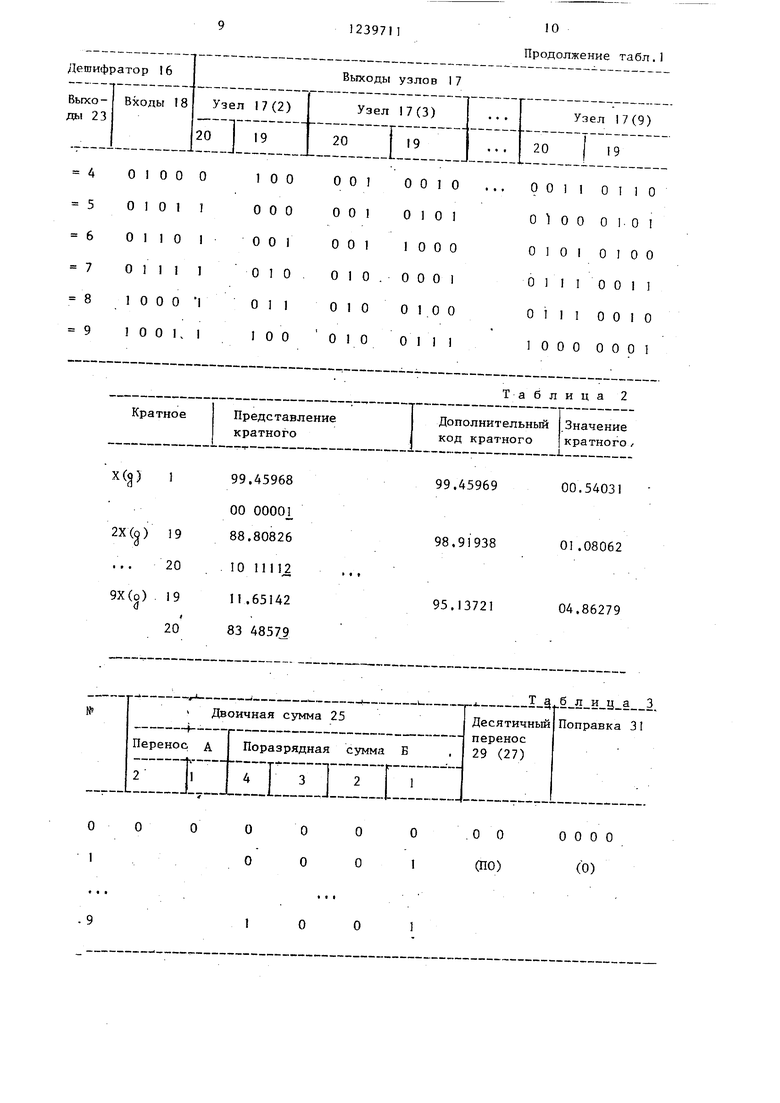

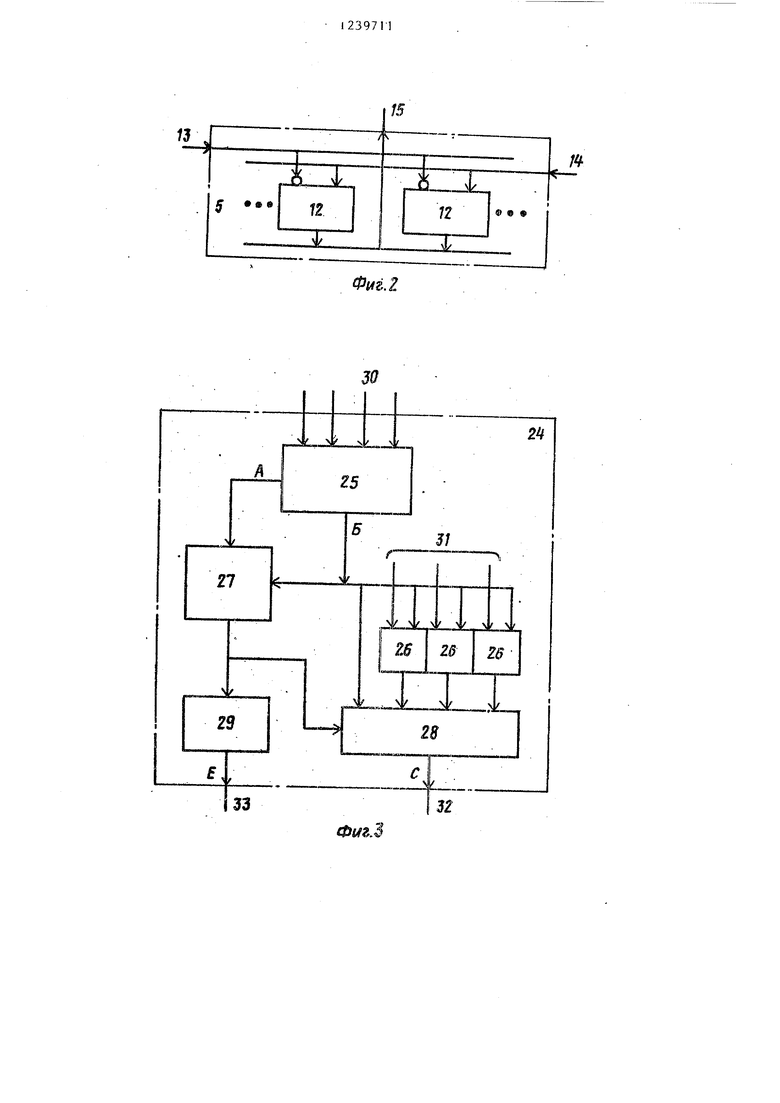

Устройство содержит регистр 1 делителя, регистр 2 делимого, регистр 3 остатка, регистр 4 частного, преобразователь 5 прямого кода в o6pat- ный, блоки 6 формирования кратных, блоки 7 суммирования, блок 8 формирования опережающих переносов, коммута тор 10, узел 11 определения знака частного, Преобразователь 5 содержит в каждом Р-ном разряде двоичный сзт матор 12 разрядности 1о§д РС, соединенный с входами 13 и 14 делителя и кода основания и имеющий выходы 15. БЛОК 6 содержит дешифратор 16,(Р-2) узлов 17 умножения на 2, 3,.,.,(Р-1)

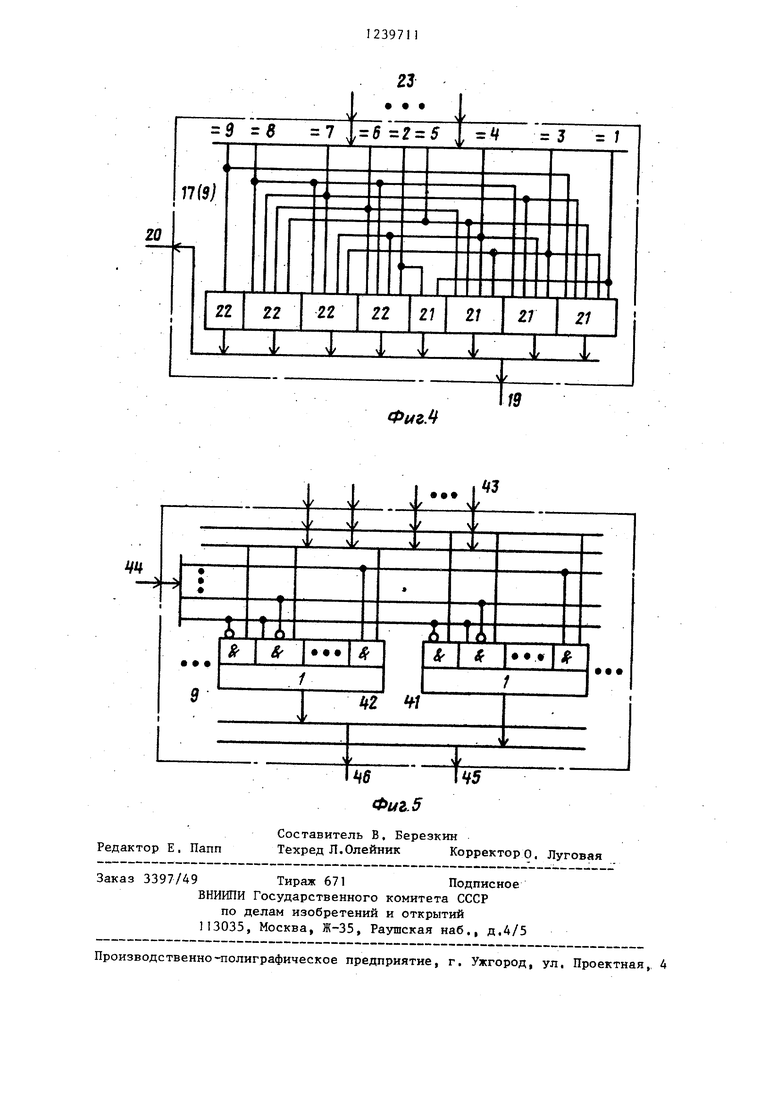

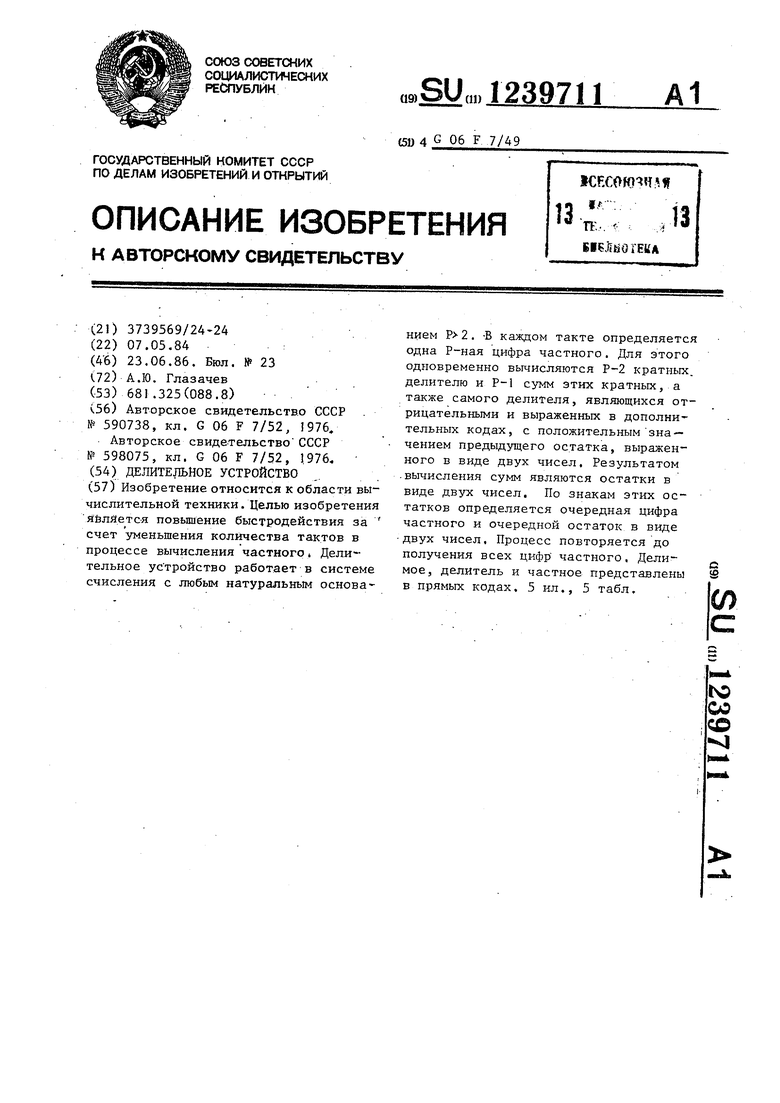

соответственно и, имеет входы 18, выходы 19 поразрядных сумм, выходы 20 переносов. Каждый узел 17 содержит элементы ИЛИ 21 и 22 и имеет выходы 19, 20 и входы 23, которые сое-- динены с соответствующими выходами дешифратора 16. Блок 7 содержит.(Р-1) одноразрядных сумматоров 24 для суммирования нескольких чисел по осно- -ванию Р, каждый из которых содержит двоичный сумматор 25 нескольких чисел разрядности 3 loga PC, двоичные сумматоры 26 разрядности , узел 27 образования десятичных переносов, коммутатор 28, шифратор 29 десятичных переносов и имеет входы 30 и 31 {входы 3 соединены с входами значений поправок), выходы 32 поразрядных сумм, выходы 33 переносов. Блок 8 содержит (Р-1) узлов 34 формирования подготовительных функхщй и (Р-1) узлов 35 формирования опережающих переносов. Каждый узел .34 имеет входы 36 поразрядных сумм, входы 37 переносов, выходы 38 переносов подгото

5

0

5

0

5

0

5

0

5

1 . 2

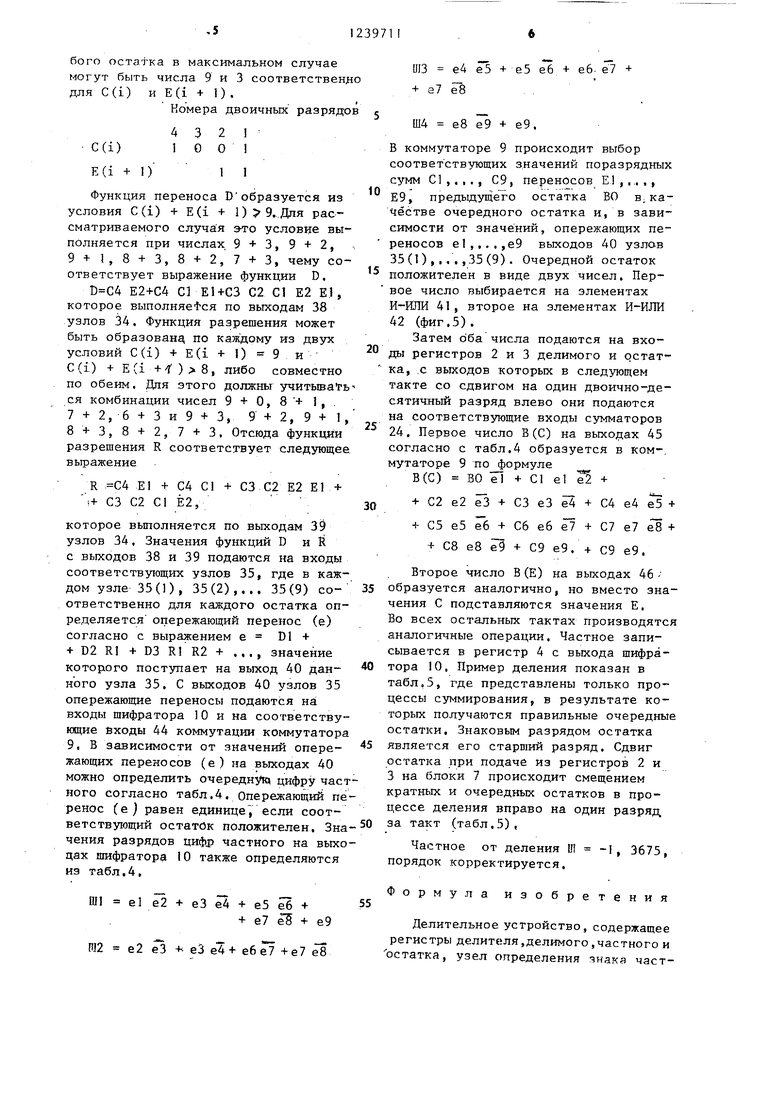

витальной функции (D) переноров, выходы 39 разрешения подготовительной функции (R) разрешения, которые являются соответствующими входами узлов 35. Узлы 35 имеют выходы 40, которые; являются выходами блока 8, Коммутатор 9 содержит в каждом разряде многовходовой элемент И-ИЛИ 41 и мно- говходрвой элемент И-ИЛИ 42, имеет информационные входы 43, входы 44 упра вленйя, выходы 45 и 46, Регисто 2 имеет первую группу входов 45 и вторую группу входов 47 , Узел 1 1 имеет входы 48 знака делимого, 49 знака делителя и выход 50 знака частного .

Устройство работает следующим образом.

Дел:ямое (У), делитель (X) и частной (Щ) представлены прямыми кодами в системе счисления с основанием , Делимое в пределах , делитель нормализован . В одном такте определяется одна цифра частного. Очередной остаток представляется положительным в виде двух чи-- сел. Делитель 5 вне зависимости от знака, представляется отрицательным .в обратном коде и записывается в регистр 1. Одновременно образуются разности между значением предыдущего

остатка и всеми кратными делителя, необходимыми дл.я получения одной цифры частного в данной системе счисления , По значению знаков этих разнос, тей определяются очередные цифры частного и остаток в виде двух чисел. Условно разности можно записать как В1 ВО - X, В2 ВО-2Х, ,,.В(Р-1) ВО - (Р-1)Х. Делимое (У-) записывается по входам 47 в регистр 2 в прямом коде. Значения прямого кода делителя подаются на входы 13 .преобразователя 5, в котором для каждого разряда определяется дополнение до старшей цифры используемой системы счисления Р-1 (обратный код) по формуле X(|)t Xj + P. Полученные дополнения записьтаются в регистр 1 делителя. Знаки делимого и делителя по входам 48 и 49 записываются в узел I1 (реализующий функцию суммы по. модулю два).

Работа устройства рассматривается для двоично-десятичной системы-счис-о ления, Р 10.. Пусть делимое У + 0,73892, делитель X -0,54031 в прямых кодах. Полученные дополнения разрядов делителя с выходов ре312

гистра 1 подаются на соответствуюпше. входы 18 блоков 6. Каждому Р -ному разряду соответствует свой блок 6. В каждом блоке 6 образуются значения 2Х(§),, 3X(g),..., 9Х();, преобразо- ванных разрядов делителя, которые подаются на в.ыходы 19 и 20. На всех выходах 19 и 20 блоков 6 в совокупности образ тотся кратные делителя в виде двух чисел. Дополнительные единицы младшего разряда, образующиеся от недостатка единицы младшего разряда в обратном коде регистра 1, добавляются при суммировании в младший блок 7, В блок 6 на одном из выходов 23 дешифратора 16 образуется сигнал, соответствующий коду двоично-десятичной цифры входов 18, Умножение на 2, 3, ...9 в блоке 6 производится в узлах 17(2), 17(3), ..., 17(9) в со- ответствии с табл.1.. Каждый узел 17 имеет в своем составе элементы ИЛИ 21 и 22 для образования поразрядных сумм и переносов на выходах 19 и 20. Соединения входов этих элементов ИЛИ 21 и 22 с выходами 23 дешифратора 16 определяют умножение на соответствующую цифру 2, 3,..., 9, для чего сигналы выходов 23 (-, 2, -3,..., 9)i дешифратора 16 соединены в каждом из узлов 17 с входами элементов ИЛИ 21 и 22 соответствующим данному узлу образом. На фиг.4 представлена схема узла 17(9) одноразрядного умножения на девять.

Полученные на выходах 19 и 20 блоков 6 кратные (без соответствующего количества единиц младшего разряда подаются на входы 30 сумматоров 24 блоков 7 таким образом, чтобы значения поразрядных сумм выходов 19 подавались на входы соответствующего пр номеру кратного сумматора 24 данного разряда, а значения переносов выходов 20 на входы соответствующего по номеру кратного сумматора 24 следующего более старшего разряда. На два других входа каждого сумматора 24 из регистров 2 и 3 подаются соответ ствующие предыдущие Р-ные разряды двух чисел предьщущего остатка. На входы переносов сумматора 24 блока 7 младшего разряда подаются коды, отражающие значения дополнительных единиц, 1 на сумматор 24(1), 2 на сум- матор 24(2), ..., 9 на сумматор 24(9).

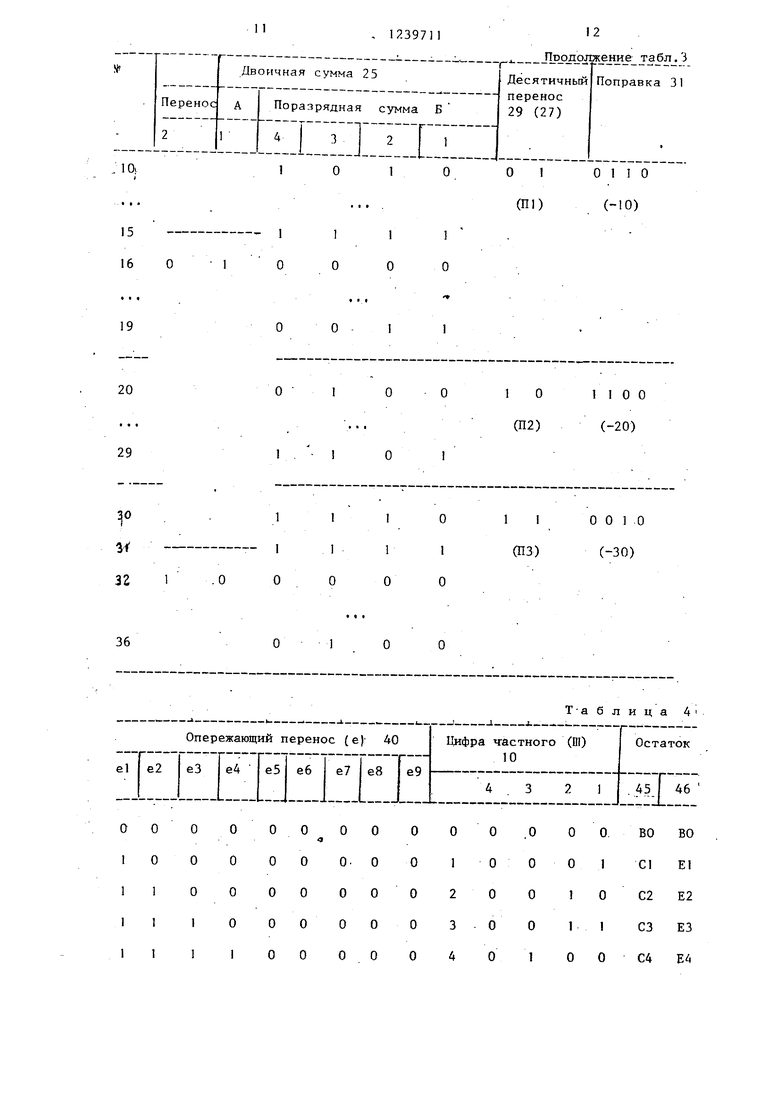

Образование преобразованных кратных можно описать табл .2. Коды допол1.4

нительных единиц младшего; разряда в табл.2 подчеркнуты. Таким образом, на выходах 32 и 33 блоков 7 одновременно образуются девять остатков в виде двух чисел от суммирования предьщущего остатка с соответствующими девятью преобразованными кратными. На выходах 33 и 32 cjn-шатора 24 одного разряда может возникнуть сумма, не превьтающая значения 9 х 4 36. Схе- iia cy fMHTopa 24 показана на фиг. З. На двоичном сумматоре 25 нескольких чисел определяется двоичная сумма двоично-десятичных чисел одного разряда входов 30. По значению этой сум- мы на выходах узла 27 образуются сигналы ПО, П1, П2, ПЗ, отражающие двоично десятичные переносы. Сигналы с выходов узла 27 подаются на управляющие входы коммутатора 28 и на входы шифратора 29 десятичных переносов-. . На выходах сумматоров 26 образуются скорректированные значения двоично- десятичных поразрядных сумм от.значения нескорректированной поразрядной суммы с выходов сзт-1матора 25 и значения соответствующей поправки .

шин 31. На выходах 33 и 32 образуются соответственно переносы и поразрядная сумма двоично-десятичного вида от нескольких чисел входов 30. Процесс с т шрования и введения поправок описьшается в табл.3.

Сигналы двоично-десятичных переносов ПО, П1, П2, ПЗ на выходах узла 27 определяются также согласно табл.З по выражениям

ПО А2 М (Б4 + Б4 )

. П1 А2 А Б4 (БЗ + Б2 +А2А1 Б4БЗ)

П2 А2 А1 (Б4 БЗ + Б4 БЗ +

+ Б4 БЗ Б2)

ПЗ А2 А Б4 БЗ Б2 + А2 AI .

С выходов 32 и 33 бло ков 7 девять остатков в виде двух чисел, поразрядных сумм (С) и переносов (Е) подаются на соответствующие входы 36 и 37 соответствующих по номеру кратного узлов 34 блока 8. В каждом узле,34 для каждого двоично-десятичного разряда определяются подготовительные функции переноса (D) и разрешения (R), Так как значения Е и С на выходах 33 и 32 одного сумматора 24 не превышают числа 36, то в одном разряде любого остатка в максимальном случае могут быть числа 9 и 3 соответственно для C(i) и E(i + 1) .

Номера двоичных разрядов

4 3 2 1 C(i) 100

E(i + 1)

1 I

Функция переноса D образуется из условия C(i) + E(i + 1) 9. ,1ля рассматриваемого случа я это условие выполняется при числах 9+3,9+2, 9+1,8+3,8+2,7+3, чему соответствует выражение функции D.

Е2+С4 С1 Е1+СЗ С2 С1 Е2 El, которое выпoлняetcя по выходам 38 узлов 34. Функция разрешения может быть образован по каждому яз двзгх условий С(i) + Е(i + 1) 9 и C(i) + E(i + f)8, либо совместно по обеим. Для этого должны учитывать ся комбинации чисел 9 + 0,8 +,. 7 + 2, 6 + 3 и 9 + 3, 9 + 2, 9 + 1, 8+3,8+2,7+3. Отсюда функции разрешения R соответствует следующее вьфажение

R С4 EI + С4 С1 + СЗ С2 Е2 Е1 + |+ СЗ С2 CI Ё2,

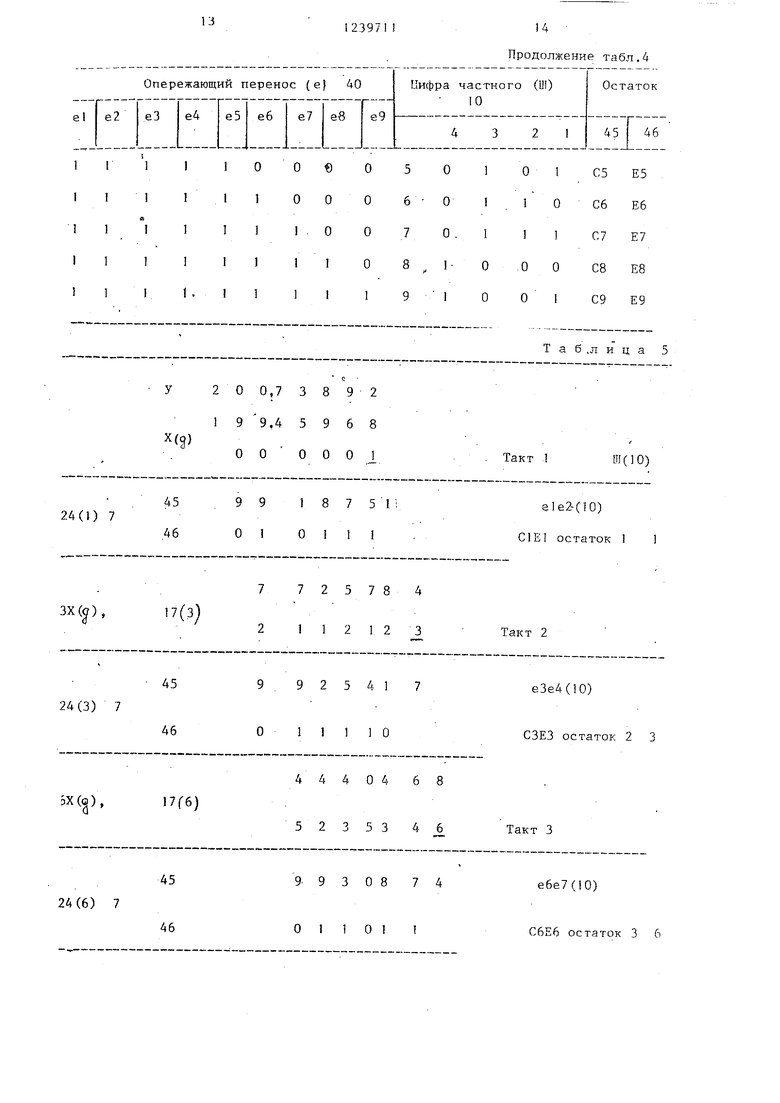

которое выполняется по выкодам 39 узлов 34. Значения функций D и R с выходов 38 и 39 подаются на входы соответствующих узлов 35, где в каждом узле 35 (1 ), 35(2),.., 35(9) со- ответственно для каждого остатка определяется опережающий перенос (е) согласно с выражением е D1 + + D2 R1 + D3 R R2 + .,., значение которого поступает на выход 40 дан- ного узла 35. С выходов 40 узлов 35 опережающие переносы подаются на входы шифратора IО и на соответствующие входы 44 коммутации коммутатора 9. В зависимости от значений опере- жающих переносов (е) на выходах 40 можно определить очередную цифру частного согласно табл.4. Опережающий перенос fеj равен единице если соответствующий остаток положителен. Зна чения разрядов цифр частного на выходах шифратора 10 также определяются из табл.4,

Ш1 el ё2 + еЗ ё4 + е5 е6 +

+ е7 е + е9

Ш2 е2 еЗ + еЗ е4 + е6 еТ +е7 ев

ШЗ е4 е5 + е5 е6 + е6. е7 + + е7 ё8

Ш4 е8 69 + е9.

В коммутаторе 9 происходит выбор соответ ствующих значений поразрядных сумм С1,..., С9, переносов Е ,...., E9J предьщущего остатка ВО в. качестве очередного остатка и, в зависимости от значений, опережающих переносов el,.,.,e9 выходов 40 узлов 35(1),...,35 (9). Очередной остаток положителен в виде двух чисел. Первое число выбирается на элементах И-ЮШ 41 , второе на элементах И-ИЛИ 42 (фиг.5).

Затем о ба числа подаются на входы регистров 2 и 3 делимого и остатка, .с выходов которых в следующем такте со сдвигом на один двоично-десятичный разряд влево они подаются на соответствующие входы сумматоров 24. Первое число В (С) на выходах 45 согласно с табл.4 образуется в ком-, мутаторе 9 по формуле

В(С) ВО 1 + С1 el е +

+ С2 е2 ёЗ + СЗ еЗ ё4 + С4 е4 е5 + + С5 е5 е6 + С6 е6 ё7 + С7 е7 ё + + С8 е8 ё 9 + С9 е9. + С9 е9.

Второе число В (Е) на выходах 46 - образуется аналогично, но вместо значения С подставляются значения Е. Во всех остальных тактах производятся аналогичные операции. Частное записывается в регистр 4 с выхода шифратора 10. Пример деления показан в табл.5, где представлены только процессы су1чмирования, в результате которых получаются правильные очередные остатки. Знаковым разрядом остатка является его старший разряд. Сдвиг остатка при подаче из регистров 2 и 3 на блоки 7 происходит смещением кратных и очередных остатков в процессе деления вправо на один разряд за такт (табл.5),

Частное от деления UI -I, 3675, порядок корректируется.

Формула изобретения

Делительное устройство, содержащее регистры делителя,делимого,частного и остатка, узел определения частного, входы которого являются входами знаков делимого и делителя устройства, а выход соединен с выходом знака частного устройства, отличающееся тем, что, с целью по вьпления быстродействия, в него введены преобразователь прямого кода в обратный, блоки суммирования, каждый из которых содержит (Р-1) одноразрядных Р-ных сумматоров, и блоки формирования кратных, блок формирования опережающих переносов, содер- .жащий (Р-1) узлов формирования подготовительных: функций и (Р-1) узлов формирования опережающих переносов, коммутатор, причем входы делителя устройства подключены к информационным входам преобразователя прямого кода в обратный, управляющие входы которого подключены к входам кода основания устройства, а выходы подключены к входам регистра делителя, выходы разрядов регистра делителя соединены с входами соответствующих блоков формирования кратных и с первыми группами входов одноразрядных сумматоров блоков суммирования выходы поразрядных сумм блоков формирования кратных соединены с первьми группами входов одноразрядных Р-ных сумматоров .с второго по (Р-1)-й со- ответствзпощих блоков суммирования, выходы переносов блоков формирования кратных соединены с вторыми группами входов одноразрядных Р-ных сумматоров с второго по (Р-1)-й следующих блоков сзгммировання, третьи и четвертые группы входов одноразрядных Р-ных сумматоров с второго по (Р-1)-и и вторые и третьи группы входов первых одноразрядных Р-ных блоков суммирования соединены с выходами предыдущ1-гх

разрядов регистров делиьюго и остатка соответственно, выходы поразрядных сумм одноразрядных Р-ных сумматоров всех блоков суммирования соединены с входами поразрядных сумм соответствующих узлов формирования подготовительных; функций, выходы переносов одноразрядных Р-ных сумматоров всех блоков суммирования соединены с

входами переносов соответствующих узлов формирования подготовительных функций, выходы переносов узлов формирования подготовительных функций соединены с входами первой группы

соответствующих узлов формирования опережающих переносов, выходы разре- щения узлов формирования подготовительных функций соединены с входами второй группы узлов формирования опережающих переносов, выходы узлов формирования опережающих переносов динены с входами щифратора и с входами управления коммутатора, выходы шифратора соединены с входами регистра частного, входы первой группы информационных входов коммутатора соединены с выходами поразрядных cyNfM одноразрядных Р-ных сумматоров и с выходами регистра делителя, входы

второй группы информационных входов коммутатора соединены с выходами переносов одноразрядных Р-ных сумматоров и с выходами регистра остатка, выходы первой и второй групп комму- лтатЬра соединены с входами регистров делителя и остатка, в каждом блоке суммирования четвертая группа входов первого одноразрядного Р-ного тора и пятые группы входов одноразрядных Р-ных сумматоров с второго по (Р-1)-й соединены с входами значений поправок устройства,

Таблица 1 .

00000000

00001001

00011000 00100111

О

О

о

о о

. 9

о

1239711

10

Продолжение табл.1

о

I

о о

(ПО)

0000 (0)

19 20

f

29

f

зг

36

Т-аблица 4

u

123971

Х(9}

20 0,7 3 8 92

1 9 9.4 5968

О О О О О

ЗХ

(),(3}

7 725784

2 112123

45

9 92541 7

24(3) 7

46

011110

44404 68

5Х(),ПСб)

52353 46

45

24(6) 7

46

0110 1

Продолжение табл,4

Такт .1

Ш(10)

Такт 2

еЗе4(10)

СЗЕЗ остатор; 2 3

Такт 3

308 74

е6е7(10)

С6Е6 остаток 3 6

Продолжение табл.5

.Z

Ф«/а.З

Фиг.5

Составитель В, Березкин

Редактор Е. Папп

Техред Л.Олейник

Заказ 3397/49 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.А/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,, 4

Ф14гМ

19

Корректоре. Луговая

| название | год | авторы | номер документа |

|---|---|---|---|

| Делительное устройство | 1986 |

|

SU1335980A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1234831A1 |

| Устройство для извлечения квадратного корня с перестраиваемым основанием системы счисления | 1985 |

|

SU1363204A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления десятичных чисел | 1984 |

|

SU1241235A1 |

| Устройство для деления | 1985 |

|

SU1282117A1 |

| УСТРОЙСТВО ДЛЯ ДЕЛЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU330451A1 |

Изобретение относится к области вычислительной техники. Целью изобретения явлйется повышение быстродействия за счет уменьшения количества тактов в процессе вычисления частного. Делительное ус тройство работает в системе счисления с любым натуральным основа-нием Р 2. -В каждом такте определяется одна Р-ная цифра частного. Для этого одновременно вычисляются Р-2 кратных, делителю и Р-1 сумм этих кратных, а также самого делителя, являющихся отрицательными и выраженных в дополнительных кодах, с положительным значением предыдущего остатка, выраженного в виде двух чисел. Результатом вьгчисления сумм являются остатки в виде двух чисел. По знакам этих остатков определяется очередная цифра частного и очередной остаток в виде двух чисел. Процесс повторяется до получения всех цифр частного. Делимое, делитель и частное представлены в прямых кодах. 5 ил., 5 табл. с (О ts: 00 со

| Устройство для деления | 1976 |

|

SU590738A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для деления | 1976 |

|

SU598075A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-23—Публикация

1984-05-07—Подача