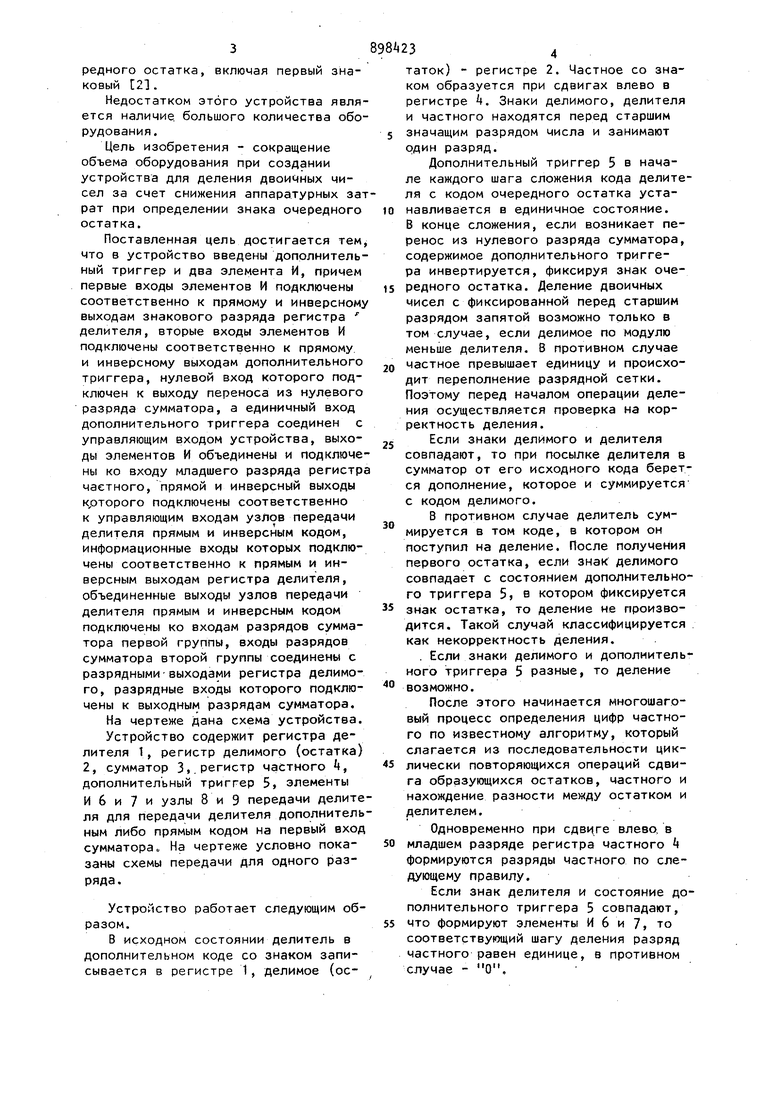

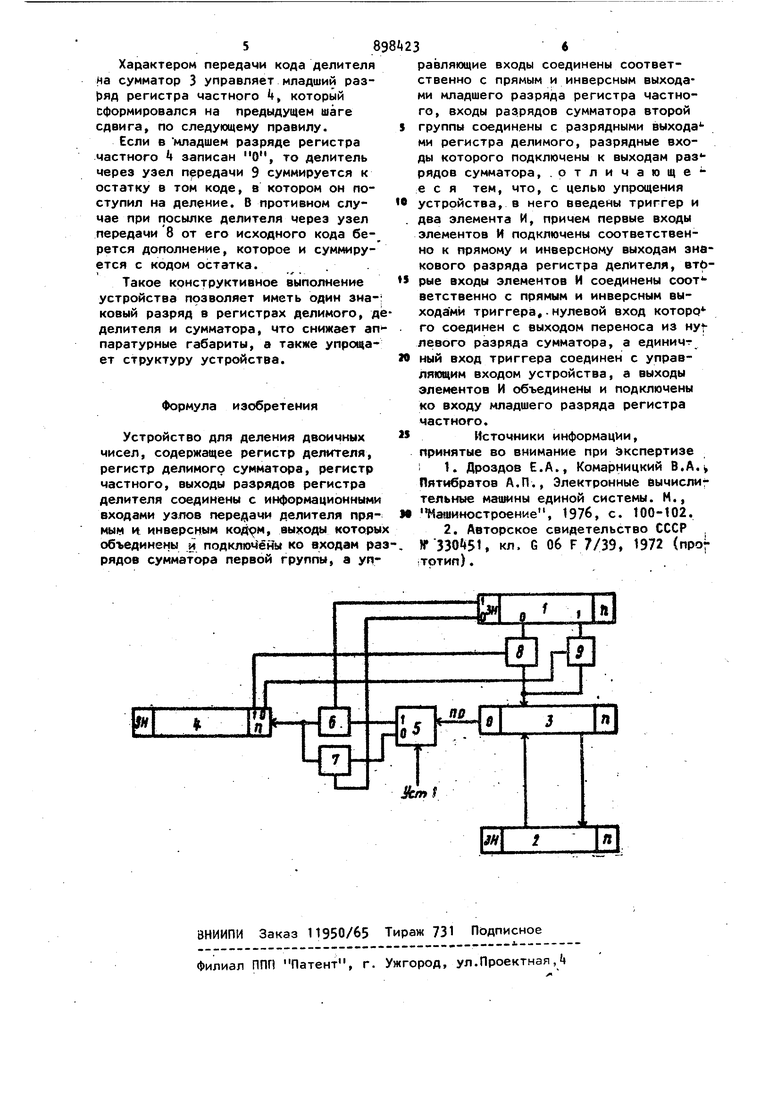

Изобретение относится к вычислительной технике и может быть использо вано в частности, для аппаратной реализации операции деления в специализированных вычислительных кашинах, работающих в дв(5ичной системе счисления с фиксированной запятой с использованием дополнительных кодов отрицательных операндов. Известно устройство для деления без восстановления остатка с учетом алгебраических знаков операндов со сдвигом остатка и частного влево на один разряд, содержащее регистры делимого и делителя, сумматор, регистр частного и схемы анализа знака очередного остатка. В данном устройстве для сокращения времени выполнения деления во всех определяемых остатках, кроме конечного, не производится полное приведение переносов. Каждый очередной остаток получается в двухрядном коде, состоящем из кодов поразрядной суммы и поразрядных переносов Для определения знака остатка полное приведение переносов осуществляется только в старших его разрядах. При этом на величину делителя налагается определенное огранич ение, а именно делитель должен быть нормализован. Все это дает возможность, введя дополнительный знаковый разряд, определить знак остатка путем полного приведения переносов лишь в четырех старших разрядах его модифицированного кода С1 . Недостатком этого устройства является избыточность аппаратуры. Наиболее близким к изобретению техническим решением является устройство для деления двоичных чисел, содержащее регистры делимого и делителя, сумматор, буферный регистр, схему анализа знака очередного остатка, регистр частного, в котором знак очередного остатка определяется путем анализа трех старших разрядов очередного остатка, включая первый знаковый С2 . Недостатком этого устройства явля ется наличие, большого количества обо рудования. Цель изобретения - сокращение объема оборудования при создании устройства для деления двоичных чисел за счет снижения аппаратурных за рат при определении знака очередного остатка. Поставленная цель достигается тем что в устройство введены дополнитель ный триггер и два элемента И, причем первые входы элементов И подключены соответственно к прямому и инверсном выходам знакового разряда регистра делителя, вторые входы элементов И подключены соответственно к прямому, и инверсному выходам дополнительного триггера, нулевой вход которого подключен к выходу переноса из нулевого разряда сумматора, а единичный вход дополнительного триггера соединен с управляющим входом устройства, выходы элементов И объединены и подключе ны ко входу младшего разряда регистр частного, прямой и инверсный выходы крторого подключены соответственно к управляющим входам узлов передами делителя прямым и инверсным кодом, информационные входы которых подключены соответственно к прямым и инверсным выходам регистра делителя, объединенные выходы узлов передачи делителя прямым и инверсным кодом подключены ко входам разрядов сумматора первой группы, входы разрядов сумматора второй группы соединены с разрядными-выходами регистра делимого, разрядные входы которого подключены к выходным разрядам сумматора. На чертеже дана схема устройства. Устройство содержит регистра делителя 1, регистр делимого (остатка) 2, сумматор 3,. регистр частного , дополнительный триггер 5, элементы И 6 и 7 и узлы 8 и 9 передачи делите ля для передачи делителя дополнитель ным либо прямым кодом на первый вход сумматора. На чертеже условно показаны схемы передачи для одного разряда. Устройство работает следующим образом. В исходном состоянии делитель в дополнительном коде со знаком записывается в регистре 1, делимое (ос234таток) - регистре 2. Частное со знаком образуется при сдвигах влево в регистре . Знаки делимого, делителя и частного находятся перед старшим значащим разрядом числа и занимают один разряд. Дополнительный триггер 5 в начале каждого шага сложения кода делителя с кодом очередного остатка устанавливается в единичное состояние. В конце сложения, если возникает перенос из нулевого разряда сумматора, содержимое дополнительного триггера инвертируется, фиксируя знак очередного остатка. Деление двоичных чисел с фиксированной перед старшим разрядом запятой возможно только в том случае, если делимое по модулю меньше делителя. В противном случае частное превышает единицу и происходит переполнение разрядной сетки. Поэтому перед началом операции деления осуществляется проверка на корректность деления. Если знаки делимого и делителя совпадают, то при посылке делителя в сумматор от его исходного кода берется дополнение, которое и суммируется с кодом делимого. В противном случае делитель суммируется в том коде, в котором он поступил на деление. После получения первого остатка, если знак делимого совпадает с состоянием дополнительного триггера 5, в котором фиксируется знак остатка, то деление не производится. Такой случай классифицируется как некорректность деления. . Если знаки делимого и дополнительного триггера 5 разные, то деление возможно. После этого начинается многошаговый процесс определения цифр частного по известному алгоритму, который слагается из последовательности циклически повторяющихся операций сдвига образующихся остатков, частного и нахождение разности между остатком и делителем. Одновременно при сдви.ге влево, в младшем разряде регистра частного Ц формируются разряды частного по следующему правилу. Если знак делителя и состояние дополнительного триггера 5 совпадают, что формируют элементы И 6 и 7, то соответствующий шагу деления разряд частного равен единице, в противном случае - О.

Характером передачи кода делителя на сумматор 3 управляет младший разряд регистра частного t, который сформировался на предыдущем шаге сдвига, по следующему правилу.

Если в младшем разряде регистра частного k записан О, то делитель через узел передачи 9 суммируется к остатку в том коде, в котором он поступил на деление. В противном случае при посылке делителя через узел передачи 8 от его исходного кода берется дополнение, которое и суммируется с кодом остатка.

1г f , .

Такое конструктивное выполнение устройства позволяет иметь один знаковый разряд в регистрах делимого, дделителя и сумматора, что снижает ап паратурные габариты, а также упрощает структуру устройства.

Формула изобретения

Устройство для деления двоичных чисел, содержащее регистр делителя, регистр делимого сумматора, регистр частного, выходы разрядов регистра делителя соединены с информационными входами узлов передачи делителя прямым н инверсным коД9М выходы которых объединены и подключены ко входам разрядов сумматора первой группы, а управляющие входы соединены соответственно с прямым и инверсным выхода ми младшего разряда регистра частного, входы разрядов сумматора второй

группы соединены с разрядными выходами регистра делимого, разрядные входы которого подключены к выходам раз рядов сумматора, .отличающееся тем, что, с целью упрощения

устройства, в него введены триггер и два элемента И, причем первые входы элементов И подключены соответственно к прямому и инверсному выходам знакового разряда регистра делителя, втЬрые входы элементов И соединены соответственно с прямым и инверсным выходами триггера,.нулевой вход которо го соединен с выходом переноса из ну левого разряда сумматора, а единич

ный вход триггера соединен с управляющим входом устройства, а выходы элементов И объединены и подключены ко входу младшего разряда регистра частного.

Источники информации, принятые во внимание при Экспертизе 1. Дроздов Е.А., Комарницкий В.А. Пятибратов А.П., Электронные вычислит тельные машины единой системы. М., Машиностроение, 1976, с. 100-102. 2. Авторское свидетельство СССР №330 51, кл. G Об F 7/39, 1972 (npof

гТрТИп) .

И t

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления чисел | 1981 |

|

SU1119006A1 |

| ДЕЛИТЕЛЬ НА НЕЙРОНАХ | 2003 |

|

RU2249846C1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Делительное устройство | 1983 |

|

SU1198512A1 |

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления двоичных чисел | 1980 |

|

SU1048472A1 |

| Устройство для деления чисел | 1980 |

|

SU907544A1 |

| ПОСЛЕДОВАТЕЛЬНЫЙ ДЕЛИТЕЛЬ ТРОИЧНЫХ ЦЕЛЫХ ЧИСЕЛ | 2023 |

|

RU2810609C1 |

| Устройство для деления чисел | 1979 |

|

SU911518A1 |

| Устройство для деления чисел | 1981 |

|

SU1056183A1 |

Авторы

Даты

1982-01-15—Публикация

1980-04-11—Подача