коммутатора 9-11, три регистра 6-8 порядков, сумматор 12 порядков, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 4, коммутатор 5 знака, три регистра 1-3 знака, первый и второй коммутаторы 17-18 мантисс j два коммутатора 23 и 24 полусумм, два коммутатора 27 и 28 переносов, вспомогательный коммутатор 30, первый и второй регистры 13 и 15 мантисс, два регистра 21 и 22 полусумм, два регистра 25 и 26 переносов, вспомогательный регистр 29, коммутатор 40 сдвигаемой информаци - сдви- гатель 36, блок 37 умнолсения, узел 45 нормализации, регистр 46 нормализации, счетчик 52 полутактов, сум1

Изобретение относится к вычислительной технике и может быть использовано в составе мультипроцессора быстродействующих ЭВМ,

Целью изобретения является повы™ шение быстродействия,

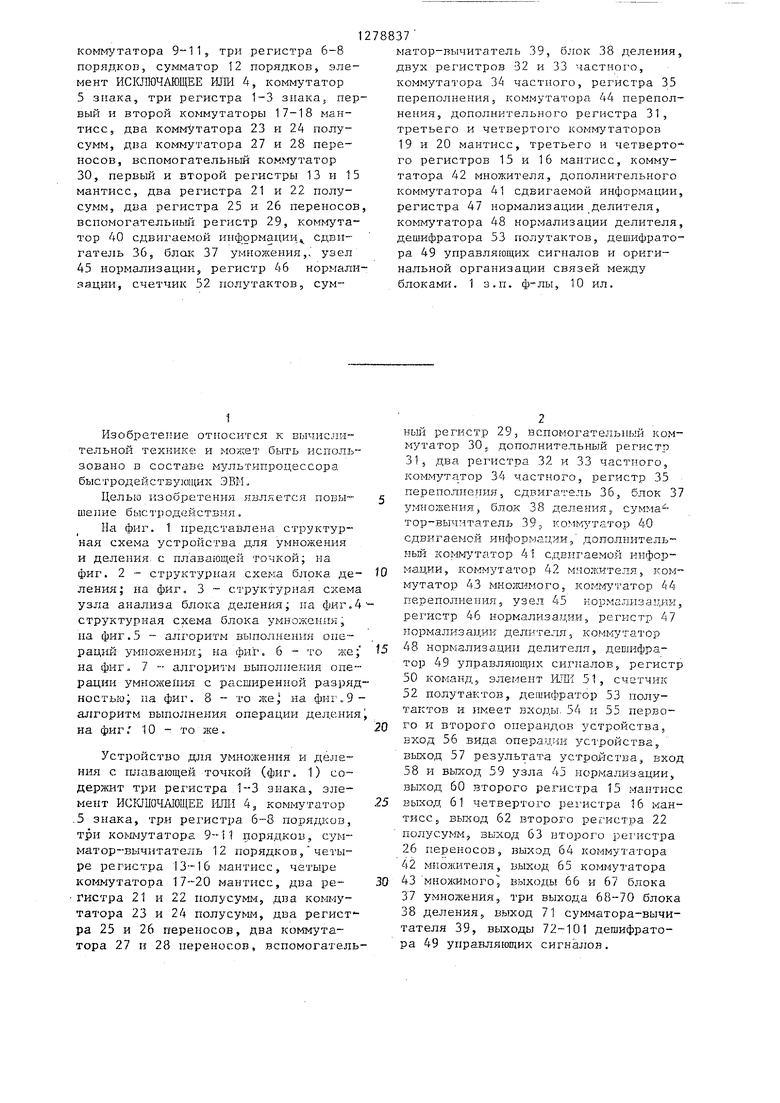

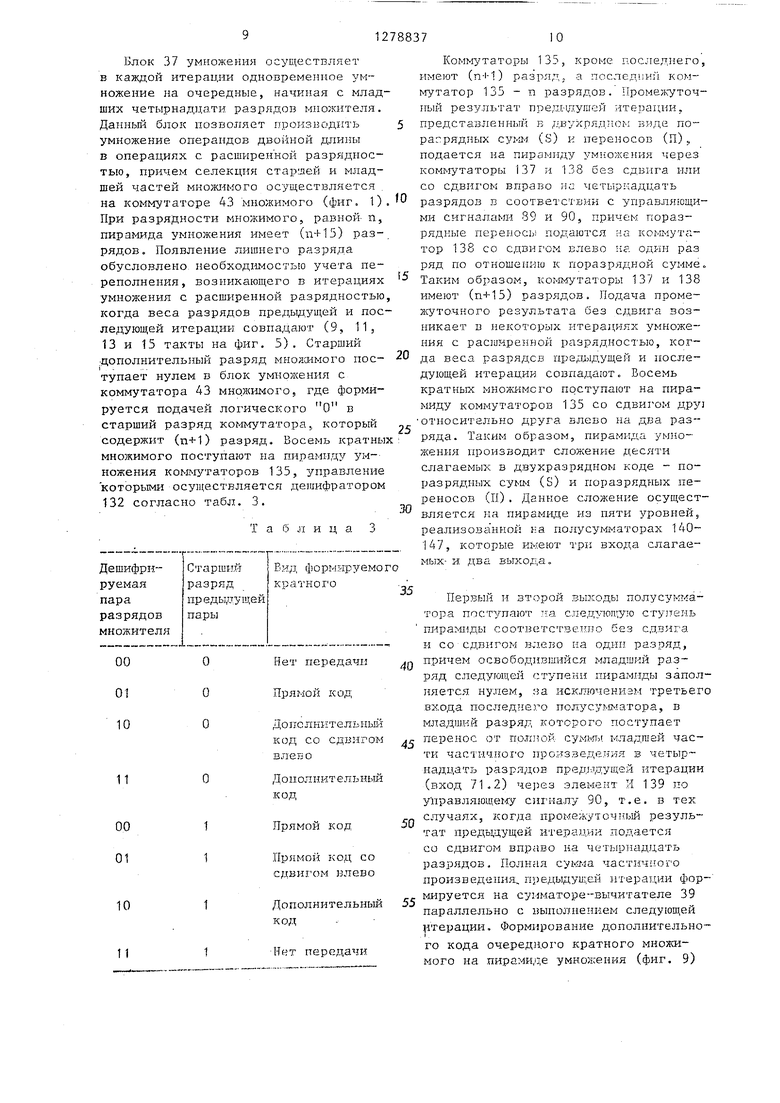

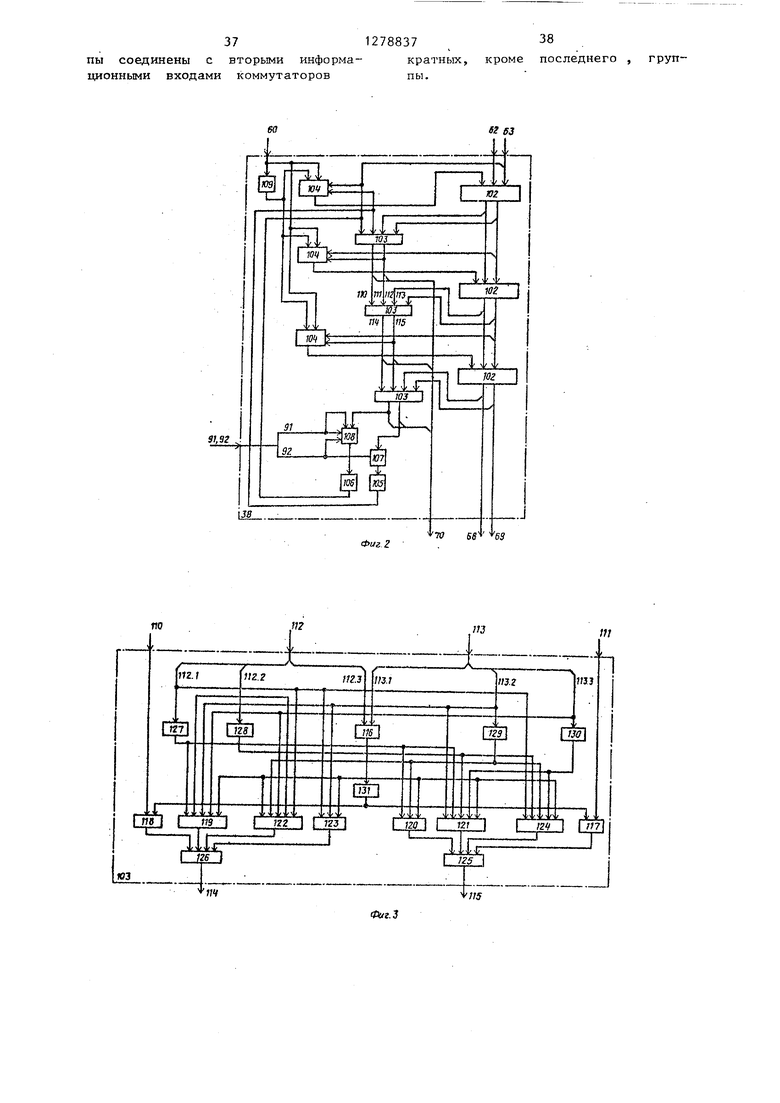

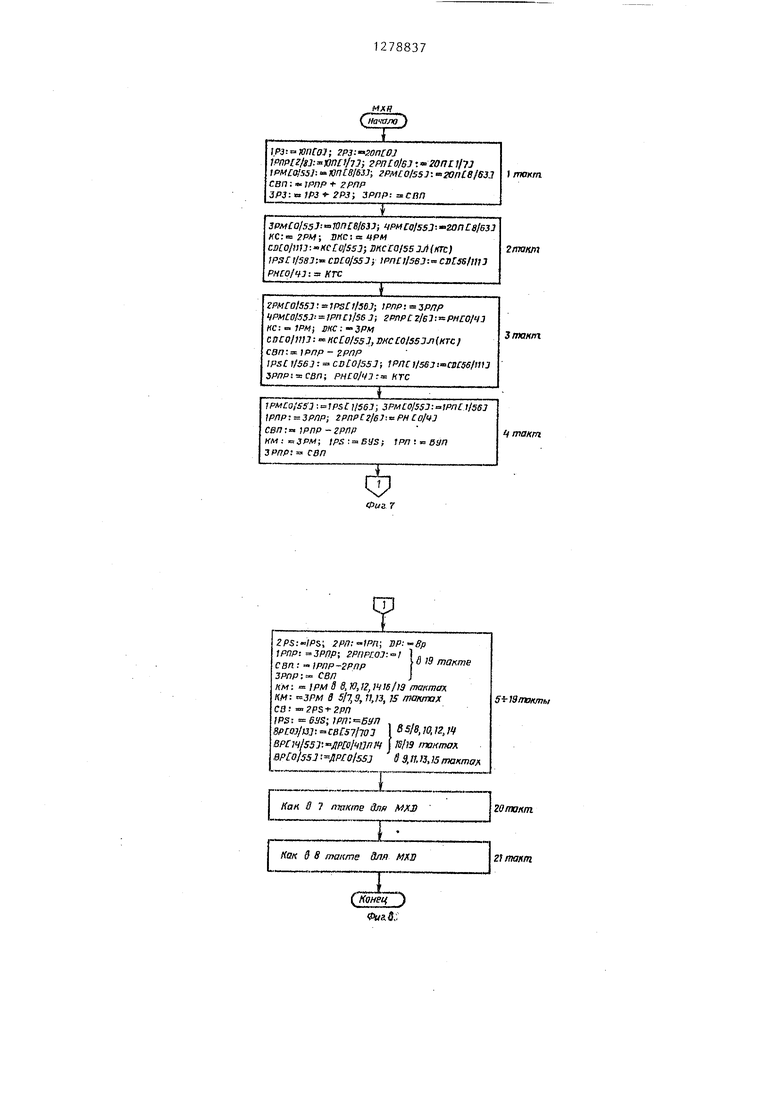

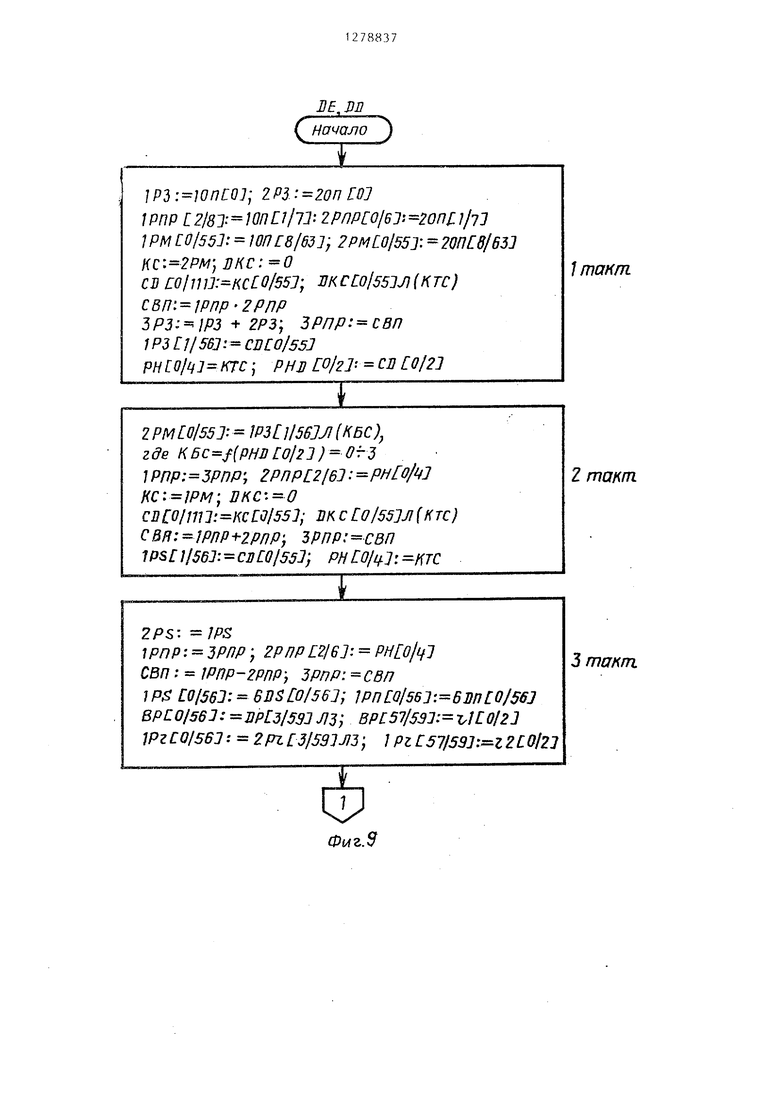

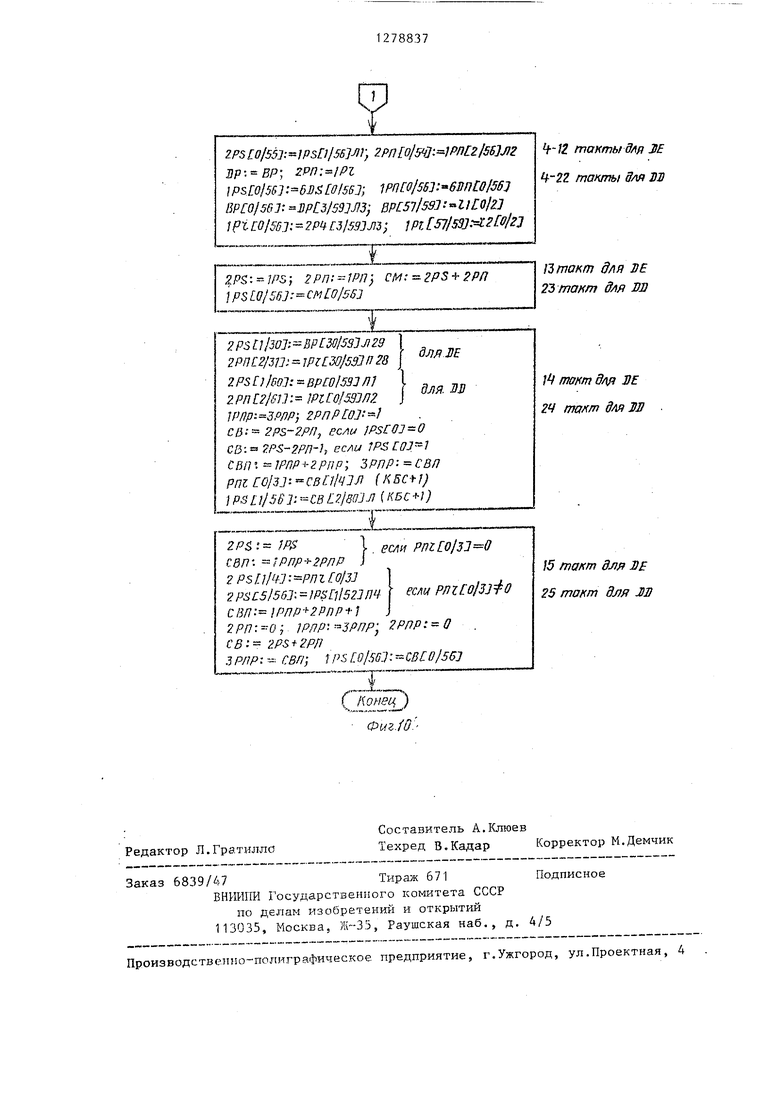

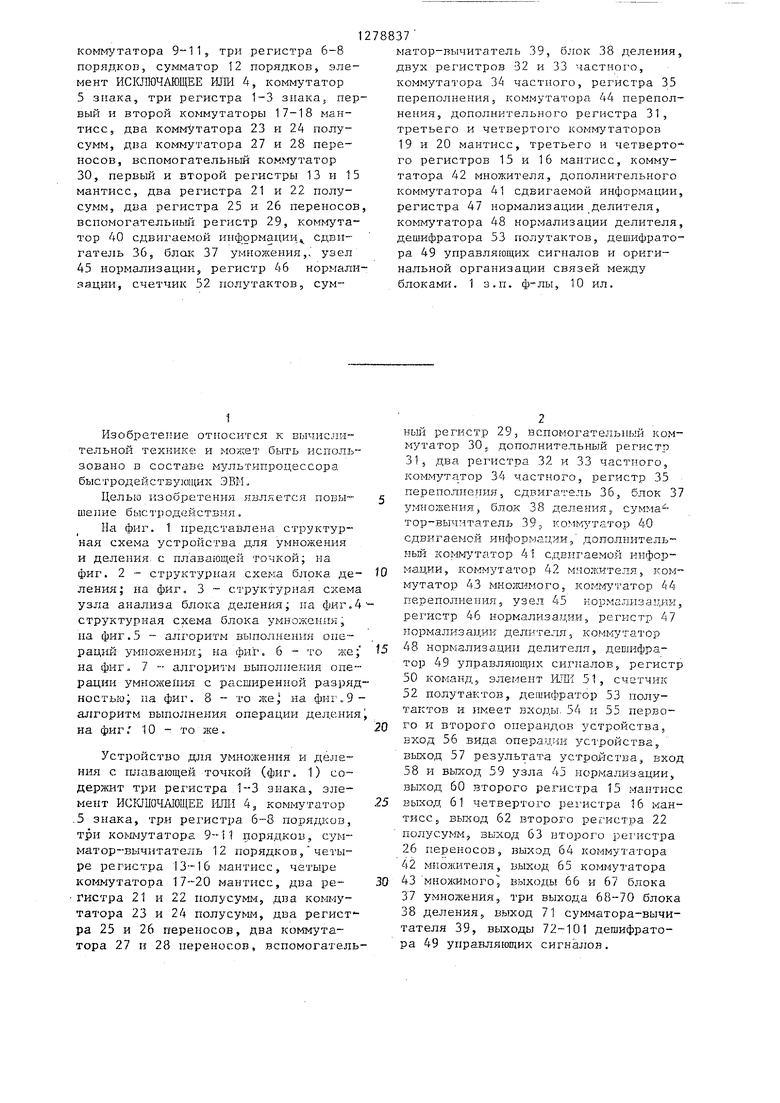

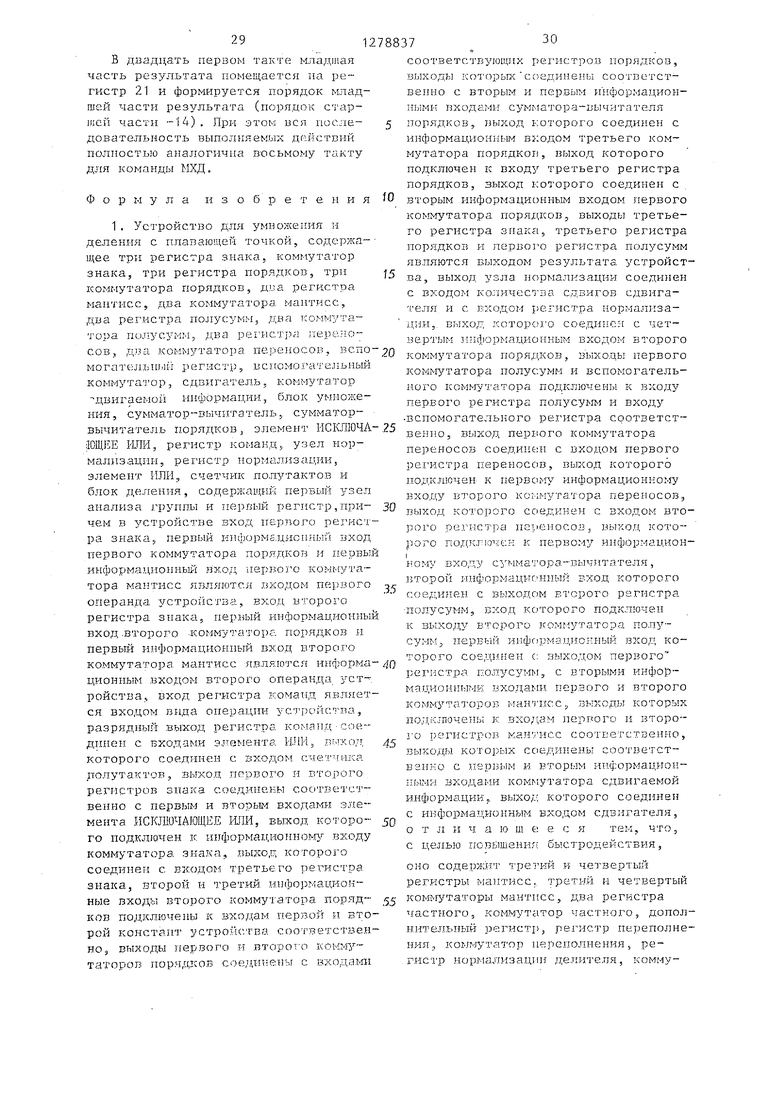

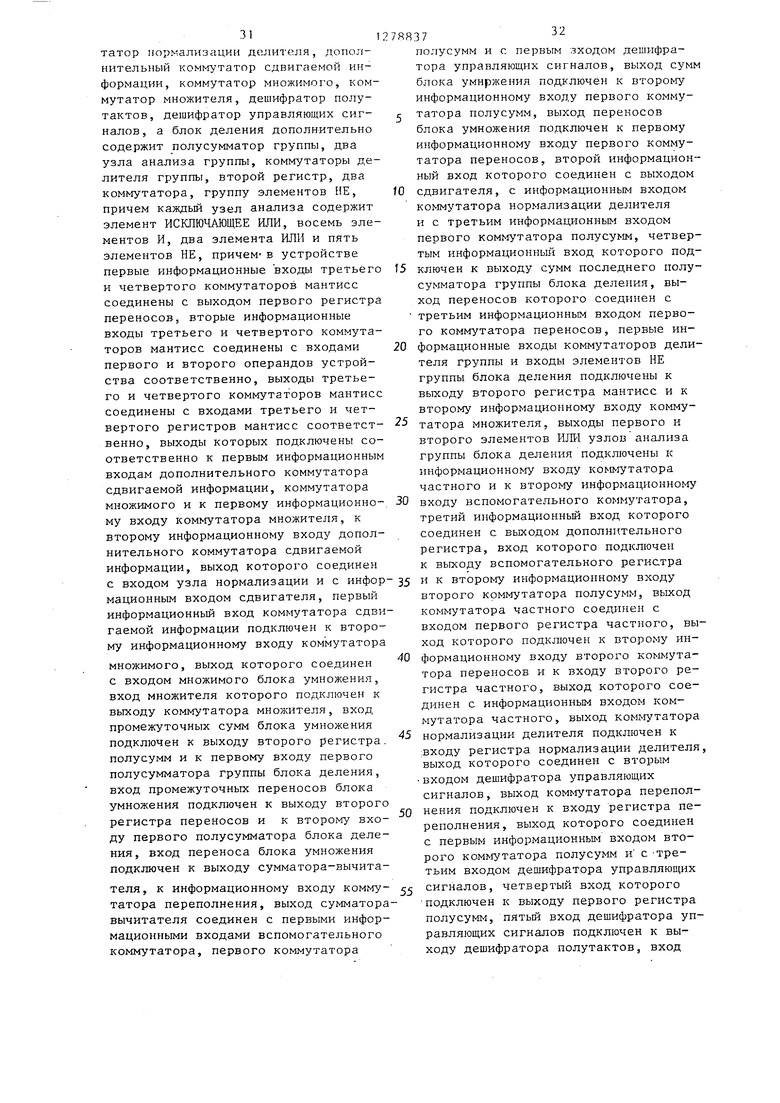

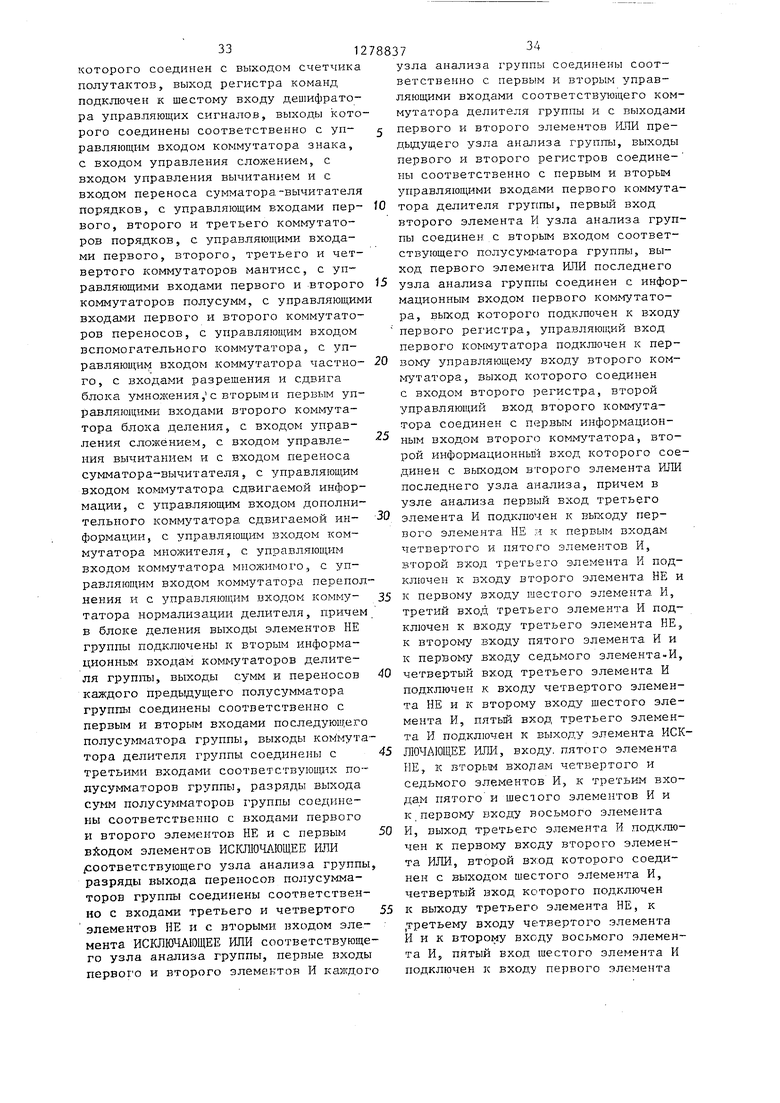

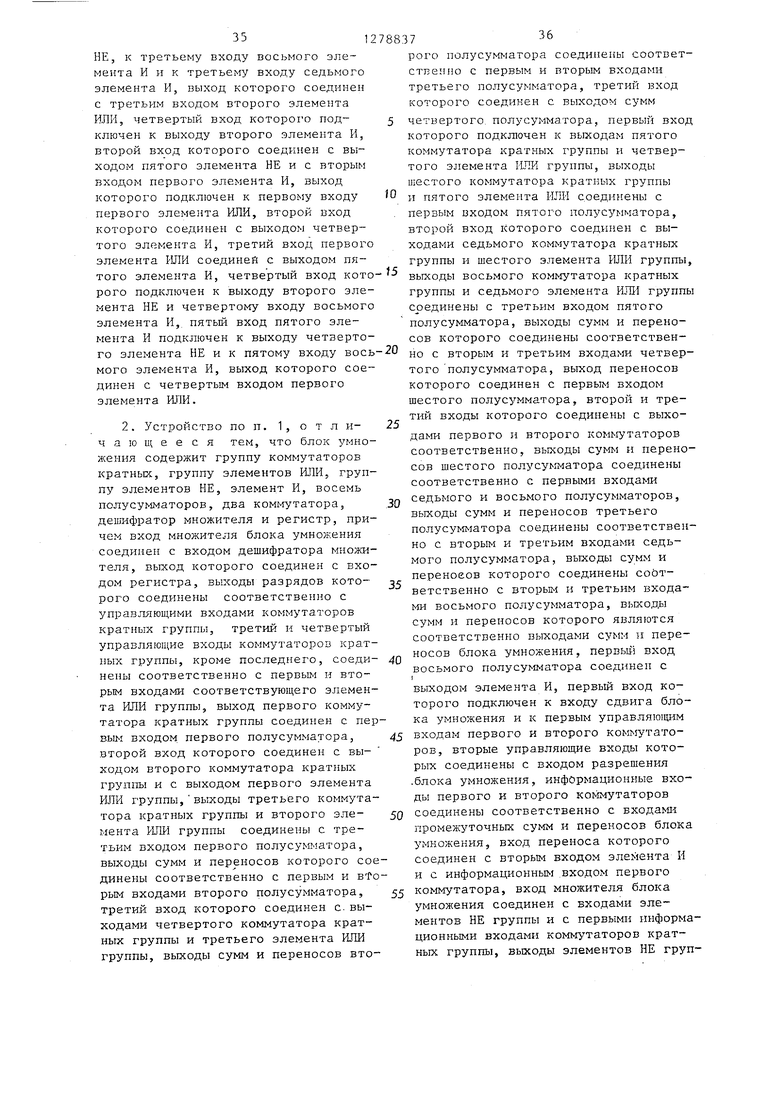

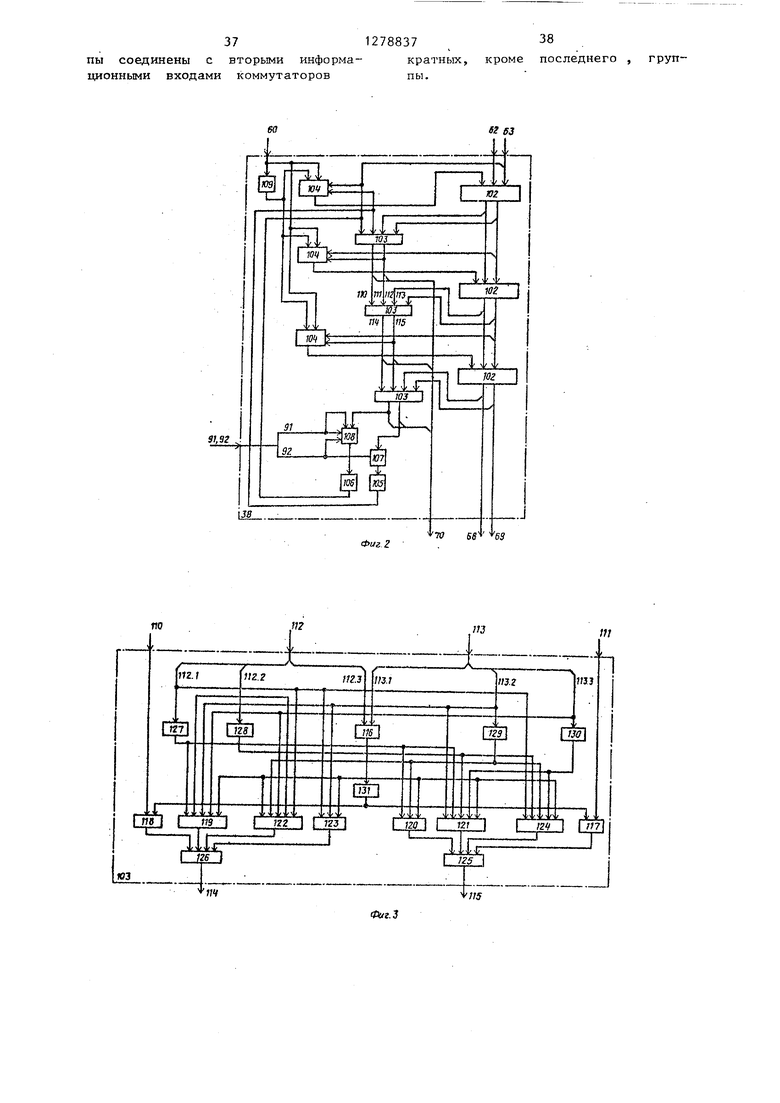

На фиг. 1 представлена структурная схема устройства для умножения и деления, с плавающей точкой; на фиг. 2 - структурная схема блока де- ления; на фиг. 3 структурная схема узла анализа блока деления; на фиг,4 структурная схема блока умножения, на фиг.5 - алгоритм выполнения операций умножения; на фиг. 6 то на фиг 7 - алгори1 м выполнения операции умножения с расширенной разрядностью; па фиг. 8 - то лее на фиг, 9- алгоритм выполнения операции деления на фиг. 10 - то же.

Устройство для умножения и деления с плавающей точкой (фиг. 1) со- дерлшт три регистра 1--3 знака, элемент ИСЮШЧАЮЩЕЕ 11ПИ 4, коммутатор .5 знака, три регистра 6-8 порядков, три коммутатора 9-11 порядков, сум- матор-вычитатель 12 порядков, четыре регистра 13-16 мантисс, четыре коммутатора 17-20 мантисс, два ре гистра 21 и 22 полусумм, два коммутатора 23 и 24 полусумм, два регистра 25 и 26 переносов, два тора 27 и 28 переносов, вспомогательматор-вычитатель 39, блок 38 деления, двух регистров 32 и 33 частнох-о, коммутатора 34 частного, регистра 35 переполнения 5 коммутатора 44 переполнения, дополнительного регистра 31, третьего и четвертого коммутаторов 19 и 20 мантисс, третьего и четверто- го регистров 15 и 16 мантисс, коммутатора 42 множителя, дополнительного коммутатора 41 сдвигаемой информации, регистра 47 нормализации делителя, коммутатора 48 нормализации делителя, дешифратора 53 полутактов, деп1ифрато- ра 49 управляющих сигналов и оригинальной организации связей блоками. 1 з.п. ф-лы, 10 ил.

ньш регистр 29, вспомогательный коммутатор 30., дополнительный регистр 31, два регистра 32 и 33 частного, коммутатор 34 частного, регистр 35 переполнения, сдвигатель 36, блок 37 ум юлсения, блок 38 деления, сумма- тор-вычитатель 39, комм утатор 40 сдвигаемой информации, дополнительный ком1-г/татор 41 сдвигаемой информации, коммутатор 42 множителя, коммутатор 43 мнола- мого, когфтутатор 44 переполнегзия, узел 45 нормализа1;,ии, регистр 46 нормализатдии, регистр 47 нормализации делителя, комм7х татор 48 нормализации делителя, деЕ ифра- тор 49 управляющих сигналов, регистр 50 команд, элемент ИЛК 51, счетчик 52 полутактов, дешифратор 53 полутактов и имеет входы. 54 и 55 первого и второго операндов устройства, вход 56 вида операции устройства, выход 57 результата устройства, вход 58 и вькод 59 узла 45 нормализации, выход 60 второго регистра 15 мантисс выход 61 четвертого рех истра 16 мантисс, выхо/д 62 второго регистра 22 пoлycy м, выход 63 второго регистра 26 переносов, выход 64 коммутатора

42миолштеля, выход 65 коммутатора

43мноасимого выходы 66 и 67 блока

37умножения, три выхода 68-70 блока

38деления, выход 71 сумматора-вычи- тателя 39, выходы 72-101 дешифратора 49 управляющих сигналов.

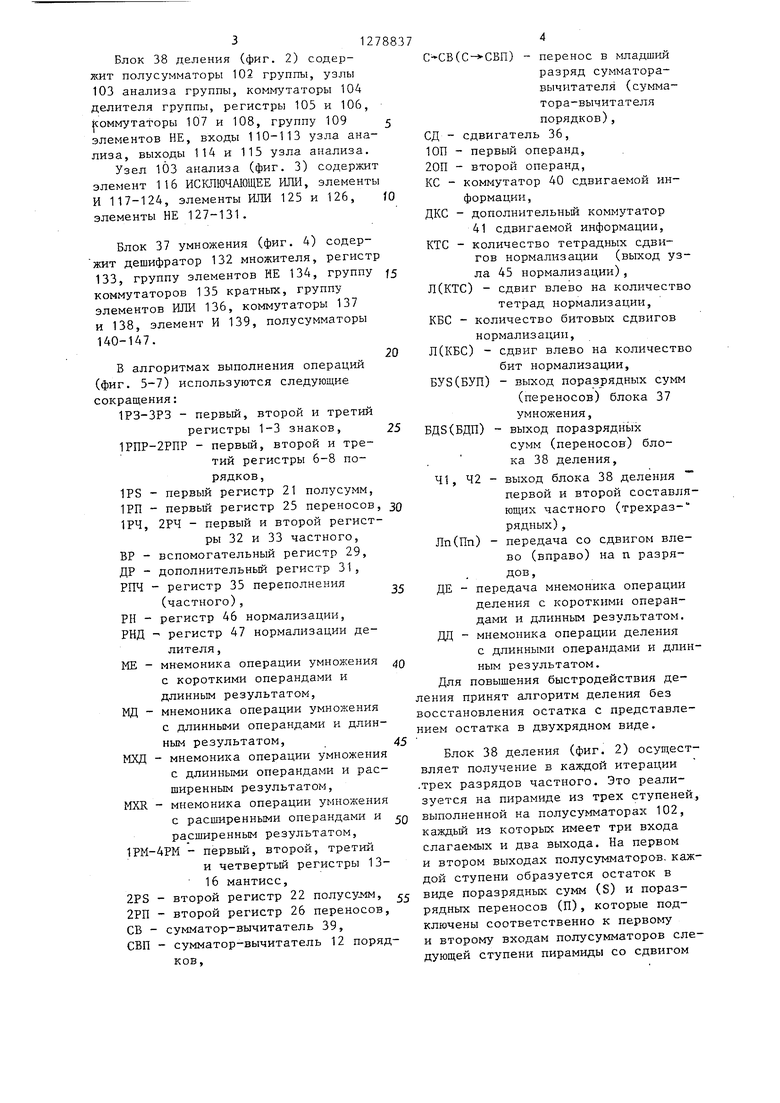

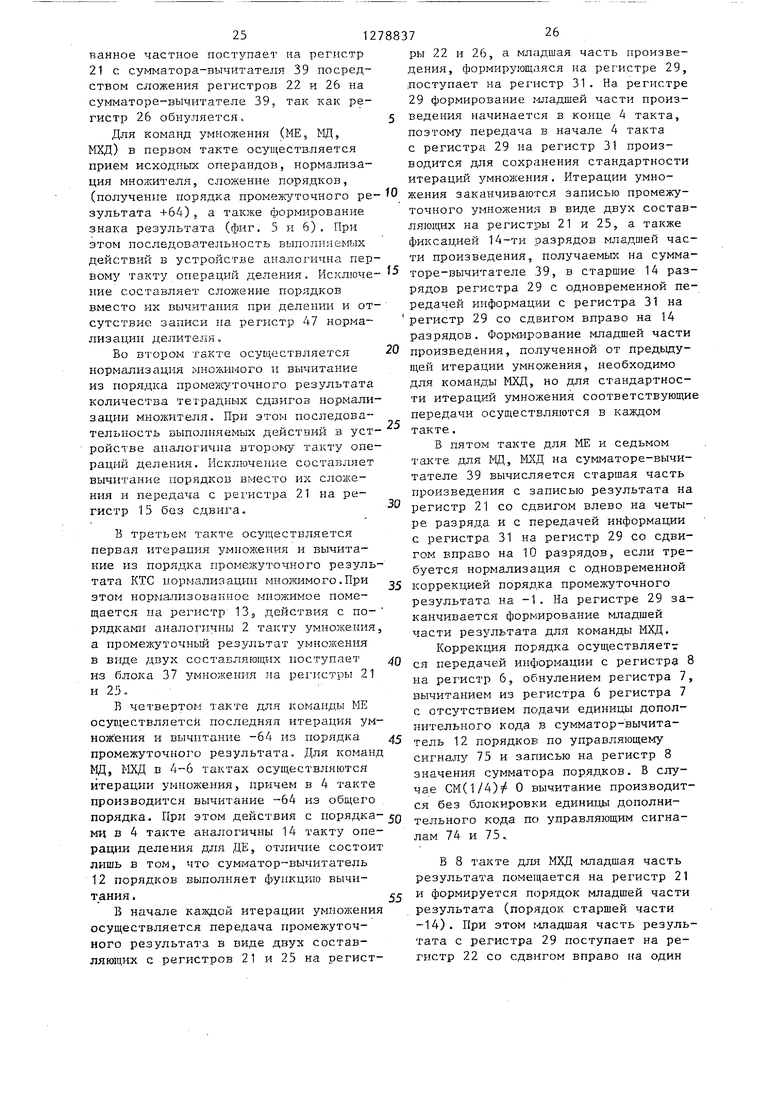

Блок 38 деления (фиг. 2) содержит полусумматоры 102 группы, узлы 103 анализа группы, коммутаторы 104 делителя группы, регистры 105 и 106, | :оммутаторы 107 и 108, группу 109 элементов НЕ, входы 110-113 узла анализа, выходы 114 и 115 узла анализа.

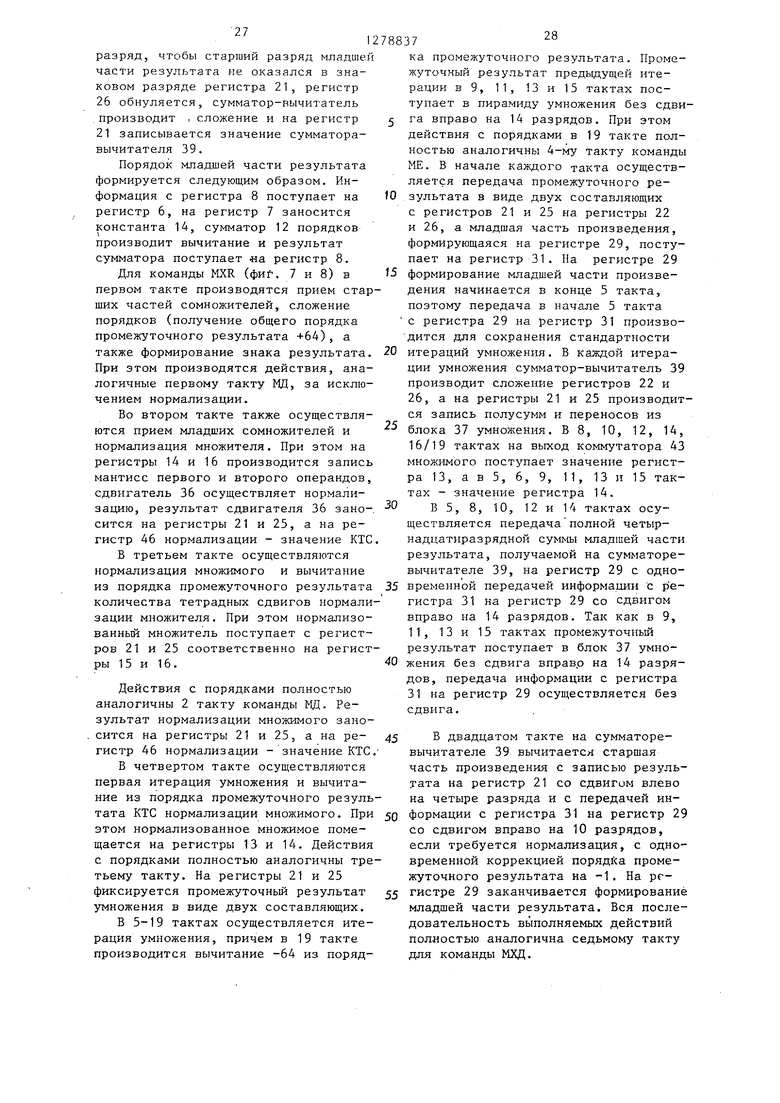

Узел 103 анализа (фиг. 3) содержит элемент 116 ИСКЛЮЧАЮЩЕЕ ИЛИ, элементы И 117-124, элементы ИЛИ 125 и 126, элементы НЕ 127-131.

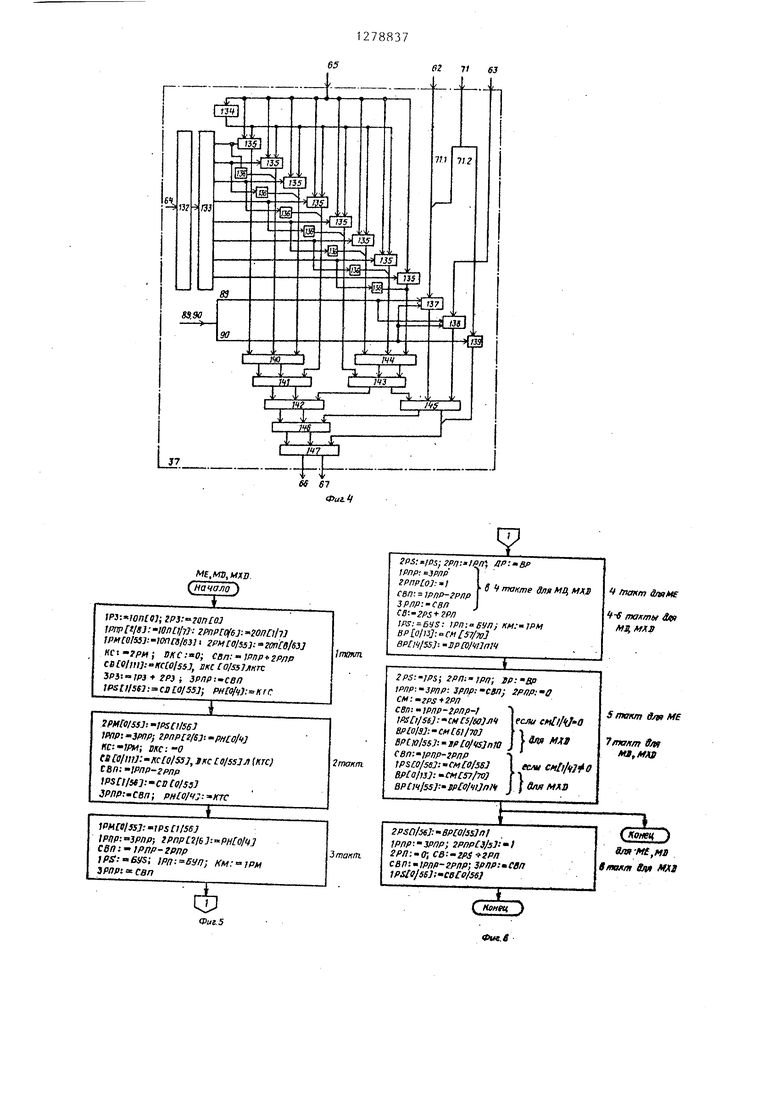

Блок 37 умножения (фиг. 4) содер- жит дешифратор 132 множителя, регистр 133, группу элементов НЕ 134, группу коммутаторов 135 кратных, группу элементов ИЛИ 136, коммутаторы 137 и 138, элемент И 139, полусумматоры 140-147.

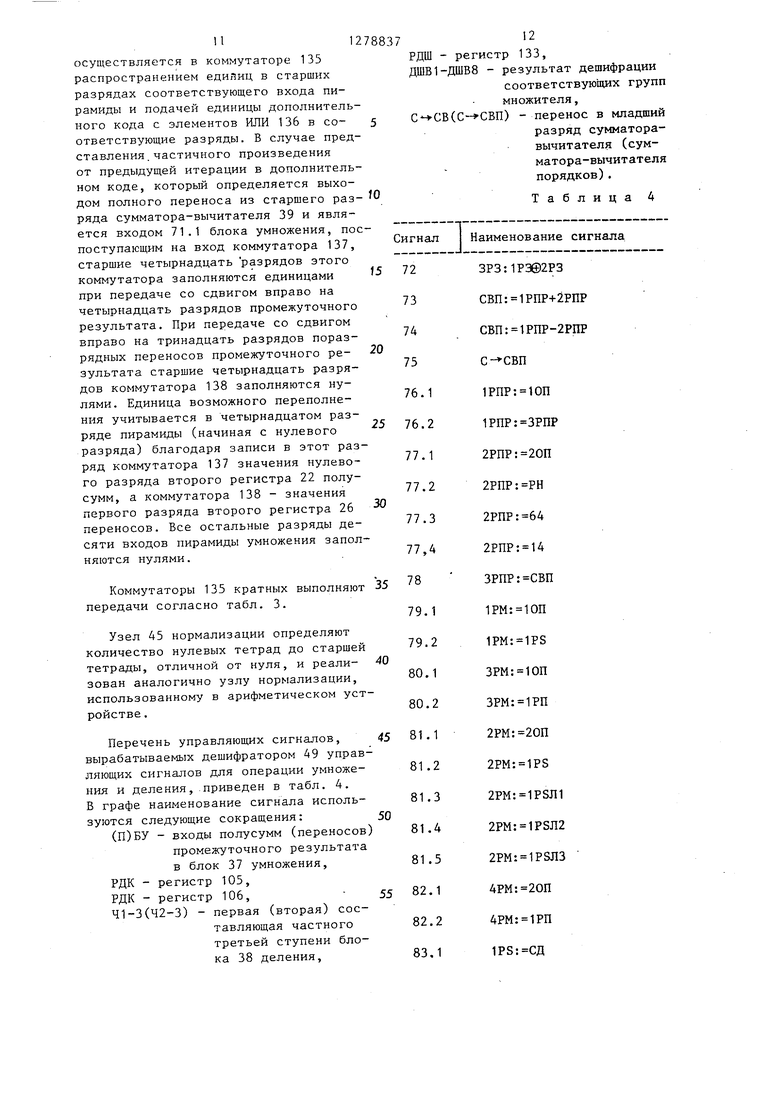

в алгоритмах выполнения операций фиг. 5-7) используются следующие окращения:

1РЗ-ЗРЗ - первый, второй и третий

регистры 1-3 знаков, 1РПР-2РПР - первый, второй и третий регистры 6-8 порядков,

IPS - первый регистр 21 полусумм, 1РП - первый регистр 25 переносов, 1РЧ, 2РЧ - первый и второй регистры 32 и 33 частного, ВР - вспомогательный регистр 29, ДР - дополнительный регистр 31, РГГЧ - регистр 35 переполнения

(частного), РН - регистр 46 нормализации, РИД - регистр 47 нормализации делителя ,

ME - мнемоника операции умножения с короткими операндами и длинным результатом, МД - мнемоника операции умножения с длинными операндами и длинным результатом, МХД - мнемоника операции умножения с длинными операндами и расширенным результатом, MXR - мнемоника операции умножения с расширенными операндами и расширенным результатом, 1РМ-4РМ - первый, второй, третий

и четвертьй регистры 13- 16 мантисс,

2PS - второй регистр 22 полусу-мм, 2РП - второй регистр 26 переносов, СВ - сумматор-вычитатель 39, СВП - сумматор-вычитатель 12 порядков ,

5

O

5

() 0

5

0

5

0

5

0

5

перенос в младший разряд сумматора- вычитателя (сумма- тора-вычитателя порядков), СД - сдвигатель 36, 10П - первый операнд, 20П - второй операнд, КС - коммутатор 40 сдвигаемой информации,

ДКС - дополнительньй коммутатор 41 сдвигаемой информации, КТО - количество тетрадных сдвигов нормализации (выход узла 45 нормализации), Л(КТС) - сдвиг влево на количество

тетрад нормализации, КБС - количество битовых сдвигов

нормализации, Л(КБС) - сдвиг влево на количество

бит нормализации,

БУЗ(БУП) - выход поразрядных сумм (переносов) блока 37 умножения, БД8(БДП) - выход поразрядных

сумм (переносов) блока 38 деления,

41, 42 - выход блока 38 деления первой и второй составляющих частного (трехраз- рядных),

Лп(Пп) - передача со сдвигом влево (вправо) на п разрядов ,

ДЕ - передача мнемоника операции деления с короткими операндами и длинньм результатом. ДД - мнемоника операции деления

с длинными операндами и длинным результатом.

Для повышения быстродействия деления принят алгоритм деления без восстановления остатка с представлением остатка в двухрядном виде.

Блок 38 деления (фиг. 2) осуществляет получение в каждой итерации .трех разрядов частного. Это реализуется на пирамиде из трех ступеней, выполненной на полусумматорах 102, каждьй из которых имеет три входа слагаемых и два выхода. На первом и втором выходах полусумматоров, каждой ступени образуется остаток в виде поразрядных сумм (S) и поразрядных переносов (П), которые подключены соответственно к первому и второму входам полусумматоров следующей ступени пирамиды со сдвигом

влево на один разряд (S) и со сдвигом влево на два разряда (П). На третий вход полусумматора поступает целитель 60 в прямом или обратном коде. Определение вида передачи делителя на вход полусумматора и получение очередной цифры частного в виде двух составляющих на каждой ступени пирамиды осуществляется на узле 103 анализа, на которьш поступают три старших разряда остатка в двух- рядном виде и два выхода предыдущего узла анализа. Два выхода узла ана- . лиза, представляюд1ие очередной разряд частного в виде двух составляющих, используются для определения вида передачи делителя на очередную ступень полусумматора.

Дополнительньй код делителя образуется подачей единицы в освободившийся младший разряд третьего входа полусумматора, на который подается поразрядный перенос остатка со сдвигом влево на два разряда. Вид передачи делителя, полученньш иа третьем узле анализа, запоминается по управляющему сигналу 92 на регистрах 105 и 106.

В первой итерации деления делител поступает на третий вход первой ступени пирамиды в обратном коде, что осуществляется записью единицы на регистр 106 по управляюще1 1у сигналу 91. При этом на первый вход первой ступени пирамиды поступает делимое, на второй вход - нули, за исключением-младшего разряда, куда поступает единица дополнительного кода делителя с регистром 106. Формирование делителя в нужном коде ступени на калздо ступени пираш1ды осуществляется на элементах НЕ 109 и коммутаторах 104, управляющими входами которых являются выходы узлов анализ а предыдущей ступени.

Определение цифры частного, имея остаток, который записан в двухразрядном коде, производится с использованием избыточных цифр частного, Г. е. для каждого частного допусти- мы{4и считаются три возможные цифры: ,+1, О, -1, При условии, что делитель (d) должен быть нормализованным числом, для анализа вида передачи делителя и определения цифры частного достаточно анализировать в приведенном виде четыре старших цифры остатка, включая два знаковых

разряда. При зтом комбинации вида 01.XX (значения X - О или .1) исключаются, так как не может быть переполнения. Комбинация 10 в знаковых разрядах может получиться, если в четьфех старших разрядах - комбинация 10.11 и присутствует перенос из неприведенной части, в результате чего комбинация 10.11 сводится к комбинации 11.00. Вид передачи делителя и цифра частного., соответствующие определенной комбинации старших разрядов, приведены в табл. 1.

Таблица 1

При комбинации 11.11 знак оста.тка неизвестен. Он зависит от переноса не из неприведенной части. При полном приведении остатка в этих разрядах может быть две комбинации: 00,00 (поожительный остаток) или 11.11 (отрицательный , остаток) . В обоих случаях остаток по абсолютной величине не превышает делитель. При этом последующий остаток - это настоящий, сдвину-

тый влево на один разряд, а цифра частного равна нулю.

Если для определения цифры частного используется значение предыдущей цифры частного (предьщущей передачи делителя), можно количество знаковых разрядов сократить до одного младшего разряда в приведенном виде (с приведением переноса), а два

12788378

других разряда могут быть представ- соответствующие определенной комби- лены в двухрядном коде. Вид переда- нации при анализе трех старших раз- чи делителя и цифра с частного, рядов остатка, представлены в табл.2,

Таблица2

с учетом знака (п+1) (п - количество разрядов мантиссы длинного операнда) . Дополнительный старший разряд делителя формируется подачей в старший разряд коммутаторов 104 нуля при передаче делимого в прямом коде и единицы при его передаче в обратном коде. Дополнительный старший разряд делимого образуется в старшем разряде на первом регистре 21 полусумм подачей нуля на коммутатор 23 при записи результата нормализации делимого со сдвигателя-36 В дальнейшем знак делимого через второй регистр 22 полусуммы поступает в блок деления в старший разряд первого входа первой ступени

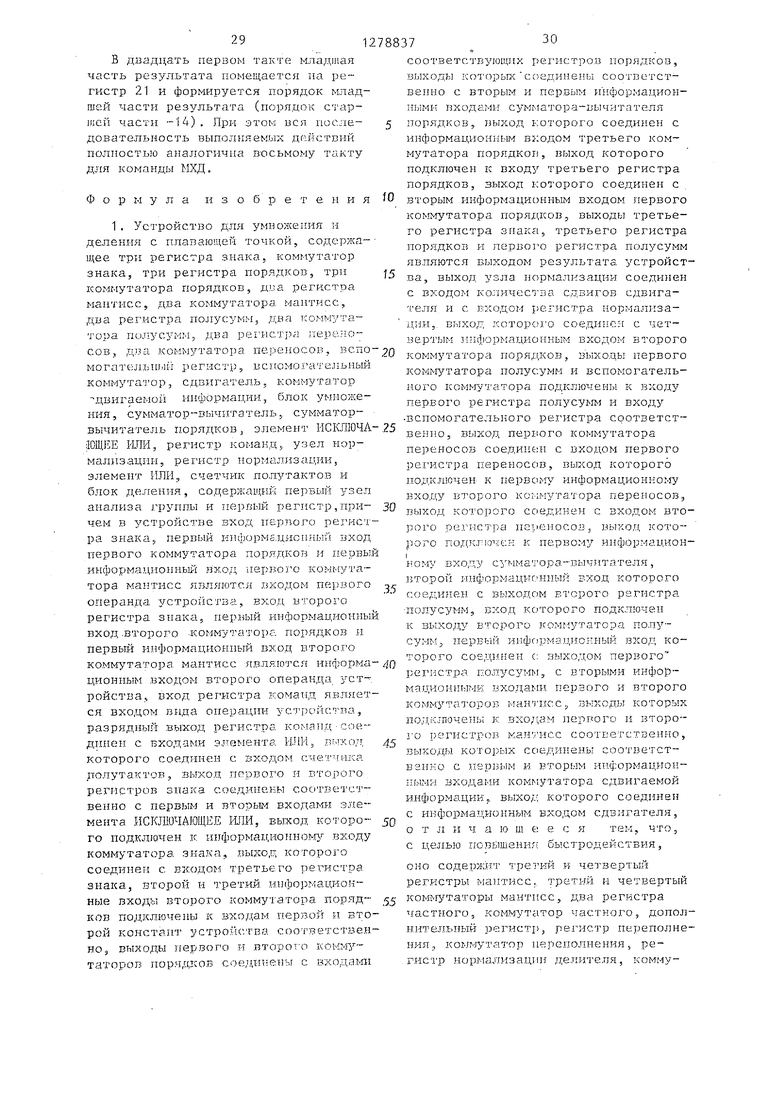

В блоке 37 умножения (фиг. 4) осуществляется анализ очередных четырнадцати разрядов множителя, разбитых на пары, что реализуется дешифратором 132, вырабатьшающим группу управляющих сигналов, фиксируемых на регистре 133 в конце такта. Выход этого регистра подключен к управляющим входам коммутаторов 135 блока 37 умножения. Дешифрация каждой пары разрядов множителя производится в соответствии с табл. 3. Селекция очередных четырнадцати разрядов множителя осуществляется за такт до итерации умножения на эти разряды и реализуется коммутатором 42 множителя.

Блок 37 умножения осуЕ1;ествляет в казкдой итерации одновременное умножение иа очередные, начиная с младших четырнадцати разрядов множителя. Данньш блок позволяет производить умножение операндов двойной длины в операциях с расширенной разрядностью, причем селекция стар:дей и младшей частей множиьюго осуществляется на коммутаторе 43 множимого (фиг, 1) При разрядности множимого, равной- п, пирамида умножения имеет (п+15) разрядов. Появление лишнего разряда обусловлено необходимостью учета переполнения, возникающего в итерациях умножения с расширенной разрядностью когда веса разрядов предыдущей и последующей итерации совпадают (9, 11, 13 и 15 такты на фиг, 5), Старший -дополнительный разряд мнолсимого поступает нулем в блок умножения с коммутатора 43 MHO.HiiMoro, где формируется подачей логического О в старший разряд коммутатора, который содержит (n-f-1) разряд. Восемь кратны множимого поступают на пирамиду умножения коммутаторов 135, управление которыми осуществляется дешифратором 132 согласно табл, 3,

Т а б л и ц а. 3

о о о

Нет передачи Прямой код

Дополнительный код со cдвигo 5 влет- о

Дополнительный код

Прямой код

Прямой код со сдвигом влево

Дополнительный код

Нет передачи

0

5

Комм; таторы 135, кроме последнего, имеют (п-1-1) разряд, а последии; ком- гyтaтop 135 - п разрядов. Промежуточный результат предыдущей итерации, представленный в двyзcpядпo.; виде поразрядных cyi-a-i (S) к переносов (П) , подается на пирамиду умножеьп-ьч через комкгутаторы 137 и 138 без сдвига или со сдвигом вправо на четырнадцать разрядов в соответствии с управляющими сигналами 89 и 90, причем поразрядные перенос) подаются на комму-та- тор 138 со сдвигом влево на один раз ряд по отнощеги 1ю к поразрядной сумме - Таким образом, коммутаторы 137 и 138 имеют (п+15) разрядов. Подача проме- лсуто-чного результата без сдвига возникает в } екоторых итерациях умножения с расширенной разрядностью, когда веса разрядов предащущей и последующей итерации совпадают, Восемь кратных множимого поступают на пирамиду коммутаторов 135 со сдвигог ДРУ1 относительно друга влево на два разряда. Таким образом, пирамида умножения производит сложение д,есяти слагаемых в двухразрядном коде - поразрядных cyf-M (S) и поразрядных переносов (п). Данное сложение осуществляется на пира.ми,це из пяти уровней, реализова нной ка полусумматорах 140- 147, которые и1чгеют три входа слагаемых- и два выхода.

0

Первый и второй выходы полусумматора поступают иа. след пощую ступень пирамиды соответствепБо без сдвига и со сдвигом влево на один разряд, причем освободившийся младший разряд следую1це11 ступени пирамиды заполняется нулем, яа исключениэм третьего входа последнего полусумматора, в младший разряд которого поступает перенос от поляой сумш младшей части частичног о произведения в четырнадцать разрядов пред1-лдущей итерации (вход 71,2) че1)ез элемент И 139 по управляющег у сигналу 90, т,е. в тех случаях, когда промежуточный результат цреды,цущей итерации подается со сдвигом вправо на четырнадцать разрядов. Полная сукма частичного произведения предыдущей итерации формируется на сумматоре-вычитателе 39 параллельно с вынолнением следуюш,ей цтерации. Формирование дополнительного кода очередного кратного множимого на пирами,а,е умножения (фиг. 9)

0

5

0

5

Ч1

осуй(ествляется в коммутаторе 135 распространением едипиц в старших разрядах соответствующего входа пирамиды и подачей единицы дополнительного кода с элементов ИЛИ 136 в со- ответствующие разряды. В случае представления, частичного произведения от предыдущей итерации в дополнительном коде, который определяется выходом полного переноса из старшего раз- ряда сумматора-вычитателя 39 и является входом 71.1 блока умножения, пос поступающим на вход коммутатора 137, старшие четырнадцать разрядов этого коммутатора заполняются единицами при передаче со сдвигом вправо на четырнадцать разрядов промежуточного результата. При передаче со сдвигом вправо на тринадцать разрядов поразрядных переносов промежуточного результата старшие четырнадцать разрядов коммутатора 138 заполняются нулями. Единица возможного переполнения учитывается в четырнадцатом разряде пирамиды (начиная с нулевого разряда) благодаря записи в этот разряд коммутатора 137 значения нулевого разряда второго регистра 22 полусумм, а коммутатора 138 - значения первого разряда второго регистра 26 переносов. Все остальные разряды десяти входов пирамиды умножения заполняются нулями.

Коммутаторы 135 кратных выполняют передачи согласно табл. 3.

Узел 45 нормализации определяют количество нулевых тетрад до старшей тетрады, отличной от нуля, и рвали- зован аналогично узлу нормализации, использованному в арифметическом устройстве.

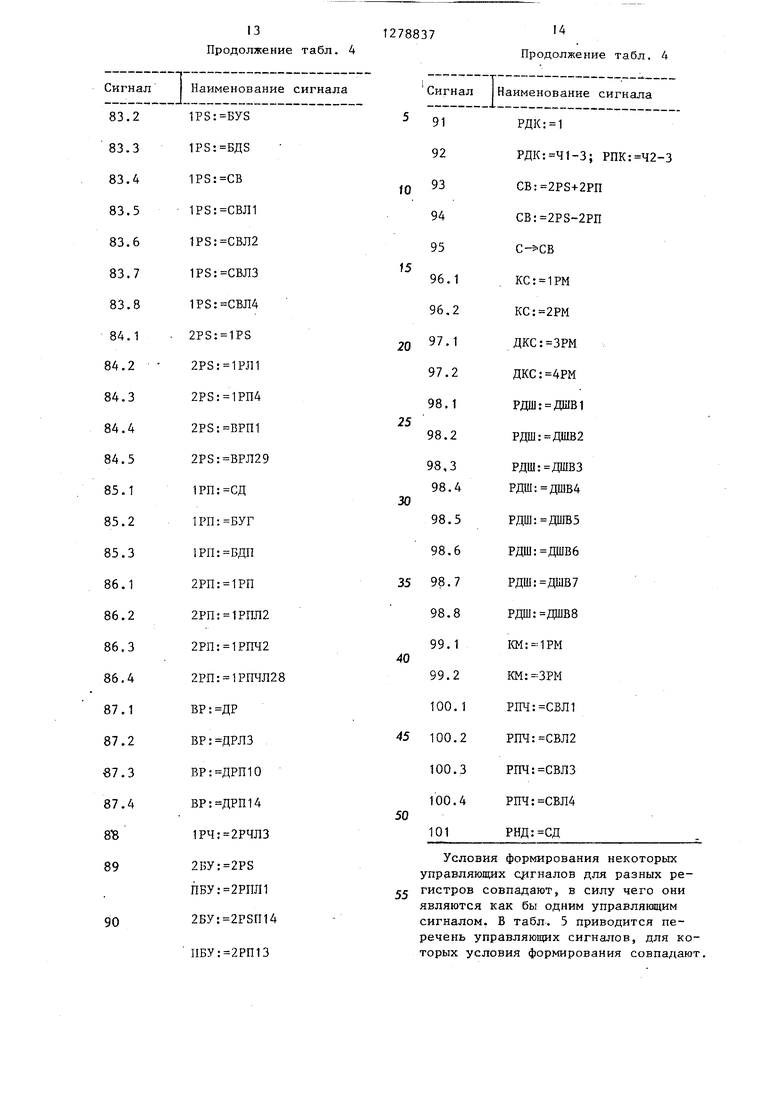

Перечень управляющих сигналов, вырабатываемых дешифратором 49 управляющих сигналов для операции умножения и деления, .приведен в табл. 4. В графе наименование сигнала используются следующие сокращения: (П)БУ - входы полусумм (переносов) промежуточного результата в блок 37 умножения, РДК - регистр 105,

РДК - регистр 106,

41-3(42-3) - первая (вторая) составляющая частного третьей ступени блока 38 деления.

12

РДШ - регистр 133, ДШВ1-ДШВ8 - результат дешифрации соответствующих групп множителя,

() - перенос в младший разряд сумматора- вычитателя (сумматора-вычитателяпорядков).

Таблица 4

13

Продолжение табл. 4

11БУ: 2РП13

1278837

14 Продолжение табл. 4

речень управляющих сигналов, для которых условия формирования совпадают.

Таблица 5

Сигнал

Назначение сигналов

76.1

Запись на регистры 6, 7, 13 и 15 значений первого И второго операндов

Запись на регистры 14 и 16 младшей части мантиссы расширенной ра зрядности

Запись на регистры 21 и 25 нормализованной мантиссы со сдвигателя

Запись на регистры 21 и 25 промежуточного результата итераций умножения

Запись на регистры 21 и 25 промежуточного результата итераций деления

Запись на регистры 22 и 26 двух составляющих частного в 24 также ДЦ для формирования полного частного Запись на регистры 22 и 26 двух составляющих частного в 24 такте ДЕ для формирова ния полного частного

Запись на регистры 29 и 32 двух составляющих частного

Запись частного на регистры 21 и 35 с учетом нормализации делителя до одного бита

Нормализованная мантисса со сдвигателя 36 на регистры 21 и 25 по

fO

15

7883716

управляющим сигналам 83.1 и 85.1 всегда записывается с учетом операции умножения с расширенной разрядностью. При других операциях на ре5 гистр 25 со сдвигателя 36 поступают нули. Управляющие сигналы 83.8 и 100.4 используются также для нормализации произведения на одну шестнадцатиричную цифру, если это необходимо, при записи на регистр 2t, а значение регистра 35 при этом не имеет значения.

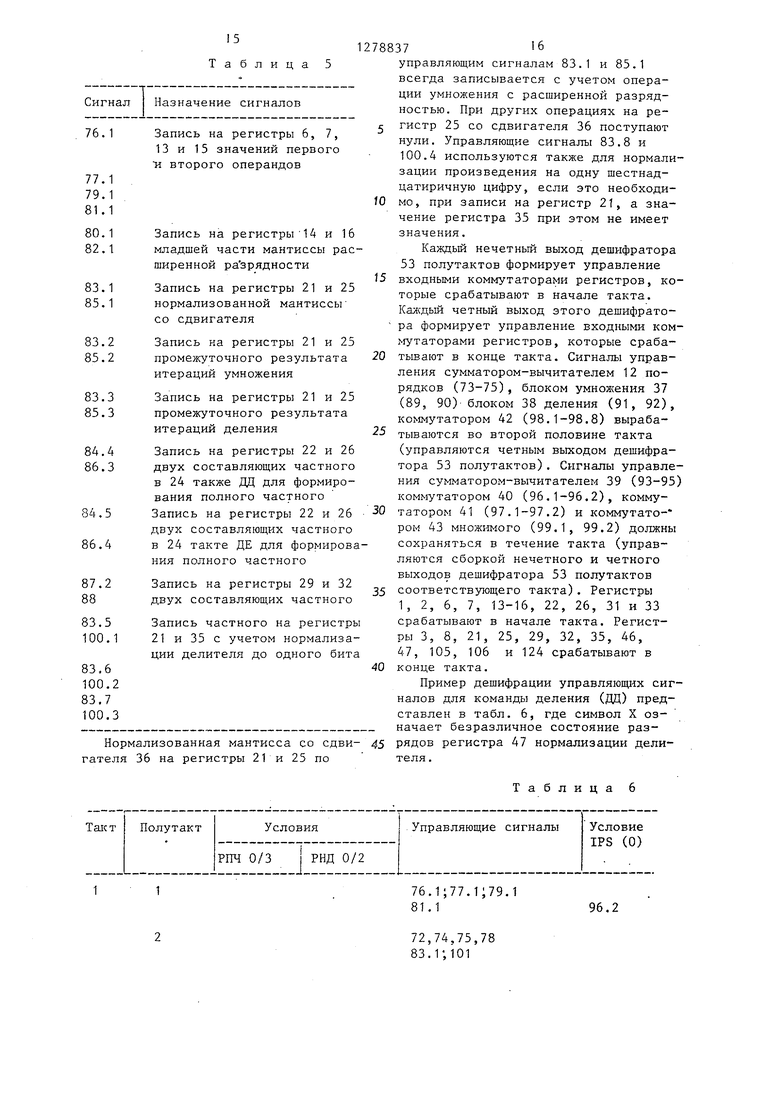

Каждый нечетный выход дешифратора 53 полутактов формирует управление входными коммутаторами регистров, которые срабатывают в начале такта. Калодый четный выход этого дешифратора формирует управление входными коммутаторами регистров, которые сраба- тьшают в конце такта. Сигналы управления сумматором-вычитателем 12 порядков (73-75), блоком умножения 37 (89, 90) блоком 38 деления (91, 92), коммутатором 42 (98.1-98.8) вырабатываются во второй половине такта (управляются четным выходом дешифратора 53 полутактов). Сигналы управления сумматором-вычитателем 39 (93-95) KOMNryTaTopoM 40 (96.1-96.2), комму30 татором 41 (97.1-97.2) и коммутато- ром 43 множимого (99.1, 99.2) должны сохраняться в течение такта (управляются сборкой нечетного и четного выходов дешифратора 53 полутактов

35 соответствующего такта). Регистры 1, 2, 6, 7, 13-16, 22, 26, 31 и 33 срабатывают в начале такта. Регистры 3, 8, 21, 25, 29, 32, 35, 46, 47, 105, 106 и 124 срабатывают в

40 конце такта.

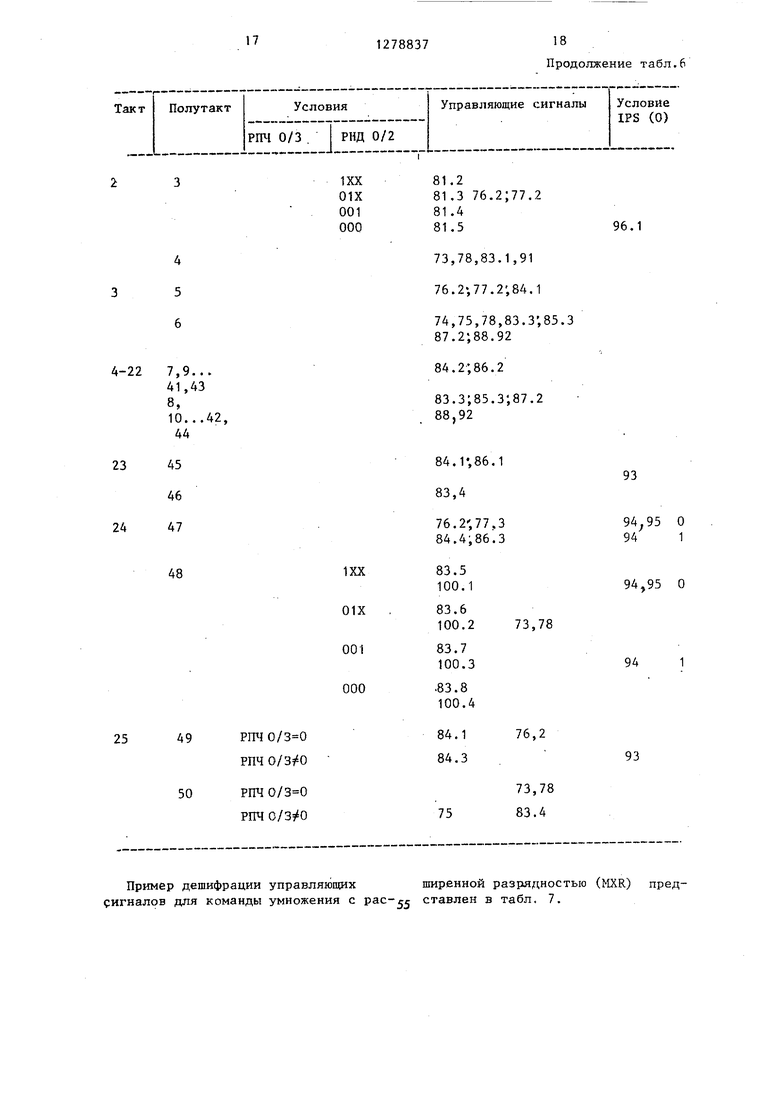

Пример дешифрации управляющих сигналов для команды деления (ДЦ) представлен Б табл. 6, где символ X оз- начает безразличное состояние раз45 рядов регистра 47 нормализации делителя .

Таблица 6

20

25

76.1;77.i;79.1 81.1

72,74,75,78 83.1;101

17

1ХХ 01Х 001 000

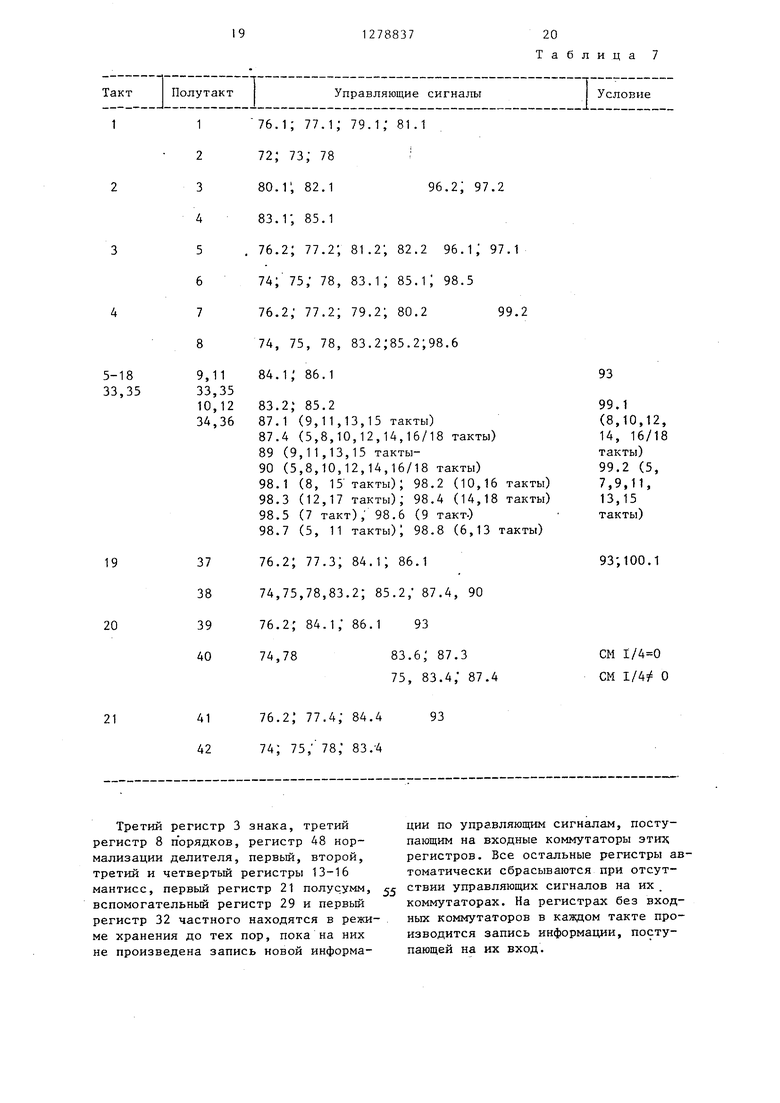

Пример дешифрации управляющих ширенной разрядностью (MXR) пред- сигналов для команды умножения с рас-гг ставлен в табл. 7.

1278837

18 Продолжение табл.6

76.2;77.2

96.1

3776.2; 77.з; 84.i; 86.1

3874,75,78,83.2; 85.2; 87.4, 90

3976.2; 84.1,- 86.1 93

4074,7883.6; 87.3

75, 83.4; 87.4

4176.2; 77.4; 84.4 93

4274; 75; 78; 83.-4

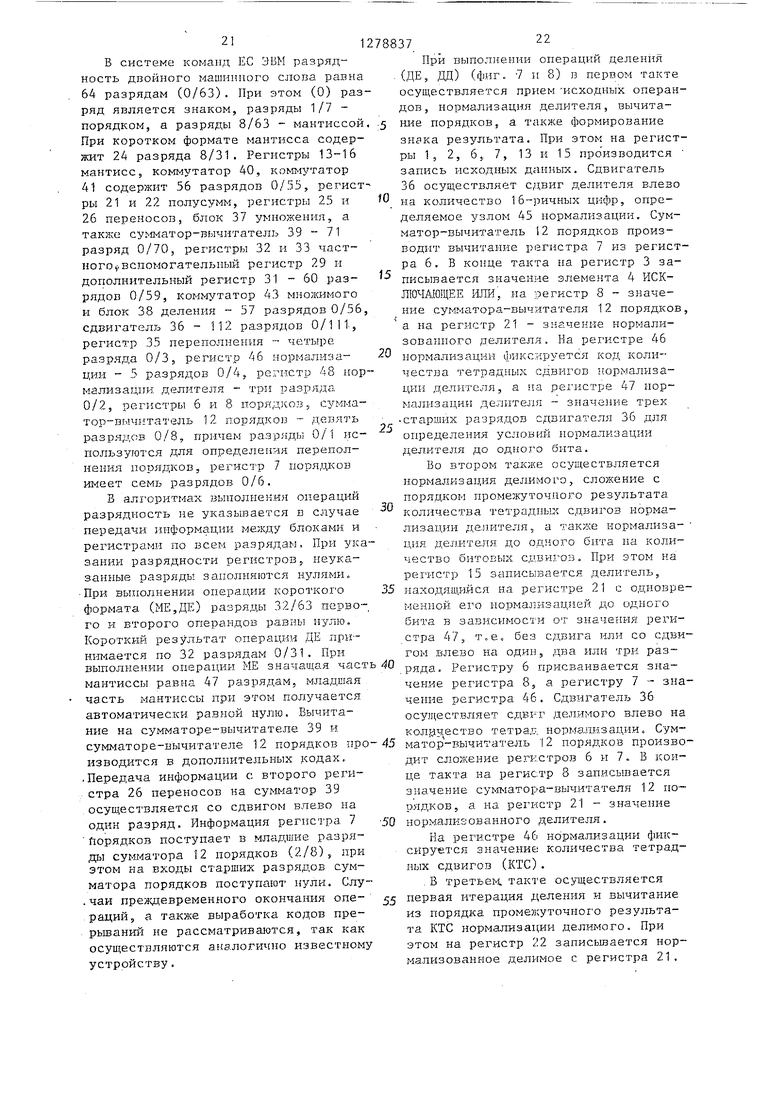

Третий регистр 3 знака, третий регистр 8 порядков, регистр 48 нормализации делителя, первый, второй, третий и четвертьй регистры 13-16 мантисс, первый регистр 21 полусумм, вспомогательньй регистр 29 и первый регистр 32 частного находятся в режиме хранения до тех пор, пока на них не произведена запись новой информа93; 100.1

см CM 1/4 О

ции по управляющим сигналам, поступающим на входные коммутаторы этих, регистров. Все остальные регистры автоматически сбрасываются при отсут- ствии управляющих сигналов на их . коммутаторах. На регистрах без входных коммутаторов в каткцом такте производится запись информации, поступающей на их вход.

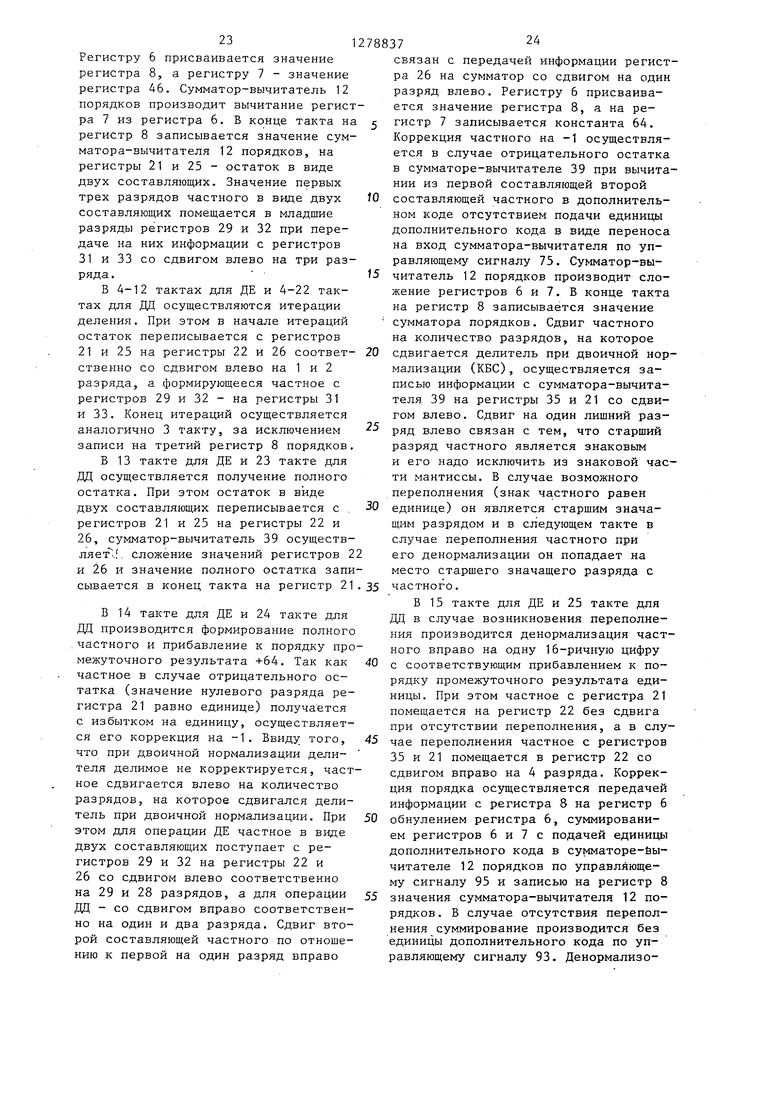

21

В системе команд ЕС ЭВМ разрядность двойного машинного слогза равна 64 разрядам (0/63) . При этом (0) разряд является знаком, разряды 1/7 - порядком, а разряды 8/63 - мантиссой. При коротком формате мантисса содержит 2А разряда 8/31. Регистры 13-16 мантисс, коммутатор 40, коммутатор 41 содержит 56 разрядов 0/55, регист-- ры 21 и 22 полусумм, регистры 25 и 26 переносов, блок 37 умножения, а также сумматор-вычитатель 39 - 71 разряд 0/70, регистр 32 и 33 част- ного вспомогательный регистр 29 и дополнительный регистр 31 - 60 разрядов 0/59, коммутатор A3 мнолдамого и блок 38 деления 57 разрядов 0/56, сдвигатель 36 - 112 разрядов 0/111, регистр 35 переполнения - четыре разряда 0/3, регистр 46 нормализации - 5 разрядов 0/4, регистр 48 нормализации делителя - три разряда 0/2, регистры 6 и 8 поряд1сов, сумматор-вычитатель 12 порядков - девя П разрядов 0/8. причем разряды 0/1 используются для определения переполнения порядков, регистр 7 порядков имеет семь разрядов 0/6,

В алг оритмах выполнения операц1-1й разрядность не указывается в случае передачи информации между блоками и регистрами по всем разрядам. При указании разрядности регистров, неуказанные разрядь заполняются нулями, При выполнении операции короткого формата (МЕ,ДЕ) разряды 32/63 перво-- го и второго оперггндов равны нулю. Короткий результат операции ДЕ принимается по 32 разрядам 0/31, При

10

f5

127883722

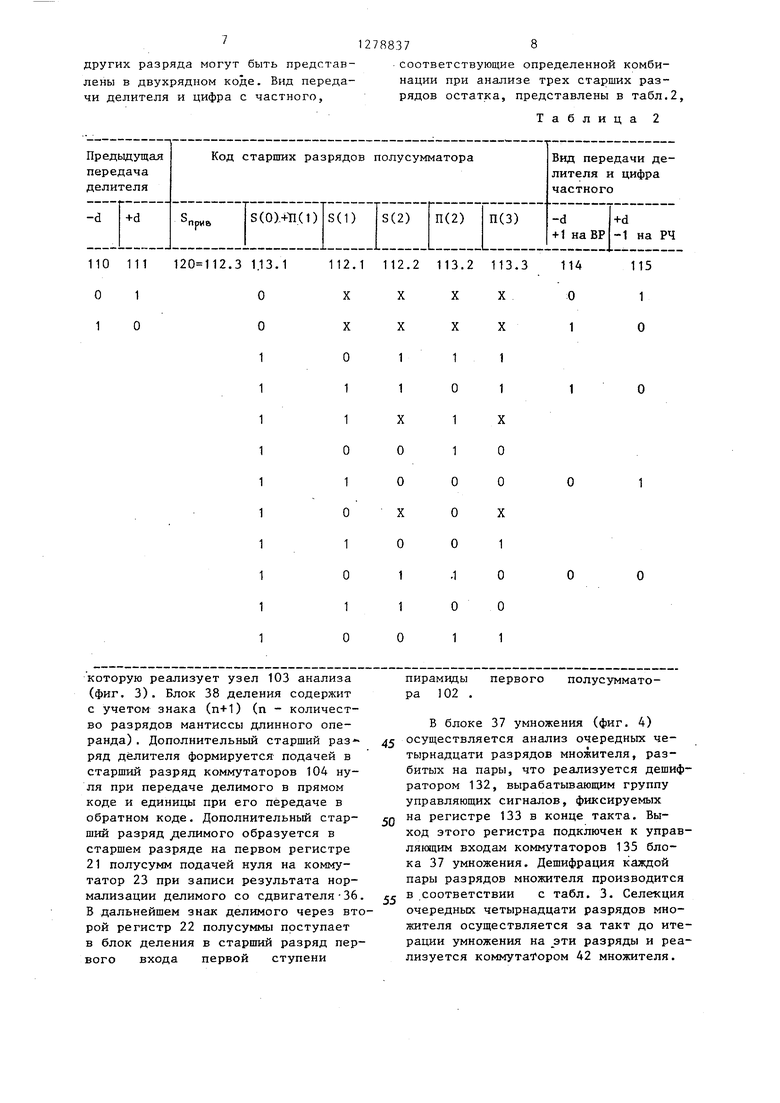

При выполнении операций деления (ДЕ, ДД) (фиг. -7 и В) в первом такте осуществляется прием исходных операндов, нормализация делителя, вычитание порядков, а также формирование знака результата. При этом на регистры 1, 2, 6, 7, 13 и 15 про изводится запись исходных данных, Сдвигатель 36 осуществляет сдвиг делителя влево на количество 1б-ричных цифр, определяемое узлом 45 нормализации. Сумматор-вычитатель 2 порядков производит вычитание регистра 7 из регистра 6, В конце такта на регистр 3 записывается значение элемента 4 ИСК- ЙПИ, на регистр 8 - значение суГ матора-вычитателя 12 порядков, а на регистр 21 значение нормализованного делителя. На регистре 46 нормализации фз-ткслруетСя код количества тетрад ых сдвигов нормализации делителя, а па р егистре 47 нормализации делителя - значение трех старших разрядов сдвигателя 36 для определения условий нормалр1зации делителя до одного бита.

Во втором такл(е осуществляется нормализация делимого, сложение с порядком промезкуточного результата количества тетрадных сдвигов нормализации делителя, а также нормализа- ция делителя до одного бита на количество битовых сдвигов. При этом на per -HCTj:i 15 записывается делитель, находяЕШЙся на регистре 21 с одновременной его нормализацией до одного бита в зависимости от значения регистра 47, , без сдвига или со сдвигом влево на один, два или три раз20

25

30

35

выполнении операции ME значащая часть 40 -рдда Регистру 6 присваивается зна- мантиссы равна 47 разрядам, младшая чение регистра В, а регистру 7 - зна- часть мантиссы при этом получается автоматически равной нулю. Вычитание на сумматоре-вычитателе 39 и

чение регистра 46, Сдвигатель 36 осуществляет СДВРГ делимого влево на

колрч.естЕо тетрад нормализации. Сум- сумматоре-вычитателе 12 порядков про-45 матор -вычитатель 12 порядков произвоизводится в дополнительных кодах, .Передача информации с второго реги- стра 26 переносов на сумматор 39 осуществляется со сдвигом влево на один разряд. Информация регистра 7 Лорядков поступает в младшие разряды суг-матора 12 порядков (2/8), при этом на входы старших разрядов сумматора порядков поступают нули. Слу- .чаи преждевременного окончания операций, а также выработка кодов пре- рьшаний не рассматриваются, так как осуществляются аналогично известному устройству,

10

f5

27883722

При выполнении операций деления (ДЕ, ДД) (фиг. -7 и В) в первом такте осуществляется прием исходных операндов, нормализация делителя, вычитание порядков, а также формирование знака результата. При этом на регистры 1, 2, 6, 7, 13 и 15 про изводится запись исходных данных, Сдвигатель 36 осуществляет сдвиг делителя влево на количество 1б-ричных цифр, определяемое узлом 45 нормализации. Сумматор-вычитатель 2 порядков производит вычитание регистра 7 из регистра 6, В конце такта на регистр 3 записывается значение элемента 4 ИСК- ЙПИ, на регистр 8 - значение суГ матора-вычитателя 12 порядков, а на регистр 21 значение нормализованного делителя. На регистре 46 нормализации фз-ткслруетСя код количества тетрад ых сдвигов нормализации делителя, а па р егистре 47 нормализации делителя - значение трех старших разрядов сдвигателя 36 для определения условий нормалр1зации делителя до одного бита.

Во втором такл(е осуществляется нормализация делимого, сложение с порядком промезкуточного результата количества тетрадных сдвигов нормализации делителя, а также нормализа- ция делителя до одного бита на количество битовых сдвигов. При этом на per -HCTj:i 15 записывается делитель, находяЕШЙся на регистре 21 с одновременной его нормализацией до одного бита в зависимости от значения регистра 47, , без сдвига или со сдвигом влево на один, два или три раз20

25

30

35

40 -рдда Регистру 6 присваивается зна- чение регистра В, а регистру 7 - зна-

-рдда Регистру 6 присваивается зна- чение регистра В, а регистру 7 - зна-

чение регистра 46, Сдвигатель 36 осуществляет СДВРГ делимого влево на

дит сложение регистров 6 и 7. В конце такта, на регистр 8 записывается значение сумыатора-вычитателя 12 порядков, а на регистр 21 - значение нормализованного делителя.

На регистре 46 нормализации фиксируется значение количества тетрадных сдвигов (КТС),

. В третьем, такте осуществляется первая итерация деления и вычитание из порядка промел;уточног о результата КТС нормализации делимого. При этом на регистр 22 записьшается нормализованное делимое с регистра 21,

23

Регистру 6 присваивается значение регистра 8, а регистру 7 - значение регистра 46. Сумматор-вычитатель 12 порядков производит вычитание регистра 7 из регистра 6, В конце такта на регистр 8 записывается значение сум- матора-вычитателя 12 порядков, на регистры 21 и 25 - остаток в виде двух составляющих. Значение первых трех разрядов частного в виде двух составляющих помещается в младшие разряды регистров 29 и 32 при передаче на них информации с регистров 31 и 33 со сдвигом влево на три разряда .

В 4-12 тактах для ДЕ и 4-22 тактах для ДЦ осуществляются итерации деления. При этом в начале итераций остаток переписывается с регистров 21 и 25 на регистры 22 и 26 соответственно со сдвигом влево на 1 и 2 разряда, а формирующееся частное с регистров 29 и 32 - на регистры 31 и 33. Конец итераций осуществляется аналогично 3 такту, за исключением записи на третий регистр 8 порядков.

В 13 такте для ДЕ и 23 такте для ДД осуществляется получение полного остатка. При этом остаток в виде двух составляющих переписывается с . регистров 21 н 25 на регистры 22 и 26, сумматор-вычитатель 39 осуществ- ляет.. сложение значений регистров 2 и 26 и значение полного остатка записывается в конец такта на регистр 21

В 14 такте для ДЕ и 24 такте для ДД производится формирование полного .частного и прибавление к порядку про

1

межуточного результата +64. Так как частное в случае отрицательного остатка (значение нулевого разряда регистра 21 равно единице) получается с избытком на единицу, осуществляется его коррекция на -1. Ввиду того, что при двоичной нормализации делителя делимое не корректируется, частное сдвигается влево на количество разрядов, на которое сдвигался делитель при двоичной нормализации. При этом для операции ДЕ частное в виде двух составляющих поступает с регистров 29 и 32 на регистры 22 и 26 со сдвигом влево соответственно на 29 и 28 разрядов, а для операции ДД - со сдвигом вправо соответственно на один и два разряда. Сдвиг второй составляющей частного по отношению к первой на один разряд вправо

fO

15

2 .35

20

25

27883724

связан с передачей информации регистра 26 на сумматор со сдвигом на один разряд влево. Регистру 6 присваивается значение регистра 8, а на регистр 7 записывается константа 64. Коррекция частного на -1 осуществляется в случае отрицательного остатка в сумматоре-вычитателе 39 при вычитании из первой составляющей второй составляющей частного в дополнительном коде отсутствием подачи единицы дополнительного кода в виде переноса на вход сумматора-вычитателя по управляющему сигналу 75. Сумматор-вычитатель 12 порядков производит сложение регистров 6 и 7. В конце такта на регистр 8 записывается значение сумматора порядков. Сдвиг частного на количество разрядов, на которое сдвигается делитель при двоичной нормализации (КБС), осуществляется записью информации с сумматора-вычитателя 39 на регистры 35 и 21 со сдвигом влево. Сдвиг на один лишний разряд влево связан с тем, что старший разряд частного является знаковым и его надо исключить из знаковой части мантиссы. В случае возможного переполнения (знак частного равен единице) он является старшим значащим разрядом и в следующем такте в случае переполнения частного при его денормализации он попадает на место старшего значащего разряда с частного.

В 15 такте для ДЕ и 25 такте для ДЦ в случае возникновения переполнения производится денормализация частного вправо на одну 16-ричную цифру с соответствующим прибавлением к порядку промежуточного результата единицы. При этом частное с регистра 21 помещается на регистр 22 без сдвига при отсутствии переполнения, а в случае переполнения частное с регистров 35 и 21 помещается в регистр 22 со сдвигом вправо на 4 разряда. Коррекция порядка осуществляется передачей информации с регистра 8 на регистр 6 обнулением регистра 6, суммированием регистров 6 и 7 с подачей единицы дополнительного кода в cyNMaTope-йы- читателе 12 порядков по управляющему сигналу 95 и записью на регистр 8 значения сумматора-вычитателя 12 порядков . В случае отсутствия переполнения суммирование производится без единицы дополнительного кода по управляющему сигналу 93. Денормализо30

40

45

50

55

ванное частное поступает на регистр 21 с сумматора-вычитателя 39 посредством сложения регистров 22 и 26 на сумматоре-вычитателе 39, так как регистр 26 обнуляется,

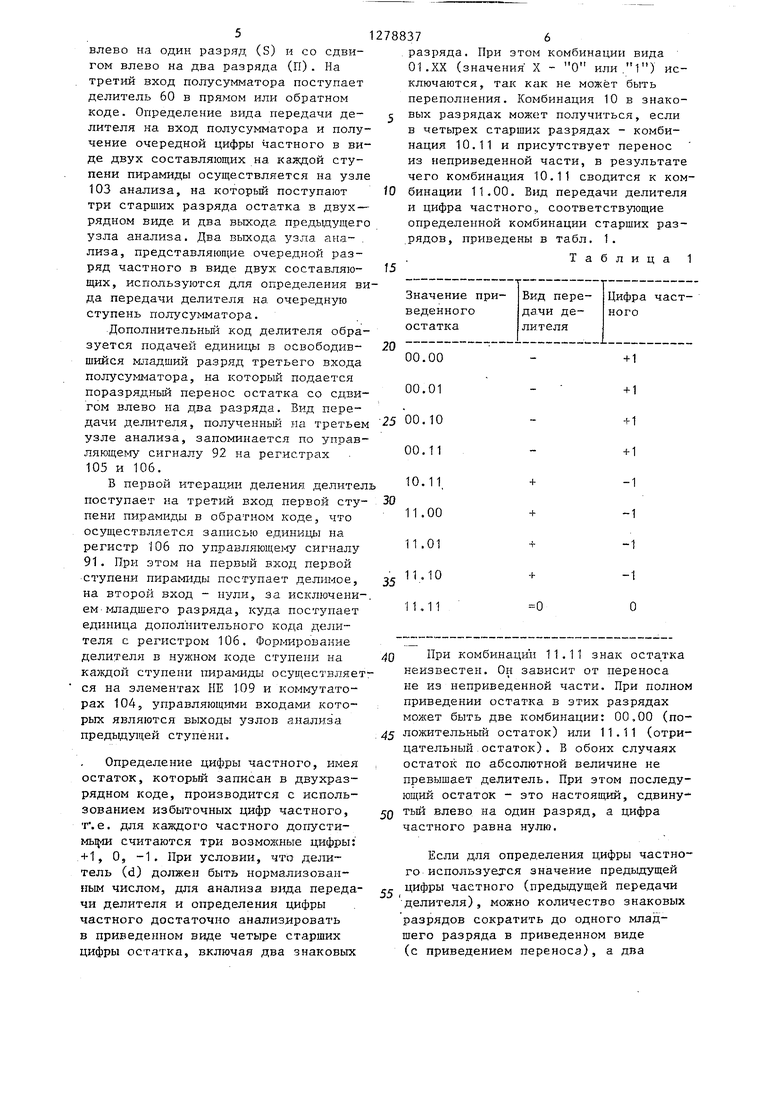

Для команд умножения (ME, МД, МХД) в первом такте осуществляется прием исходных операндов, нормализация мнолсителя, сложение порядков, (получение порядка промежуточного результата +64), а также формирование знака результата (фиг. 5 и 6), При этом последовательность выполняемых действий в устройстве аналогична пер- вомз такту операций деления. Исключение составляет сложение порядков вместо их вычитания при делении и отсутствие записи на регистр 47 нормализации делителя.

Во втором такте осуществляется нормализация множимого и вычитание из порядка промейсуточного результата количества тетрадных сдвигов нормализации множителя. При этом последовательность выполняемых действий в устройстве аналогична втopo fy такту операций деления. Исключение составляет вычитание порядков вместо их сложения и передача с рег истра 21 на регистр 15 без сдвига,

В третьем такте осуществляется первая итерапия умножения и вычитание из порядка промежуточного результата КТС нормализацрп множимого.При этом нормализова1июе множимое помещается на регистр IB действия с порядгсами аналогичны 2 такту умножения а промежуточны результат у1 нонсення в виде двух составляющих поступает из блока 37 умножения на регистры 21 и 25.

В четвертом такте для команды ME осуществляете последняя итерация умножения и вычитание -64 из порядка промежуточного результата. Для команд МД, ЫХД в 4-6 тактах осуществляются итерации умножения, причем в 4 такте производится вычитание -64 из общего порядка. При этом действия с порядками в 4 такте аналогичны 14 такту операции деления для ДЕ, отличие состоит лишь в том, что сумматор-вычитатель 12 порядков выполняет функцию вычитания .

В начале каждой итерации умножения осуществляется передача промежуточного результата в виде двух составляющих с регистров 21 к 25 на регист

5

0

5

0

5 5

0

5

Q

0

ры 22 и 26, а младшая часть произведения, формирующаяся на регистре 29, доступает на регистр 31. На регистре 29 формирование младшей части произведения начинается в конце 4 такта, поэтому передача в начале 4 такта с регистра 29 на регистр 31 производится для сохранения стандартности итераций умножения. Итерации умножения заканчиваются записью промежуточного умнолсения в виде двух составляющих на регистры 21 и 25, а также фиксацией 14-ти разрядов младшей части произведения, получаемьос на сумматоре-вычитателе 39, в старшие 14 разрядов регистра 29 с одновременной передачей информации с регистра 31 на регистр 29 со сдвигом вправо на 14 разрядов. Формирование младшей части произведения, полученной от предьщу- щей итерации умножения, необходимо для команды МХД, но для стандартности итераций умножения соответствующие передачи осуществляются в каждом такте..

В пятом такте для ME и седьмом такте для ВД, на сумматоре-вычитателе 39 вычисляется старшая часть произведения с записью результата на регистр 21 со сдвигом влево на четыре разряда и с передачей информации с регистра 31 на регистр 29 со сдвигом вправо на 10 разрядов, если требуется нормализация с одновременной коррекцией порядка промежуточного результата на -1. На регистре 29 заканчивается формирование младшей части результата, для команды МХД.

Коррекция порядка осуществляет ся передачей информации с регистра 8 на регистр 6, обнулением регистра 7, вычитанием из регистра 6 регистра 7 с отсутствием подачи единицы дополнительного кода в сумматор-вычитатель 12 порядков по управляющему сигналу 75 и записью на регистр 8 значения сумматора порядков. В случае СМ(1/4) О вычитание производится без блокировки единшда дополнительного кода по управляющим сигналам 74 и 75..

В 8 такте для МХД младшая часть результата помещается на регистр 21 и формируется порядок младшей части результата (порядок старшей части -14). При этом -шадшая часть результата с регистра 29 поступает на регистр 22 со сдвигом вправо на один

27

разряд, чтобы старший разряд младшей части результата не оказался в знаковом разряде регистра 21, регистр 26 обнуляется, сумматор-вычитатель ,производит , сложение и на регистр 21 записывается значение сумматора- вычитателя 39.

Порядок младшей части результата формируется следующим образом. Информация с регистра 8 поступает на регистр 6, на регистр 7 заносится константа 14, сумматор 12 порядков производит вычитание и результат сумматора поступает «а регистр 8.

Для команды MXR (фи. 7 и 8) в первом такте производятся прием старших частей сомножителей, сложение порядков (получение общего порядка промежуточного результата +64), а также формирование знака результата. При этом производятся действия, аналогичные первому такту МД, за исключением нормализации.

Во втором такте также осуществляются прием младших сомножителей и нормализация множителя. При этом на регистры 14 и 16 производится запись мантисс первого и второго операндов, сдвигатель 36 осуществляет нормализацию, результат сдвигателя 36 заносится на регистры 21 и 25, а на регистр 46 нормализации - значение КТО

В третьем такте осуществляются нормализация множимого и вычитание из порядка промежуточного результата количества тетрадных сдвигов нормализации множителя. При этом нормализо- ванньш множитель поступает с регистров 21 и 25 соответственно на регистры 15 и 16.

Действия с порядками полностью аналогичны 2 такту команды ВД. Результат нормализации множимого заносится на регистры 21 и 25, а на регистр 46 нормализации - значение КТСВ четвертом такте осуществляются первая итерация умножения и вычитание из порядка промежуточного результата КТС нормализации множимого. При этом нормализованное множимое помещается на регистры 13 и 14. Действия с порядками полностью аналогичны третьему такту. На регистры 21 и 25 фиксируется промежуточный результат умножения в виде двух составляющих.

В 5-19 тактах осуществляется итерация умножения, причем в 19 такте производится вычитание -64 из поряд

.

.788372

ка промежуточного результата. Промежуточный результат предыдущей итерации в 9, 11, 13 и 15 тактах поступает в пирамиду умножения без сдви га вправо на 14 разрядов. При этом действия с порядками в 19 такте полностью аналогичны 4-му такту команды ME. В начале каждого такта осуществляется передача промежуточного ре10 зультата в виде двух составляющих с регистров 21 и 25 на регистры 22 и 26, а младшая часть произведения, формирующаяся на регистре 29, поступает на регистр 31. На регистре 29

t5 формирование младшей части произведения начинается в конце 5 такта, поэтому передача в начале 5 такта с регистра 29 на регистр 31 произво- дится для сохранения стандартности

20 итераций умножения. В каждой итерации умножения сумматор-вычитатель 39 производит сложение регистров 22 и 26, а на регистры 21 и 25 производится запись полусумм и переносов из

блока 37 умножения. В 8, 10, 12, 14, 16/19 тактах на выход коммутатора 43 множимого поступает значение регистра 13, а в 5, 6, 9, 11, 13 и 15 тактах - значение регистра 14.

30 В 5, 8, 10, 12 и 14 тактах осуществляется передача полной четырнадцатиразрядной суммы младшей части результата, получаемой на сумматоре- вычитателе 39, на регистр 29 с одно35 временной передачей информации с р е- гистра 31 на регистр 29 со сдвигом вправо на 14 разрядов. Так как в 9, 11, 13 и 15 тактах промежуточный результат поступает в блок 37 умно40 жения без сдвига вправо на 14 разрядов, передача информации с регистра 31 на регистр 29 осуществляется без сдвига.

45 В двадцатом такте на сумматоре- вычитателе 39 вычитается старшая часть произведения с записью результата на регистр 21 со сдвигом влево на четыре разряда и с передачей ин50 формации с регистра 31 на регистр 29 со сдвигом вправо на 10 разрядов, если требуется нормализация, с одновременной коррекцией порядх са промежуточного результата на -1. На рс55 гистре 29 заканчивается формирование младшей части результата. Вся последовательность выполняемых действий полностью аналогична седьмоь1у такту для команды МХД.

291278837

В двадцать перьэом такте младшая асть результата помещается па реистр 21 и формируется порядок младей части результата (порядок старей часты -14). При этом вся после- овг1тельность выполниемых дмйстгзий олностью а}1алогнчпа восьмому такту ля команды МХД.

со вы ве ны по ин му по по вт ко го по яв .ва с те ци ве ко ко но пе вс ве пе ре по вх вы то ро

Формула изобретения

1. Устройство для умножения и деления с плавающей точкой, содержащее три регистра знака, коммутатор знака, три регистра порядков, три коммутатора порядков, д.иа регистра мантисс, два коммутатора мантисс, два регистра полусумм, два коммутатора полусумм, два регистра переносов, два коммутатора переносов, вспо могатс;льн1лй регистр., вспомот ательный коммутатор, сдвигатель, коммутатор двигаемо информации, блок умножения, сумматор-вычитатель, сумматор- вычитатель порядков, элемент ИСКЛЮЧА- ЩЕЕ КПИ, регистр команд, узел нормализации , регистр нормализ ации, элемент ИЛИ, счет -гик полутактов и блок деления, содерл;ащий первый узел анализа группы и первый регистр,при- чем в устройстве вход перзюго регистра знакгг, первый информ.циопь:ый вход первого коммутатора порядков и первый инфо1)ма.ционнь й в ход первого коммутатора мантисс являются входом первого операнда устройствг ., вход второго регистра знака, первый информационный вход-ВТО1ТОГО .коммутатора порядков и первый информационный вход второго коммутатора, мггнтисс лв.пяютс,ч информа- ционнь м входом второго операнда устройства,, вход регистра команд яв.пяет- ся вхо.цом вида операции устройства, разрядный выход регистра команд . с;:;е динен с входами э..ттамента ИЛИ, выход, которого соединен с входом счетчака полутактов, выход первого и второго регистров зг(ака соединены соответственно с первым и вторым входами элемента ИС1ШОЧ.АЮ1ДЕЕ ШШ, выход которо- го подключен к информационному входу коммутатора, знака, выход которого соединен с входом третьего ре1гистра знака, второй и третий информационные входы второго коммутатора поряд- 55 комментаторы мантисс, два регистра

ков подключены к входам пергвои я второй констант стройства соответственно, выходы первого и второго коммутаторов порядков сое,дииетгг.г с входа.ми

30

соответствующих регистров порядков, выходы которых сс;единены соответственно с вторым и первым информационными входами сумматора-вычитателя порядков, выход которого соединен с информацион - ЫМ входом третьего коммутатора порядков, вгз1х.од которого подключен к входу третьего регистра порядков, выход которого соединен с вторым информационныхМ входом первого комг-гутатора порядков, выходы третьего регистра знака, третьего регистра порядков и первог о регистра полусумм яв.ляются выходом результата устройст- .ва, выход узла нормализации соеди1 ен с входом ко.гп-гчества сдвигов сдвига- теля и с входом регистра нормализа- ци и, выход которс.ч о соедипсн с четвертым информационным входом второго коммутатора ,кoв,, выходы первого коммутатора полусумм и вспомогательного коммутатора подключены к входу первого регистра полусумм и входу вспомогательного регистра соответственно, выход первого коммутатора переносов соединил- с входом первого рег нстра переносов, выход которого подключен к первому информационному вхо,цу второго комггутатора переносов, выход которого соединен с входом вто- того pei HCTpa переносов, выход которого подк.г1.:г.1сн к первому рп1формацион

ному вход .у с 5 мматора.-БЫчитателя, второй информациг. нный вход которого соединен с выходом второго регистра по.лусумм, вход которого подключен к выходу второго коммутатора полу- первый инфг)рмационный .вход которого соединен с выходоь первого pen-iCTpa полусумм, с вторыми информационными входаг- И первого и второго коммутаторов мантисс, выходы которых по;.1,к.1почены к входам первого и второго регистров ман ) исс соотве гственно, выходы кото1 ых соединены соответственно с первым и }зторым 1-и-1формацион- Бходаии коммутатора сдвигаемой информации, BhiixoM которого соединен с информа.ционны 4 входом сдзигателя, о т л и ч а ю ш е е с я тем, что, с целью liOBBimeHF.;: быстродействия,

оно содер/KiiT третий и четвертьй регистры ма)гтисс. третий и четвертый

частного, коммутг1тор частного, дополнительный регистр, регистр переполнения, ко1 .гмутатор переполнения, ре- г.истр нормализации дел1П еля, комму311

татор нормализации делителя, дополнительный коммутатор сдвигаемой информации, коммутатор множимого, коммутатор множителя, дешифратор полутактов, дешифратор управляющих сигналов, а блок деления дополнительно содержит полусумматор группы, два узла анализа группы, коммутаторы делителя группы, второй регистр, два коммутатора, группу элементов НЕ, причем каждьй узел анализа содержит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, восемь элементов И, два элемента ИЛИ и пять элементов НЕ, причем-в устройстве первые информационные входы третьего и четвертого коммутаторов мантисс соединены с выходом первого регистра переносов, вторые информационные входы третьего и четвертого коммутаторов мантисс соединены с входами первого и второго операндов устройства соответственно, выходы третьего и четвертого коммутаторов мантисс соединены с входами третьего и четвертого регистров мантисс соответственно, выходы которых подключены соответственно к первым информационным входам дополнительного коммутатора сдвигаемой информации, коммутатора множимого и к первому информационному входу коммутатора множителя, к второму информационному входу дополнительного коммутатора сдвигаемой информации, выход которого соединен с входом узла нормализации и с инфор мационным входом сдвигателя, первый информационный вход коммутатора сдвигаемой информации подключен к второму информационному входу коммутатора

множимого, выход которого соединен с входом множимого блока умножения, вход множителя которого подключен к выходу коммутатора множителя, вход промежуточных сумм блока умножения подключен к выходу второго регистра, полусумм и к первому входу первого полусумматора группы блока деления, вход промежуточных переносов блока умножения подключен к выходу второго регистра переносов и к второму входу первого полусумматора блока деления, вход переноса блока умножения подключен к выходу сумматора-вычитателя, к информационному входу коммутатора переполнения, выход сумматора вычитателя соединен с первыми информационными входами вспомогательного коммутатора, первого коммутатора

7Я83732

полусумм и с первым зходом дешифратора управляющих сигналов, выход сумм блока умнрженил подключен к второму информационному входу первого комму- татора полусумм, выход переносов блока умножения подключен к первому информационному входу первого коммутатора переносов, второй информационный вход которого соединен с выходом to сдвигателя, с информационным входом ко.пу|утатора нормализации делителя и с третьим информационным входом первого коммутатора полусумм, четвертым информационный вход которого под- 15 ключен к выходу сумм последнего полусумматора группы блока деления, выход переносов которого соединен с третьим информационным входом первого коммутатора переносов, первые ин- 20 формационные входы коммз таторов делителя группы и входы элементов НЕ группы блока деления подключены к выходу второго регистра мантисс и к второму информационному входу комму25

татора множителя, выходы первого и

второго элементов ШШ узлов анализа группы блока деления подключены к информационному входу коммутатора частного и к BTOpONry информационному

30 входу вспомогательного кo мyтaтopa, третий информационньй вход которого соединен с выходом дополнительного регистра, вход которого подключен к выходу вспомогательного регистра 35 1 к второму информационному входу второго коммутатора полусумм, выход коммутатора частного соединен с входом первого регистра частного, выход которого подключен к второму ин40 формационному входу второго коммутатора переносов и к входу второго регистра частного, выход которого соединен с информационным входом коммутатора частного, выход комьгутатора

45 нормализации делителя подключен к

:входу регистра нормализации делителя, выход которого соединен с вторым входом дешифратора управляюш,их сигналов, выход коммутатора перепол50 нения подключен к входу регистра переполнения, выход которого соединен с первым информационньм входом второго коммутатора полусумм и с -третьим входом дешифратора управляющих

сигналов, четвертый вход которого -подключен к выходу первого регистра полусумм, пятый вход дешифратора управляющих сигналов подключен к выходу дешифратора полутактов, вход

которого соединен с выходом счетчика полутактов, выход регистра команд подключен к шестому входу дешифратора управляющих сигналов, выходы кото рого соединены соответственно с управляющим входом коммутатора знака, с входом управления сложением, с входом управления вычитан1 ем и с входом переноса сумматора-вычитателя порядков, с управляющим входами первого, второго и третьего коммутаторов порядков, с управляющими входами первого, второго, третьего и четвертого коммутаторов мантисс, с управляющими входами первого и второго коммутаторов полусумм, с управляющим входами первого и второго коммутаторов переносов, с управляющим входом вспомогательного коммутатора, с управляющим входом коммутатора частно- го, с входами разрешения и сдвига блока умнолсения, с вторыми первым управляющими входами второго коммутатора блока деления, с входом управления сложением, с входом управления вычитанием и с входом переноса сумматора-вычитателя, с управляюа;им входом коммутатора сдвигаемой информации, с управляющим входом дополнительного коммутатора сдвигаемой информации, с управляющим входом коммутатора множителя, с управляющим входом коммутатора множимого, с управляющим входом коммутатора переполнения и с управляющим входом коммутатора нормализации делителя, причем в блоке деления выходы элементов НЕ группы подключены к вторым информационным входам коммутаторов делителя группы, выходы сумм и переносов каждого предыдущего полусумматора группы соединены соответственно с первым и вторым входами последующего полусумматора группы, выходы коммутатора делителя группы соединены с третьими входами соответствующих полусумматоров группы, разряды выхода сумм полусумматоров группы соединены соответственно с входами первого и второго элементов НЕ и с первым вводом элементов ИСКЛЮЧАЮЩЕЕ 1 ШИ соответствующего узла анализа группы разряды выхода переносов полусумматоров группы соединены соответственно с входами третьего и четвертого элементов НЕ и с вторыми входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соответствующего узла анализа группы, первые входы первого и второго элементов И каждог

O

5

5

0 5

узла анализа группы соединены соответственно с первым и вторым управляющими входами соответствующего коммутатора делителя группы и с выходами первого и второго элементов ИЛИ предыдущего узла анализа группы, выходы первого и второго регистров соедине- ны соответственно с первым и вторым управляющими входами первого коммутатора делителя группы, первый вход второго элемента PI узла анализа группы соединен с вторым входом соответствующего полусумматора группы, выход первого элемента ИЛИ последнего узла анализа группы соединен с информационным входом первого коммутатора, выход которого подключен к входу первого рех истра, управляющий вход первого коммутатора подключен к первому управляющег-о входу второго коммутатора, выход которого соединен с входом второго регистра, второй управляющий вход второго коммутатора соединен с первым информационным входом второго ког-мутатора, второй информационный вход которого соединен с выходом второго элемента ИЛИ последнего узла анализа, причем в узле анализа первый вход третьего элемента И подключен к выходу первого элемента НЕ н к первым входам четвертого и пятого элементов И, второй вход третьего элемента И подключен к входу второго элемента НЕ и

5 к первому входу шестого элемента И, третий вход третьего элемента И подключен к входу третьего элемента НЕ, к второму входу пятого элемента И и к первому входу седьмого элемента-И,

0 четвертый вход третьего элемента И подключен к входу четвертого элемента НЕ и к второму входу шестого элемента И, пятьй вход третьего элемента И подключен к выходу элемента ИСК5 ЛЮЧАЮЩЕЕ KHIi, входу, пятого элемента НЕ, к вторым входам четвертого и седьмого элементов И, к третьим входам пятого и шестого элементов И и к,первому входу восьмого элемента И, выход третьего элемента И подключен к первому входу второго элемента ИЛИ, втор.ой вход которого соединен с выходом шестого элемента И, четвертый вход которого подключен к выходу третьего элемента НЕ, к ,третьему входу четвертого элемента Инк второму входу восьмого элемента И, пятый вход шестого элемента И подключен к входу первого элемента

0

0

351

НЕ, к третьему входу восьмого элемента И и к третьему входу седьмого элемента И, выход которого соединен с третьим входом второго элемента ИЛИ, четвертый вход которох о подключен к выходу второго элемента И, второй вход которого соединен с выходом пятого элемента НЕ и с вторым входом первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, третий вход первого элемента РШИ соединей с выходом пятого элемента И, четвертый вход кото рого подключен к выходу второго элемента НЕ и четвертому входу восьмого элемента И, пятый вход пятого элемента И подключен к выходу четвертого элемента НЕ и к пятому входу восьмого элемента И, выход которого соединен с четвертым входом первого элемента ИЛИ.

2. Устройство по п. 1, отличающееся тем, что блок умножения содержит группу коммутаторов кратных, группу элементов ИЛИ, группу элементов НЕ, элемент И, восемь полусумматоров, два коммутатора, деишфратор множителя и регистр, причем вход множителя блока умножения соединен с входом дешифратора множителя, выход которого соединен с входом регистра, выходы разрядов которого соединены соответственно с управляющими входами коммутаторов кратных группы, третий и четвертый управляющие входы коммутаторов кратных группы, кроме последнего, соединены соответственно с первым и вторым входами соответствующего элемента ИЛИ группы, выход первого коммутатора кратных группы соединен с первым входом первого полусумматора, второй вход которого соединен с выходом второго коммутатора кратных группы и с выходом первого элемента ИЛИ группы, выходы третьего коммутатора кратных группы и второго элемента ИЛИ группы соединены с третьим входом первого полусумг-штора, выходы сумм и переносов которого соединены соответственно с первым и в Го рым входами второго полусумматора, третий вход которого соединен с. выходами четвертого коммутатора кратных группы и третьего элемента ИЛИ группы, выходы сумм и переносов вто

15

20

883736

рого полусумматора соединены соответ- стБен1 о с первым и вторым входами третьего полусумматора, третий вход которого соединен с выходом сумм

5 четвертого, полусумматора, первый вход которого подключен к выходам пятого коммутатора кратных группы и четвертого элемента ИЛИ группы, выходы iJiecToro коммутатора кратных группы

0 II пятого элемента ИЛИ соединены с , первым входом пятого полусумматора, второй вход которого соединен с выходами седьмого коммутатора кратных группы и шестого элемента ИЛИ группы, выходы восьмого коммутатора кратных группы и седьмого элемента ИЛИ группы соединены с третьим входом пятого полусумматора, выходы сумм и переносов которого соединены соответственно с вторым и третьим входами четвертого полусумматора, выход переносов которого соединен с первым входом шестого полусумматора, второй и третий входы которого соединены с выходами первого и второго коммутаторов соответственно, выходы сумм и переносов шестого полусумматора соединены соответственно с первыми входами

эп седьмого и восьмого полусумматоров, выходы сумм и переносов третьего полусумматора соединены соответственно с вторым и третьим входами седьмого полусумматора, выходы сумм и переносов которого соединены соответственно с вторым и третьим входами восьмого полусумматора, выходд сумм и переносов которого являются соответственно выходами сумм и переносов блока умножения, первьш вход

восьмого полусумматора соединен с 1

выходом элемента И, первый вход которого подключен к входу сдвига блока умножения и к первым управляюнц-ш

5 входам первого и второго коммутаторов, вторые управляющие входы которых соединены с входом разрешения .блока умножения, информационные входы первого и второго коммутаторов

5Q соединены соответственно с входами промелсуточных сумм и переносов блока умножения, вход переноса которого соединен с вторым входом элемента И и с информационным .входом первого

55 коммутатора, вход множителя блока умножения соединен с входами элементов НЕ группы и с первыми информационными входами коьп-гутаторов кратных группы, выходы элементов НЕ груп35

37127883738

пы соединены с вторыми информа-кратных, кроме последнего , групционными входами коммутаторовпы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Арифметическое устройство с плавающей точкой | 1985 |

|

SU1259248A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| УСТРОЙСТВО ДЕЛЕНИЯ И ИЗВЛЕЧЕНИЯ КВАДРАТНОГО КОРНЯ | 2012 |

|

RU2510072C1 |

| Конвейерное устройство для деления | 1985 |

|

SU1297037A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для умножения и деления | 1986 |

|

SU1376082A1 |

| Вычислительное устройство | 1979 |

|

SU885994A1 |

Изобретение относится к вычислительной технике и может быть использовано в составе мультипроцессора быстродействующих ЭВМ. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигнута с помощью введения в устройство, содержащее регистр 50 команд, три 7Z-KS1 Фиг..

К 63

аг г

70 5fi4

ТО

7/;

т

(55

6S S7

Фиг. Ч

М,мг удд. начало

p3:«/onf «; грз:- гап(а

ItnvnsJftOnCt/J -: 2PnP :Of6 : 20n lhl

iPHColss : -lonra/Bti 1 грм ro/ss : zon slS33

HCt-fpn; B/( Свп: CSKIinJi-KCCOlSS, SKC OlsSlJIKTt

+ грз j зрпр-.тсвп tPSttlSSJ-.CSLO/SS ; Рн(1/ч}; кгг

IfMfa/SSJ: -fPSCt/SSJ IPnpl SPnp; 2PnP lfS ---PH 0/fJ SK: 0

(Sfa/itt}:-Kcfs/ssj,y/ cfff/ssJJKKrc}

ten: Vnp-lpnp PS lf5ei:- CnC(l5SJ

ЗРПр; Свп; pH o/f}: Krc

pHceiS5 :-4Psi:itsB} tPffp-.Jpap; iPnpLtl6 -- PH 0/4J свп: 1рлр-грлр

IPSs -eys; 1Рп: БУГ};

ЗРПР в СвП

62 11 63

Imaim

гтакп

Зшакт

УРЗ-.- гОПСО

. Vni: /iJ; 2pni:o/s . 2onl | з

, S5. о JOnCSlSJJ; 2PMLQI55 . -«ХпСв/Ви

can: « }рпр грпр

ЗРЗ: 1РЗ 2RJ; ЗРПр: «СЯ/7

3PMCOl55J- °TOnCSl633; ЧРМСо1553- гОПСа вЗЗ КС:-а гРМ; SKC црм CnfO/ni : -KCi:o/S53;SnC 0/55Jji(KTC)

IPSf 1/383; спса/ззз; tPHfi/ssj-. cntsstwJ

КТС

ZPMCatSSl: PSf lISBJ; РПР:

4PMt:o/ss3 tpnc)/5ej; гРпрС21Б1- рн о/чз

tf с: 1РМ; тс -.SPM

cni:onn:i-- HcCo/ss3,D ccols53Jt{KTc)

- ZPnp

IPSC J/S6J : CDCOlSSJ; P/7f J/5fij CBr55/rnj

ЗРПР СВП; РНСО/Ч .- ЯГС

TpMco/ss ;/56J; 3PM o/s5:}:- iPni:i/ss3

РПР: ЗРЛР; ZPHPf /eJ-.PHCO/tfJ

свп: 1рпр-грпр

KM : « JPM; гда : CtfS; ГW7: ЙОТ

3Pffp; rs/7

в 19 такте

2PS:-№s; SP-.- Bp

1РПр ЗРПр; ZPnP :aJ:°t

СВп: «tPnP-ZPnp

ЗРПР: СВП

км: 7ЯМ 5 и к,/, 14IS/13 тактак.

км: в 5/7, ff, П,3, К /пактах

ев: грз -f грп рзг , „ . sprnjaj:« cef57/7(7J I ° M C W ВР1:- ч1551: °Др о1чПШЧ Kha тантал BPfO/sSJ: jSPfO/SSj 8 9, tJ. 13, К тактац

Кап

J

0 7 такте Sin

I такт

гтакт

Зтакт.

ti такт.

в 19 такте

5i-19 такты

J

гогпант.

(7(OHet4 aS,;

J,J7J7 (начало

2Рд: 20ПГО:

1РПР L 2181: ion LI 113- 2PnP Ol61 20nll/il

Wn :8/63 j 2PMLOJ553:--20ni:8/653

)

СИ f:oliliJ: KCCO/55}; MCLolsSlJ)(KTC)

СВП1 1РПР 2РЛР

2P3j ЗРЛР: СвЛ

1P3Ll/563:--cni:0/55J

PH L0|l KTC , PHJ} CS CO/21

2PMLOl551: mCH56JJ} (КБС)

где )ОгЗ

1РПР: ЗРЛР у 2PnpL2l6l: PH 0/i4l

, ПКС 0

СП СО 1т т, КС f «7/J57; ПК С LolSSlJl (К ТС)

С В ft: РПР +2pnPj ЪРПР:

WS j563: CDCO{553j Р//Г%7: ЯГС

2PS- -IPS

1РПР - РПР j 2РПР

СВП: 1РПР-2РПР ЗРПР: СВП

1Р$ LQ 1561.-BUS Lois61; lPnLQl561: 6HnLQl56

BPi:oi56J: p 3/S33JJ3j BPL5ll53l: lLOl22

WzLQisei-. 2PZ 3I531J1Z , 1PIL57I59 : 12COI21

1 тонт

2 такт.

такт

Фиг.$

2Р5 0/551: 1Р5 1561Щ 2Pn olff{ : lPnLZ/56 JJ2

PS,Lol5Bl - dS&LOl551; 1Pn 0/561: 6SnCO/S6 BPCOlSO : БР1:3/59 ЛЗ; BPL5l}591: IHOJ

PtcQlsoi; гр «/55JJ73; jpi 5ijs9 : 2 olzi

: PS: --JPSf 2РП; --1РП) }PSL(l55 : -CMi:0/56

2 PS Lll30 : BP y l 33Ji29 2РП112/311: lPlLWl53 n28 2 PS Jlsol: - BpfO/ SJ nl

2РШ216П .- mcoisBinz

1РПР- 2РЛР; 2PnPLOT l Cli:-- , если PSC01 0 CB: 2PS 2pn-l, если IPSCOJ-l С ВП: - WnP -f- 2PIW-, 5РПР СВП РП1 CO/3J- CBil/ JJ ( К SC-t-1} IP31:1/55 : CBL2lS(J3M {КБС-t-J)

длл

для

веля pnt 0/31-0

2PS.: IP

С8П . iPnp+2PnP

2PSLll4- : Pni Ol31

2Pf i:5l56 i если P/Jl ol3J7

СВП- РПР- 2РПР- -

. ТРПР . бРПр- 2РПР:-0

СВ-

ЛЯ/// : СВП} PS O/SGJ: CBLOlSGl

.„i™.

)

Редактор Л.Гратилло

Заказ 6839/Д7Тираж 671 Подписное

ВНШПИ Государственного комитета СССР

по делам изобретенш и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно--гюлиграфическое предприятие, г.Ужгород, ул.Проектная, 4

fnoKmuff/ ff ж -2Z танты d/w HD

1Ътакт длй S 2Ъ(ланп1 для ЛБ

дллЖ

И такт для J)E 24 такт дм ИБ

веля pnt 0/31-0

n4 если P/Jl ol3J70

.„i™.

)

Фиг./и

Составитель А.Клюев

Техред В.Кадар Корректор М.Демчик

| Вычислительное устройство | 1979 |

|

SU885994A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Регулятор для вертикальных ветряных двигателей | 1925 |

|

SU2060A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| М., 1977, с | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| Устройство двукратного усилителя с катодными лампами | 1920 |

|

SU55A1 |

Авторы

Даты

1986-12-23—Публикация

1985-04-05—Подача