Изобретение относится к области запоминающих устройств.

Известны постоянные запоминаюш,ие устройства (ПЗУ), содержащие дешифраторы и запоминающие матрицы с магнитными или полупроводниковыми элементами, расположенными в пересечениях проводников, к которым подключены токовые формирователи и усилители считывания.

Известные ПЗУ имеют сложную структуру и недостаточно надежны.

Предложенное ПЗУ, в отличие от известных, содержит счетчик, блоки совпадения и кольцевой регистр сдвига, при этом выход счетчика соединен со вторыми входами блоков совпадения, первые входы которых подключены к выходу формирующих элементов, а кольцевой регистр сдвига подключен к проводникам запоминающей матрицы.

Это позволяет упростить устройство и повысить его надежность.

В предложенном устройстве используется запоминающая матрица, в которой роль запоминающих элементов выполняют проводниковые связи, а из устройства управления матрицей, реализующегося на маломощных логических элементах, исключены токовые формирователи и усилители считывания.

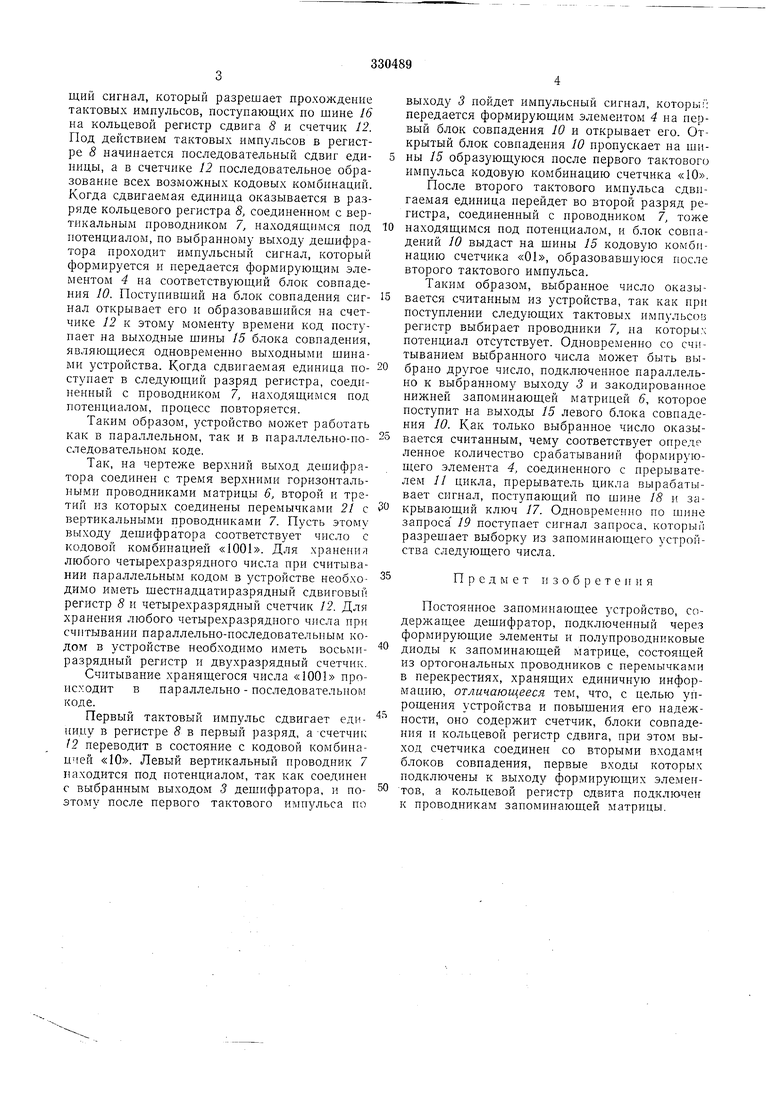

ПЗУ содержит входные шины /, соединенные с депшфратором 2, имеющим выходы 3, соединенные через формирующие элементы 4 с полупроводниковыми диодами 5, запоминающие матрицы 6, горизонтальные проводники которых подключены к диодам 5, а вертикальные проводники 7 поразрядно соединены с кольцевым регистром сдвига 8. Выходы формирующих элементов 4 соединены с первыми входами 9 блоков совпадения JO. В ПЗУ входят также прерыватель // цикла работы, соединенный с кольцевым регистром 8 и счетчиком 12, выходы 13 которого подключены ко вторым входам 14 блоков совпадения 10, имеющих выходы 15, тактовая шина 16, заведенная на ключ 17, который соединен с выходной шиной 18 прерывателя // цикла работы, шиной запроса 19, шиной разрешения 20.

Перемычки между горизонтальными и вертикальными проводниками запоминающей матрицы 6 условно показаны в виде точек 21. ПЗУ работает следующим образом. Кодовой комбинацией, поступающей по входным щинам /, с помощью дешифратора

2 выбирается необходимое число, и на соответствующем выходе 3 дешифратора появляется определенный потенциал. Этот потенциал подается на соответствующие вертикальные проводники 7 матрицы. Затем по шине разщии сигнал, который разрешает прохождение тактовых импульсов, поступающих по шине 16 на кольцевой регистр сдвига 8 и счетчик 12. Под действием тактовых импульсов в регистре 8 начинается последовательный сдвиг единицы, а в счетчике 12 носледовательное образование всех возможных кодовых комбинаций. Когда сдвигаемая единица оказывается в разряде кольцевого регистра 8, соединенном с вертикальным проводником 7, иаходяшпмся под потенциалом, по выбранному выходу дешифратора проходит импульсный сигнал, который формируется и передается формирующим элементом 4 на соответствующий блок совпадения 10. Поступивщий на блок совпадения сигнал открывает его и образовавшийся на счетчике 12 к этому моменту времени код поступает на выходные шины 15 блока совпадения, являющиеся одновременно выходными шинами устройства. Когда сдвигаемая единица поступает в следующий разряд регистра, соединенный с проводником 7, находящимся под потенциалом, процесс повторяется. Таким образом, устройство может работать как в параллельном, так и в параллельно-последовательном коде. Так, на чертеже верхний выход дешифратора соединен с тремя верхними горизонтальными проводниками матрицы 6, второй и третий из которых соединены перемычками 21 с вертикальными проводниками 7. Пусть этому выходу дешифратора соответствует число с кодовой комбинацией «1001. Для хранения любого четырехразрядного числа при считывании параллельным кодом в устройстве необходимо иметь шестиадцатиразрядпый сдвиговый регистр 8 и четырехразрядный счетчик 12. Для хранения любого четырехразрядного числа при считывании параллельно-последовательным кодом в устройстве необходпмо иметь восьмиразрядный регистр и двухразрядный счетчпк. Считывание хранящегося числа «1001 происходит в параллельно - последовательном коде. Первый тактовый импульс сдвигает едипипу в регистре 8 в первый разряд, а -счетчик 12 переводит в состояние с кодовой комбинацией «10. Левый вертикальный проводник 7 находится под потенциалом, так как соединен с выбранным выходом 3 дешифратора, и поэтому после первого тактового импульса по выходу 3 пойдет импульсный сигнал, которыГ: передается формирующим элементом 4 на нервый блок совпадения 10 и открывает его. Открытый блок совпадения 10 пропускает на шины 15 образующуюся после первого тактового импульса кодовую комбинацию счетчика «10. После второго тактового импульса сдвигаемая единица перейдет во второй разряд регистра, соединенный с проводником 7, тоже находящимся под потенциалом, и блок совпадений 10 выдаст на шины 15 кодовую комбинацию счетчика «01, образовавшуюся после второго тактового импульса. Таким образом, выбранное число оказывается считанным из устройства, так как при поступлении следующих тактовых импульсов регистр выбирает проводники 7, на которых иотеицнал отсутствует. Одновременно со считыванием выбранного числа может быть выбрано другое число, подключенное параллельно к выбранному выходу 3 п закодированное нижней запоминающей матрицей 6, которое поступит на выходы 15 левого блока совпадения 10. Как только выбранное число оказывается считанным, чему соответствует опреде ленное количество срабатываний формирующего элемента 4, соединенного с прерывателем // цикла, прерыватель цикла вырабатывает сигнал, поступающий по шине 18 и закрывающий ключ 17. Одновременно по шине запроса 19 поступает сигнал запроса, которым разрешает выборку из запоминающего устройства следующего числа. Предмет изобретения Постоянное запоминающее устройство, содержащее дешифратор, подключенный через формирующие элементы и полупроводниковые диоды к запоминающей матрице, состоящей из ортогональных проводников с перемычками в перекрестиях, хранящих единичную информацию, отличающееся тем, что, с целью унрощения устройства и новыщения его надежности, оно содержит счетчик, блоки совнадения и кольцевой регистр сдвига, ири этом выход счетчика соединен со вторыми входами блоков совпадения, первые входы которых подключены к выходу формирующих элементов, а кольцевой регистр сдвига подключен к проводникам запоминающей матрицы.

... ,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ГРУППОВЫХ КОДОВ | 1990 |

|

RU2025049C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2003 |

|

RU2239037C1 |

| Формирователь кодов для рельсовой цепи | 1990 |

|

SU1753598A1 |

| Функциональный генератор | 1987 |

|

SU1501100A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2090982C1 |

| УСТРОЙСТВО ЗАЩИТЫ ОТ ОШИБОК | 1998 |

|

RU2127943C1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

Даты

1972-01-01—Публикация