Изобретпие относится к области радиотехники, а именно, к устройствам для передачи двоичной информации по каналам связи, и может быть использовано в других областях техники.

Известно устройство для передачи двоичной информации по каналам связи, содержащее блок повышения достоверности и блок вторичного уплотнения, связанный через генератор двоичной информации с комнаратором, другой вход которого соединен с датчиком искомой комбинации а выход - через счетчик совпадений с дешифратором.

Одпако известное устройство отличается сложностью и требует большого времени для поиска искомой комбинации.

Цель изобретения сокрап1,ение вре-Мени поиска искомой комбинации при одновременном унрогцении устройства.

Достигается это тем, что выходы источников разных частот подключены ко входам схем «НЕТ, на другие входы которых подан сигнал с выходов триггера, а выходы схем «НЕТ через схему «ИЛИ подключены ко входу датчика искомой комбинации; при этом один из входов триггера нодключен непосредственно к компаратору, а другой - через схему «И, на второй вход которой подан сигнал с дешифратора, через источник совпадепий подключенного к компаратору.

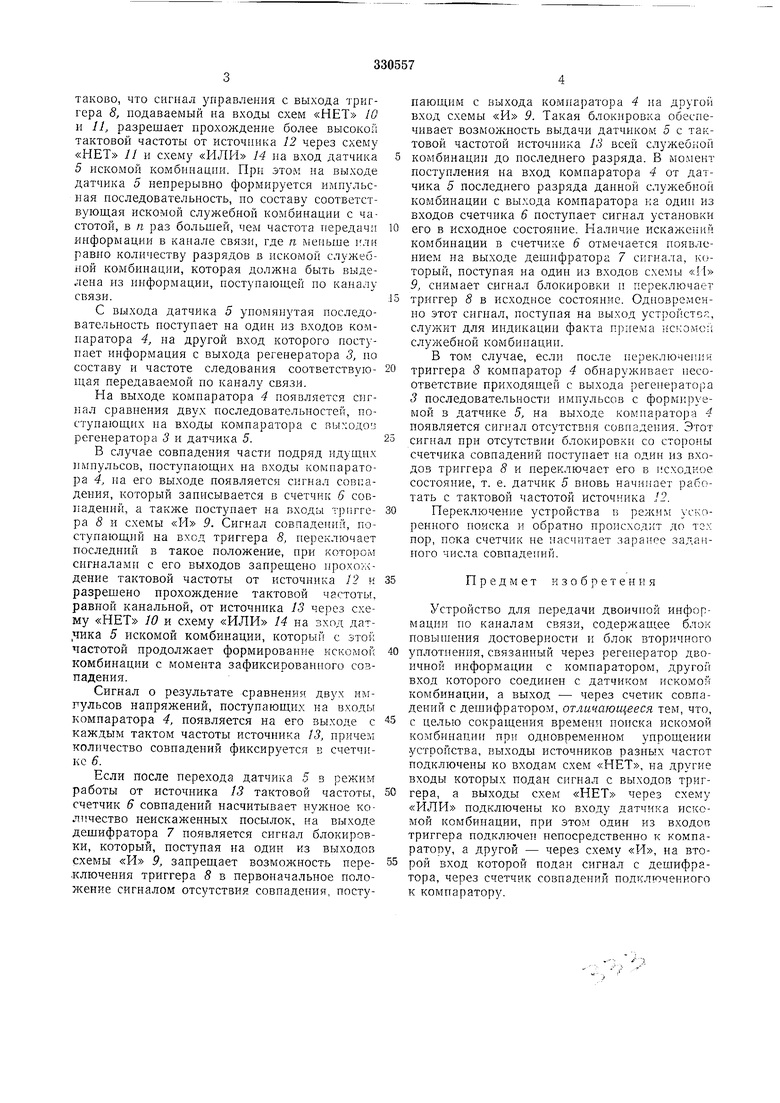

Блок-схема предлагаемого устройства приведена на чертеже.

Блок / повышения достоверностп соедппеи с блоком 2 вторпчного уплотнения и регенератором 3 двоичной информации, который в свою очередь, соединен с компаратором 4. Блок 2 вторичного уплотнения также соединен с регенератором 3. Компаратор 4 связан также с датчикол 5 искомой комбинации и счетчиком 6 совпадений, который, в свою оче-; редь, соединен с дешифратором 7.

Входы триггера 8 соединены с одним из выходов компаратора 4 и выходом схемы «И 9, входы которой соединены с выходами компаратора 4 и дешифратора 7. Выходы триггера 8 соединены с первымп входамп схем «НЕТ 10 и 11, па другие входы которых подключены выходы источников 12 и 13 разных тактовых частот.

Выходы схем «НЕТ 10 и 11 через схему 14 «ИЛ1Т подсоединены ко входу датчика 5 искомой комбинации.

Информационная последовательность импульсов совместно с комбинацией циклового фазирования поступает на вход блока 2 вторичного уилотнения, с выхода которого эта последовательность поступает параллельно на входы блока / повышения достоверности и регенератора 3 двоичной информации.

таково, что сигнал управления с выхода триггера 8, подаваемый на входы схем «НЕТ 10 и 11, разрешает прохождение более высокой тактовой частоты от источника 12 через схему «НЕТ // и схему «ИЛИ 14 на вход датчика 5 искомой комбинации. При этом на выходе датчика 5 непрерывно формируется импульсная последовательность, по составу соответствующая искомой служебной комбинации с частотой, в п раз большей, чем частота передачи информации в канале связи, где п меньше или равно количеству разрядов в искомой служебной комбинации, которая должна быть выделена из информации, поступающей по каналу связи.

С выхода датчика 5 упомянутая последовательность поступает на один из входов компаратора 4, на другой вход которого поступает информация с выхода регенератора 3, по составу и частоте следоваиия соответствующая перелТ,аваемой по каналу связи.

На выходе компаратора 4 появляется сигнал сравнения двух последовательностей, поступающих на входы компаратора с выходо; регенератора 3 и датчика 5.

В случае совпадения части подряд идущих имиульсов, поступающих на входы компаратора 4, па его выходе появляется сигнал совпадения, который записывается в счетчик 6 совпадений, а также поступает па входы триггера 5 и схемы «И 9. Сигнал совпадеипй, поступающий на вход триггера 8, переключает последний в такое положение, при котором сигналами с его выходов запрещено ирохождение тактовой частоты от источника 12 и разрешено прохонадение тактовой частоты, равной канальной, от источника 13 через схему «НЕТ 10 и схему «ИЛИ 14 на вход датчика 5 искомой комбинации, который с зтой частотой продолжает формирование кскомой комбинации с момента зафиксированного совпадения.

Сигнал о результате сравнени.ч двух импульсов напряжений, поступающих на входы компаратора 4, появляется на его выходе с каждым тактом частоты источника 13, причем количество совпадений фиксируется в счетчике 6.

Если после перехода датчика 5 в режим работы от источника 13 тактовой частоты, счетчик 6 совпадений насчитывает нулсное колт чество неискаженных посылок, на выходе дешифратора 7 появляется сигнал блокировки, который, поступая на один из выходов схемы «И 9, запрещает возможность пере.ключения триггера 8 в первоначальное положение сигналом отсутствия совпадения, поступающпм с выхода компаратора 4 на другой вход схемы «И 9. Такая блокировка обеспечивает возможность выдачи датчиком 5 с тактовой частотой источника 13 всей служебной комбинации до последпего разряда. В момент поступления на вход компаратора 4 от датчика 5 последнего разряда данной служебной комбинации с выхода компаратора ка один из входов счетчика 6 поступает сигнал установки его в исходное состояние. Наличие искажений комбинации в счетчике 6 отмечается появлепием на выходе дешифратора 7 сигнала, который, поступая на одии из входов схемы «И 9, снимает сигнал блокировки и переключает триггер 8 в исходное состояние. Одновременно этот сигнал, постуиая иа выход устройств, служит для индикации факта приема искомо;-; служебной комбинации.

В том случае, если после переключении триггера 5 рсомпаратор 4 обпаруживает песоответствие прр1ходящей с выхода регенератора 3 последовательности импульсов с формируемой в датчике 5, на выходе компаратора 4 появляется сигнал отсутствия совпадепия. Этот сигнал при отсутствии блокировки со стороны счетчика совпадений поступает па один из входов триггера 8 и переключает его в исходное состояние, т. е. датчик 5 вновь начинает работать с тактовой частотой источника 12.

Переключение устройства в режим ускоренного поиска и обратно происходит до тех пор, пока счетчик не насчитает заранее заданного числа совпаде гий.

Предмет изобретения

Устройство для передачи двоичной информации по каналам связи, содержащее блок повьпиения достоверности и блок вторичного уплотнепия,связанный через регенератор двоичиой информации с компаратором, другой вход которого соединен с датчиком искомой комбинации, а выход - через счетик совпадений с дешифратором, отличающееся тем, что, с целью сокращения времени попска искомой комбинации при одновременном упрощении устройства, выходы источников разиых частот подключены ко входам схем «НЕТ, па другие входы которых подан сигнал с выходов триггера, а выходы схем «НЕТ через схему «ИЛИ подключены ко входу датчика искомой комбинации, при этом один из входов триггера подключен непосредствеппо к компаратору, а другой - через схему «И, на второй вход которой подан сигнал с дешифратора, через счетчик совпадений подключенного к компаратору.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ОБОРОТОВ | 1971 |

|

SU296138A1 |

| Устройство для обнаружения поврежденного участка телеграфного тракта | 1981 |

|

SU1042194A2 |

| Стартстопный демодулятор | 1986 |

|

SU1363516A1 |

| Преобразователь угла поворота вала в код | 1984 |

|

SU1233282A1 |

| Система передачи дискретной информации | 1981 |

|

SU978374A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| УСТРОЙСТВО для ОПРЕДЕЛЕНИЯ ДОСТОВЕРНОСТИ ИНФОРМАЦИИ, ПЕРЕДАВАЕМОЙ ЦИКЛИЧЕСКИМ КОДоМ | 1971 |

|

SU316204A1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР | 2010 |

|

RU2428785C1 |

| Устройство для приема сигналов относительной фазовой телеграфии | 1983 |

|

SU1138954A1 |

Даты

1972-01-01—Публикация