входом третьего триггера коррекции, выход второго TpHrrepia памяти соединен с другим входом первого элемента И, выход которого соединен с третьим входом второго мультиплексора и вторым входом первого мультиплексора, выход первого триггера коррекции соединен с другим входом первого сумматора по модулю два, причем второй вход второго элемента И является первым входом блока .коррекции ошибочных символов, вторым входом которого являются объединенные вторые входы второго и четвертого триггеров коррекции и элемента ИЛИ, третий вход первого элемента И является третьим входом блока коррекции ошибочных символов, четвертым входом которого является другой вход второго сумматора по модулю два, объединенные первые входы первого и второго триггеров памяти являются пятым входом блока коррекции ошибочных символов, шестым, седьмым и восьмым :входами которого являются соответственно вторые входы второго и первого триггеров памяти и третий вход первого мультиплексора, выход четвертого триггера коррекции является вторым выходом устройства.

2. Устройство по.п. 1, отличающееся тем, что блок сравнения состоит из блоки дискретизации выход которого соединен с первым входом аналого-цифрового преобразователя, выход которого соединен с первыми входами блока памяти и элемента сравнения, второй вход которого соединен с выходом блока памяти, причем выходы элемента сравнения являются выходами блока сравнения, третьим входом которого является первый вход блока дискретизации, второй вход которого объединен с вторым входом аналого-цифрового преобразователя и является первым входом блока сравнения, входом которого является второй вход блока памяти, .

. 3. Устройство по п. 1,- о т л. и чающееся тем, -что блок управления состоит из последов-ательно соединенных счетчика управления и формирователя импульсных -последовательностей, выходы которого являются входами блока управления, первым и вторым входами которого являются первый и второй входы счетчика управления ,

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПРИЕМА СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ В УСТРОЙСТВАХ ПРИЕМА СИГНАЛОВ С ФАЗОВОЙ МАНИПУЛЯЦИЕЙ | 2020 |

|

RU2747777C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ С ПОВЫШЕННОЙ ПОМЕХОУСТОЙЧИВОСТЬЮ | 2020 |

|

RU2752003C1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ОШИБОК В КАНАЛЕ | 2001 |

|

RU2192038C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| Устройство декодирования с исправлением ошибок | 1985 |

|

SU1293855A1 |

| Устройство цикловой синхронизации | 1984 |

|

SU1197122A1 |

1. УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ ТЕЛЕГРАФИИ, с.рдержащее последовательно соединенные когерентный детектор, регенератор и кодопреобразователь, другой вход которого соединен с выходом блока выделения тактовой частоты, один вход которого соединен с другим выходом когерентного детектора, другой вход которого и другой вход блока выделения тактовой частоты объединены и являются входом устройства, а также блок сравнения и блок управления, причем, выход кодопреобразователя является первым выходом устройства, о т л .и ч а ющ е е с я тем, что, с целью повышения помехоустойчивости, в него введены блок выделения синхросигнала, блок задержки и блок коррекции ошибочных символов, причем выход блока вьделения тактовой частоты соединен с первым входом блока сравнения, другим входом регенератора, первым входом блока коррекции ошибочных символов и входом блока задержки, выход которого соединен с вторым входом блока коррекции ошибочных символов и первыми входами блока вьщеления синхросигнала и блока управления, вторые входы которых соединены соответственно с .выходами кодопреобразователя и блока вьщеления синхросигнала, четыре выхода блока управления соединены соответственно с третьим, четвертым и пятым входами блока коррекции оши.бочных символов и вторым входом блока сравнения, два выхода которого соединены соответственно с шестым и седьмым входами блока коррекции ошибочных символов, восьмой вход которого соединен с выходом кодопреобразователя, третий вход блока сравнения соединен с выходом когерентного детектора, при этом блок коррекции ошибочных символов состоит из последовательно соединенных первого триггера памяти, лервого сумматора по модулю два, первого мультиплексора, первого триггера коррекции, второго триггера коррекции, второго сумматора по модулю два, СС первого и второго элементов И и эо со сд элемента ИЛИ, выход которого соедицен с другим входом первого триггера )соррекции, и первым входом третьего триггера коррекции, выход которого соединен с одними входами третьего сумматора по модулю два и четвертого триггера коррекции, выход первого триггера памяти соединен с другим входом третьего сумматора по модулю два, выход которого соединен с первым входом второго мультиплексора, второй вход которого соединен с выходом второго триггера коррекции, выход второго мультиплексора соединен с ВТОРЫМ

Изобретение относится к электросвязи и может использоваться для приема двоичных данных методом относительной фазовой телеграфии.

Известно устройство для приема сигналов с относительной фазовой модуляцией, содержащее последовательно соединенные формирователь опорного когерентного напряжения, фазовый манипулятор, фазовьй детектор, другой вход которого соединен с ВХОДОМ формирователя опорного когерентного напряжения, регенератор и кодопреобразователь, другие входы регенератора и кодопреобразователя соединены с выходом блока вьиеления тактовой частоты ij .

Однако такое устройство характеризуется недостаточной надежностью.

Наиболее близким к предлагаемому является устройство для приема сигналов относительной фазовой телеграфии, содержащее последовательно соединенные когерентный детектор, регенератор и кодопреобразователь, другой вход которого соединен с выходом блока вьщеления тактовой частоты, один вход которого соединен с другим выходом когерентного детектора , другой вход которого и другой вход блока вьщеления тактовой частот объединены и являются входом устройства, а также блок сравнения и блок управления, причем выход кодопреобразователя является перв1Л4 вых.одом устройства z .

Однако известное устройство обладает недостаточной помехоустойчивостью.

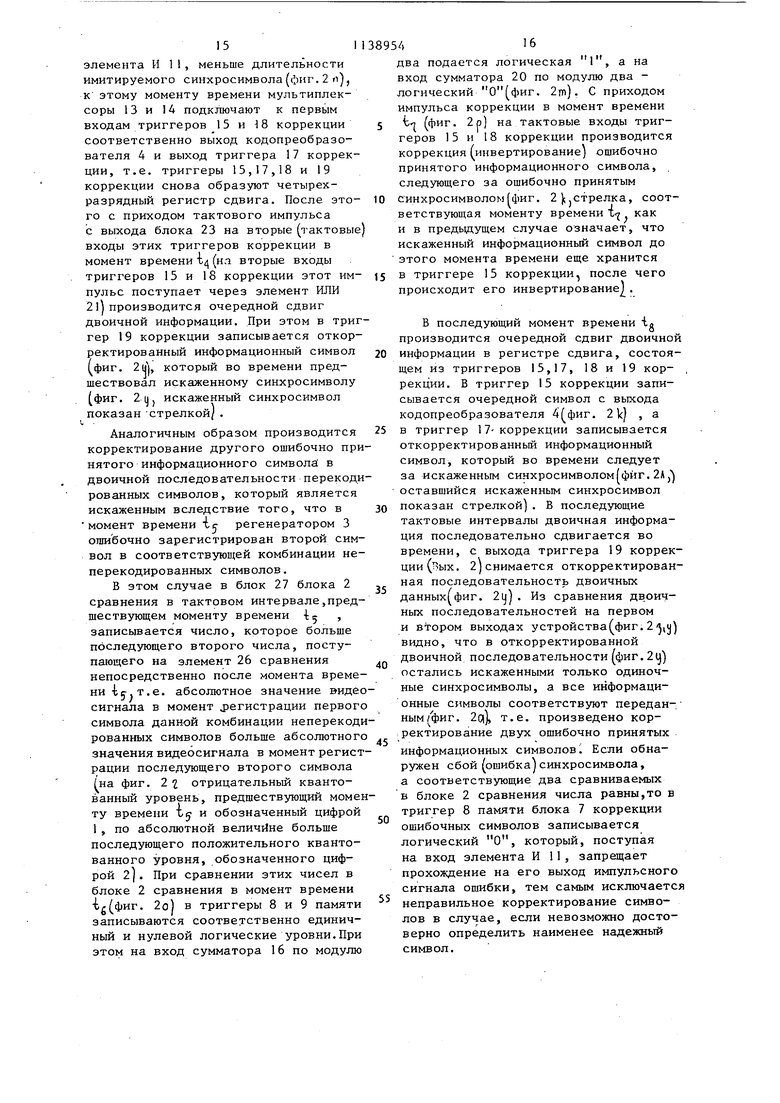

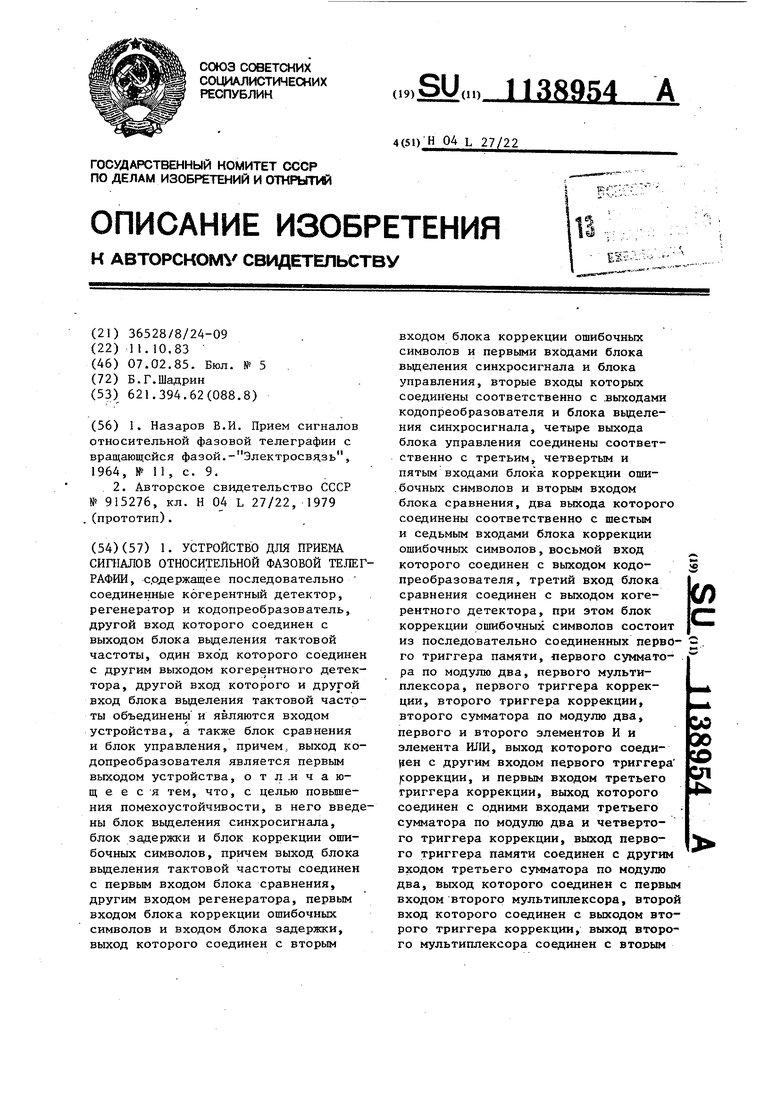

Цель изобретения - повьшение помехустойчивости. Указанная цель достигается тем, что в устройство для приема сигналов относительной фазовой телеграфии, содержащее последовательно соединен ные когерентный детектор, регенератор и кодопреобразователь, другой вход которого соединен с выходом блока выделения тактовой частоты, один вход которого соединен с другим выходом когерентного детектора, дру гой вход которого и другой вход бло вьщеления тактовой частоты объедине ны и являются входом устройства, а также блокСравнения и блок управле ния, причем выход кодопреобразовате является первым выходом устройства, введены блок выделения синхросигнала блок задержки и блок коррекции ошибочных символов, причем выход блока выделения тактовой частоты соединен с первым входом блока сравнения, другим входом регенератора, первым входом блока коррекции ошибочных символов и входом блока задержки, выход которого соединен с вторым входом блока коррекции ошибочных символов и первыми входами блока выделения синхросигнала и блока управления, вторые входы которых соединены соответственно с выходами кодо преобразователя и блока выделения синхросигнала, четыре выхода блока управления соединены соответственно с третьим, четвертым и пятым входами блока коррекции ошибочных символов и вторым входом блока сравнения, два выхода которого соединены соответственно с шестым и седьмым входами блока коррекции ошибочных символ восьмой вход которого соединен с выходом кодопреобразователя, третий вход блока сравнения соединен с выходом когерентного детектора, при этом блок коррекции ошибочных символов из последовательно соединенных первого триггера памяти, первого сумматора по модулю два, первого мультиплексора, первого триггера коррекции, второго триггера коррекции второго сумматора по модулю два, пер вого и второго элементов И и элемента ИЛИ, выход которого соединен с др гим входом первого триггера коррекции и первым входом третьего триггера коррекции, выход которого соединен с одними зходами третьего сумматора по модулю два и четвертого триг гера коррекции, выход первого триггера памяти соединен с другим входом третьего сумматора по модулю два, выход которого соединен с первым входом второго мультиплексора, второй вход которого соединен с выходом второго триггера коррекции, выход второго мультиплексора соединен с вторым входом третьего триггера коррекции, выход второго триггера памяти соединен с другим входом первого элемента И, выход которого соединен с третьим входом второго мультиплексора и вторым входом первого мультиплексора, выход первого триггера коррекции соединен с другим входом первого сумматора по модулю два, причем второй вход второго элемента И является первым входом блока коррекции ошибочных символов, вторым входом которого являются объединенные вторые входы второго и четвертого триггеров коррекции и г лемента ИЛИ, третий вход первого элемента И является третьим входом блока коррекции ошибочных символов, четвертым входом которого является другой вход второго сумматора по мoдVлю два, объединенные первые входы первого и второго триггеров памяти являются пятым входом блока коррекции ошибочных символов, шестым, седьмым и восьмым входами которого являются соответственно вторые входы второго и первого триггеров памяти и третий вход первого мультиплексора, выход четвертого триггера коррекции является вторым выходом устройства. Причем блок сравнения состоит из блока дискретизации, выход которого соединен с первым входом аналогоцифрового преобразователя, выход которого соединен с первыми входами блока памяти и элемента сравнения, второй вход которого соединен с выходом блока памяти, причем выходы элемента сравнения являются, выходами блока сравнения, третьим входом которого является первый вход блока дискретизации, второй вход которого объединен с вторым входом аналогоцифрового преобразователя и является первым входом блока сравнения,вторым входом которого является второй вход блока памяти. Кроме того, блок управления состоит из последовательно соединенных счетчика управления и формирователя импульсных последовательностей, выходы которого являются выходами $.1 блока управления, первым и вторым входами которого являются первый и второй входы счетчика управления. На фиг. 1 изображена структурная .электрическая схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие работу устройства. Устройство для приема сигналов относительной фазовой телеграфии содержит когерентный детектор 1, блок 2 сравнения, регенератор 3, кодопреобразователь 4, блок 5 выделения тактовой частоты, блок 6 управления, блок 7 коррекции ошибочных символов, состоящий из второго 8 и первого 9 триггеров памяти, второго сумматора 10 по модулю два, первого элемента И 11, второго элемента И 17, первого мультиплексора 13, второ го мультиплексора 14, первого тригге ра 15 коррекции, первого сумматора 16по модулю два, второго триггера 17коррекции, третьего триггера 18 коррекции, четвертого триггера 19 коррекции, третьего сумматора 20 по модулю два и элемента ИЛИ 21, блок 22выделения синхросигнала, блок 23задержки. Блок 2 сравнения состо,ит из блока 24 дискретизации, анало цифрового преобразователя 25,элемент 26 сравнения и блока 27 памяти. Блок 6 управления состоит из счетчика 28 управления и формирователя 29 импуль ных последовательностей. Устройство работает следующим образом. Модулированный методом относитель ной фазовой телеграфии(ОФТ)сигнал данныхfс разностью фаз между соседними посылками О или 1 BGji, содержащих одиночные синхросимволы заданной час тоты следования, поступает на когерентный детектор 1 и блок 5 выделения тактовой частоты. В когерентном детекторе 1 производится квазикогерентное детектирование входного сигнала, т.е. операция перемножения входного сигнала на сформированное опорное когерентное напряжение с последующей фильтрацией результата перемножения фильтром нижних частот Опорное когерентное напряжение в ког рентном детекторе 1 может быть сформировано из входного сигнала любым известным методом. Таким образом, когерентный детектор 1 может состоять из формировател когерентного напряжения и фазового 4 детектора, представляющего собой последовательно соединенные переМножитель и фильтр нижних частот. Когерентноеопорное напряжение подается на вход блока выделения тактовой частоты. Продетектированный сигнал с первого выхода когерентного детектора 1, представляющий собой видеосигнал с нулевым средним уровнем так как положительные и отрицательные посылки симметричны относительно нулевого уровня при отсутствии напряжения помех на входе когерентного детектора 1), поступает на вход регенератора 3 и на третий вход блока 2 сравнения. В регенераторе 3 производится регистрация символов в отсчетные мо {снты времени, задаваемые, блоком 5 вьщеления тактовой частоты, т.е. если в момент прихода тактового импульса выходное напряжение когерентного детектора 1 положительное, то регенератором 3 регистрируется единичный символ, если же в этот момент напряжение когерентного детектора 1 отрицательное, то регистрируется нулевой символ. Блок 5 вьщеления тактовой частоты формирует узкие тактовые импульсы, соответствующие во времени наименее искаженной части продетектированных посылок (обычно середине посылок . Конструктивно блок 5 вьщеления тактовой частоты может быть выполнен, например, из входного преобразователя содержащего собственные керреляторы, работающие с временным сдвигом один относительно другого, и замкнутого устройства синхронизации. При этом результат сравнения выходных сигналов корреляторов используется для подборки фазы автогенератора замкнутого устройства синхронизации. С выхода регенератора 3 двоичные символы подаются на кодопреобразователь 4, где производится их перекодирование с целью снятия относительности, вводимой в двоичную последовательность символов на передающей стороне. Для наглядности(фиг. 2а) представлена исходная последовательность двоичных данных, содержащих единичные синхросимволы заданной частоты следования (синхросимволы V показаны штриховыми линиями}.Здесь каждая кодовая комбинация состоит из пяти информационных символов и одного избыточного единичного синхросимвола, т.е. период повторения синхросимволов в общем потоке двоичных данных составляет двоичных элементов. На фиг. . изображена та же последовательность двоичных данных, но только после относительного перекодирования символов, необходимого для передачи информации методом ОФТ. Этой последовательностью символов производится модуляция по фазе (О18оР)несущего колебания на передающей стороне. На фиг. 2 изображен видеосигнал на выходе когерентного детектора 1 (нулевое среднее значение обозначено прямой линией), а на фиг. 2й представлены тактовые импульсы блока 5 выделения тактовой частоты, в моменты следования которых производится регистрация символов регенератором 3 (фиг. 2е. В кодопреобразователе 4 двоичная последовательность с выхода регенератора 3 сдвигается на один тактовый интервал (фиг. 2 .) , после чего символы обеих последовательностей сравниваются между собой(например, .в сум маторе по модулю два с инверсным выходом), в результате с выхода кодо -преобразователя 4 снимается восстановленный двбичный сигнал (фиг. 2 правильно принятые синхросимволы обозна чены штриховыми линиями, а искаженные символы - стрелками). С выхода кодопреобразователя 4 двоичная последовательность подаетс на второй вход мультиплексора 13 блока 7 коррекции ошибочных символо и на вход блока 22 вьщеления синхро сигнала, который производит определение временного положения синхросигнала в принимае 1ом двоичном пото ке и формирует синхронизирующие импульсы. t. Конструктивно блок 22 вьщеления синхросигнала может состоять, напри мер , из дешифратора синхросигнала, набора счетчиков, подсчитьтающих отклики дешифратора от каждой позиц цикла цикл - совокупность последовательных символов двоичного сигнал через которые повторяется синхросиг нал в течение заданного промежутка времени, и решающей схемы, определя щей номер счетчика, в который.посту пило наибольшее число откликов деши ратора, и формирующей синхроимпульс во времени, соответствующий той поз ции цикла, от которой поступило большее число откликов дешифратора. Выходными синхроимпульсами блока 2 производится фазирование счетчика 28. Коэффициент V . счета счетчика 28равен числу символов в одном цикле принимаемой двоичной последователь- ности, в данном случае(фиг. 2о). Выход счетчика 28, представляющий собой -группу разрядных выходов этого счетчика, подключен к входу формирователя 29, который формирует периодические последовательности импулъсоЪ, управляющие работой блока 2 . сравнения и блока 7 коррекции ошибочных символов. Выходы формирователя 29являются выходами блока 6 управления. Импульсные последовательности с соответствующих выходов блоков 6 управления представляют собой периодические последовательности одиночных импульсов, частота следования которых равна частоте следования синхросимволов в принимаемом двоичном сигнале. Формирователь 29 импульсных последовательностей может быть выполнен, например, на основе дешифратора и формирующего элемента, обеспечиваюшего уменьшение длительности импульсов одной из последовательностейимпульсов, формируемых с помощью дешифратора. В блоке 2 сравнения поступающий видеосигнал подается на первый вход блока 24, в котором производится запоминание мгновенных значений видеосигнала в моменты регистрации символов регенератором 3(фиг. 2Z , среднее нулевое значение квантованных уровней также обозначено прямой линией). Запоминание мгновенных значений уровней видеосигиала необходимо для надежного срабатывания в отсчетные моменты времени аналогоцифрового преобразователя 25. Блок 24может быть выполнен, например, в виде электронного ключа и интегрирующей RC -цепи, запоминающей отсчетные значения мгновенных уровней. Аналого-цифровой преобразователь 25в момент прихода каждого тактового импульса с блока 5 производит преобразование соответствующего абсолютного значения уровня блока 24 (фиг. 2-2) в цифровую форму в виде кодового числа в прямом коде и запоминание этого числа до прихода следу ющего тактового импульса. Таким образом, кодовые числа на зыходе аналого-цифрового преобразова теля 25 представляют собой абсолютные значения уровней когерентного детектора цифровой форме в момен ты регистрации символов регенератором 3, Далее кодовые числа с выхода анало го-цифрового преобразователя 25 последовательно /с частотой следования тактовых импульсов) подаются в параллельном прямом коде на первые входы элемента 26 сравнения и блока 27, выход которого (группа разрядных выходов} подключен к второму входу элемента 26 сравнения. Передним фронтом каждого импульса последовательности с выхода блока 6 управления (фиг. 2ц) производится периодическая перезапись в блок 27 того кодового числа аналого-цифрового преобразователя 25, которое соответствует абсолютному значению уровн К9герентного детектора 1 в момент регистрации регенератором 3 каждого первого символа первым символом условно считается тот из символов в каждой кодовой комбинации неперекодированных символов на выходе регеренатора 3, который во времени предшествует соответствующему синхро символу на выходе кодопреобразовате,ля 4. На фиг 2е,г : цифрой 1 обозначены соответственно каждый первый регистрируемый символ и соответствую щий егму уровень когерентного детектора I, зафиксированный блоком 24, абсолютное значение которого в цифро вом коде записывается в блок 27, а цифрой . 2 обозначены соответственно каждый второй регистрируемый символ и соответствующий ему уровень когерентного детектора 1, зафиксированный блоком 24. Каждое записьшаемое в блоке 27 кодовое число сохраняется в нем до прихода следующего импульса посл.едовательности с выхода блока 6 управлени Сфиг, 2h , Блок 22 и блок 6 управления такт тируются импульсной последовательностью с выхода блока 23(фиг. 2tt) , который обеспечивает задержку импуль сов с выхода блока 5 вьщеления такто вой частоты(фиг. 2) на время, превышающее интервал времени, необходимый для преобразования аналого-цифровым преобразователем 25 аналогового уровня в цифровой код. При этом передние фронты управляющих импульсов (фиг. 2 н) , поступающих на блок 27, запаздывают во времени относительно моментов появления преобразованных кодовых чисел на выходе аналогоцифрового преобразователя 25, чем обеспечивается надежная перезапись кодовых чисел в блок 27. Каждое первое записанное в блоке 27 кодовое число, соответствующее первому регистрируемому символу, сразу же подается с его выхода на второй вход элемента 26 сравнения. С приходом последующего тактового импульса с выхода блока 5 выделения тактовой частоты (фиг. 2) на выходе аналого-цифрового преобразователя 25 появится второе кодовое число, соответствующее второму регистрируемому регенератором 3 символу, во времени совпадающему с соответствующим синхросимволом на выходе кодопреобразователр 4. В элементе 26 сравнения в этом случае сравниваются между собой первое кодовое число, записанное в блоке 27, и последующее второе кодовое число с выхода аналого-цифрового преобразователя 25; В момент прихода импульса последовательности с второго выхода блока 6 управления фиг. 2о) результат сравнения двух чисел в виде логических уровней с выходов блока 2 сравнения записывается в соответствующие триггеры 8 и 9 памяти блока 7. В блоке 7 коррекции ощибочных символов сигнал двоичных данных с выхода кодопреобразователя 4 подается через мультиплексор 13 на триггер 15 коррекции. Триггеры 15,17,18 и 19 коррекции соединены между собой последовательно(выход второго триггера 17 соединен с первым входом последующего триггера 18 через второй мультиплексор 14)и образуют четырехразрядный регистр сдвига. При эт.м неискаженные синхросимволы в двоичной последовательности, поступающей на вход сумматора 10 по модулю два с выхода триггера 17 коррекции, во времени и по значениям-совпадают с имитируемыми синхросимволами, оступающими на второй вход этого сумматора с третьего выхода блока 6 управления. Совпадение во времени принимаемых и имитируемых синхросимволов обеспечивается соответствующим 11 1 фазированием блока 6 управления блоков 22 выделения синхросигнала. Таким образом, в сумматоре 10 ко модулю два производится сравнение имитируемых синхросимволов с принимаемыми синхросимволами. При этом, если какой-либо синхросимвол в прин маемой двоичной последовательности не совпадает с соответствующим имитируемым синхросимволом, т.е. имеет место сбой (ошибка принимаемого синхросимвола, то производится коррекция (инвертирование либо символа, предшествующего искаженному синхросимволу(инвертируется двоичный символ, записанный в триггер 18 коррек ции, либо символа следующего за искаженным синхросимволом(инвертиру ется двоичный символ, записанный в триггер 15 коррекции). Коррекция того или иного символа производится в зависимости от результата сравнения в блоке 2 сравнения абсолютных значений уровней когерентного детек тора 1. Рассмотрим более подробно процес корректирования ошибочных символов в принимаемой поЛедовательности двоичных данных. Если бы отсутствовали искажения принимаемого сигнала, то видеосигна на выходе когерентного детектора 1 по форме соответствовал бы модулиру ющей двоичной последовательности на передающей стороне(фиг. 2S) , соответственно полностью совпадала бы с модулирующей последовательностью и последовательность регистрируемых (регенерируемьи символов на выходе регенератора 3 фйиду задержки в кан ле связи видеосигнал, на фиг. 2t изображен несколько смещенным во времени относительно модулирующего сигнала показанного на фиг. 2S) . Однако вследствие действия помех в канале в один из моментов регистрации очередного символа t) видеосигнал вместо положительного принимает отрицательное значение (фиг. 2|)) , т.е. в этот момент времени напряжение помехи на входе устройства действует противофазно по отношению к напряжению сигнала, а фаза резул1)Тирующего колебания принимает такое значение по отношен к опорному колебанию когерентного детектора 1, при котором полярность выходного напряжения когерентного детектора 1 противоположна по отно42шению к тому, если бы на вход устройства поступал только один сигнал без помех. Таким образом в момент времени t-i имеет место ошибочная регистрация первого символа одной из шестиэлементных комбинаций неперекодированных символов (фиг. 2f)jZ, е) , т.е. вместо символа 1 принят символ О, который обозначен цифрой 1. В момент времени ty имеет место ошибочная регистрация второго символа другой шестизлейентной комбинации неперекодированных символов, т.е. вместо симг.ола О принят символ 1(фиг. 2,,Z,e) , который обозначен цифрой 2. После относительного перекодирования символов кодопреобразователем 4(фиг. 20- одиночные ошибки, имеющие место на выходе регенератора 3 (фиг. 2е) удваиваются(ошибочные символы показаны стрелками. Таким образом, если обнаружен сбой (ошибка) синхросимвола после относительного перекодирования символов, то это результат того, что ошибочно зарегистрирован регенератором 3 либо первый символ в соответствующей комбинации неперекодированных символов, либо второй символ этой комбинации. В первом случае оказывается искаженным в перекодированной двоичной последовательности кроме синхросимвола еще и предшествующий ему информационный симво:1(0иг. 2ё, , этому случаю соответствует момент времени ;,. Во втором случае искаженным становится кроме синхросимвола еще и следующий за ним информационный символ (фиг. . , момент времени tj . . При обнаружении сбоя относительного перекодирования требуется корректировать либо символ, предшествующий искаженному синхрос.имволу, либо символ, следующий за искаженньм синхросимволом. А для этого надо знать, какой из двух - имволов (первый или второй)в соответствующей кодовой комбинации неперекодированных символов ошибочно зарегистрирован регенератором 3,т.е. необходимо найти, какой из этих двух символов наименее надежный. Таким образом, чтобы определить какой из двух следующих один за другим символов(первый или второй) ошибочно зарегистрирован регенератором..3(если обнаружено, что соответствующий синхроснмвол на выходе кодо преобразователя 4 искажен- , необхрди мо сравнить абсолютные значения (СЛ когерентного детектора 1 в моменты регистрации этих символов. При этом искаженным следует -считать тот символ, которому соответствует меньшее значение(СД Так, например, после момента времени ti в блоке 27 блока 2 сравнения записывается абсолютное значение когерентного детектора 1 ( цифровом коде соответствующее первому регистрируемому символу в данной комбинации неперекодированнык символов. С приходом на первый вход элемента 26 сравнения последующего второго значения(с )в цифровом коде, соответствующего второму регис рируемому символу, на первом и втором выходах элемента 26 сравнения появятся единичные логические уровни. Это означает, что значение С,)меньше значения (Cj). На фиг. 22. показано, что значение ответствующее амплитуде отрицательно го квантованного уровня когерентного детектора 1, зафиксированного в момент времени i и обозначенного циф рой 1, меньше последующего значения (, соответствующего амплитуде поло жительного квантованного уровня, обозначенного цифрой 2. С приходом в момент времени г импульса последовательности с второго выхода блока 6 управления (фиг. 2о) единичные логические уровни с выхол хов блока 2 сравнения записываются в триггеры 8 и 9 памяти блока 7. При этом на второй вход элемента И П, подключенного к прямому выходу триггера 8 памяти, поступает единичный логический уровень, а на входы сумма торов 16 и 20, подключенных соответственно к инверсному и прямому выходам триггера 9. памяти, поступают соответственно нулевой и единичный логические уровни (на фиг. 2гппред. ставлено выходное напряжение триггера 9 памяти, поступающее на сумматор 20 по модулю два5 т.е. с прямого выхода триггера 9 памяти. В следующий тактовый интервал после момента времени, j производится очередной сдвиг двоичной информации в регистре сдвига, состоящем из триггеров 15,17, 18 и 19 коррекции. В сумматоре 10 производится сравнение принимаемото (с выхода триггера 17 коррекции имитируемого блоком 6 синхросимволов (фиг. 2л,п. При этом регистрируется ошибка, т.е. на выходе сумматора 10 по модулю два появляется логическая 1 (несовпадение, а на выходе элемента И 11 появляется одиночный импульс, длительность которого равна длительности импульса, поступающего на вход элемента И 11 с четвертого выхода блока 6 управления. Этот импульсный сигнал ошибки подается на управляющие входы мультиплексоров 13 и 14, которые в этом случае подключают к сигнальным входам триггеров 15 и 18 коррекции выходы соответствующих сумматоров 16 и 20. В результате на вход триггера 15 коррекции поступает его выходной логический уровень (так как на второй вход второго сумматора 16 по модулю два подается логиче-ский 0 с инверсного выхода триггера 9 памяти и сумматор не инвертирует логический уровень, поступающий на первый его вход|, а на вход триггера 18 оррекции поступает его противоположный логический уровень (так как на второй вход сумматора 20 подается логическая Г и сумматор инвертирует логичес- кий уровень, поступающий на первьй его вход) . Одновременно сигнал ошибки поступает на вход элемента И 12, разрешая тем самым прохождение на его выход одного импульса коррекции Б момент времени г (фиг. 2р), выделяемого из последовательности тактовых импудьсов с выхода блока 5 выделения тактовой частоты. Этот импульс, проходя через элемент ИЛИ 21, поступает на тактовые входы триггеров 15 и 18 коррекции(фиг. 2cj момент времени , обеспечивая перезапись логических уровней (симвблов этих триггеров. При этом состояние триггера 15 коррекции не изменяется (фиг. 2); , а в триггер 18 коррекции записывается его противоположный выходной логический уровень (фиг. 2 стрелка, соответствующая моменту времени -1-. означает, что искаженный символ до этого момента времени еще хранится в триггере 18 коррекции, после чего происходит его инвертирование) . К следующему моменту времени т (фиг. 2h)на входы мультиплексоров 13 и 14 поступает нулевой логический уровень, поскольку длительность импульса, поступающего с четвертого выхода блока 6 управления на вход

15I

элемента И 11, меньше длительности имитируемого синхросимвола(фиг.2 о), К этому моменту времени мультиплексоры 13 и 14 подключают к первым входам триггеров 15 и 8 коррекции соответственно выход кодопреобразователя 4 и выход триггера 17 коррекции, т.е. триггеры 15,17,18 и 19 коррекции снова образуют четырехразрядный регистр сдвига. После этого с приходом тактового импульса с выхода блока 23 на вторые (тактовые входы этих триггеров коррекции в момент времени i (н.1 вторые входы триггеров 15 и 18 коррекции этот импульс поступает через элемент ИЛИ 2l производится очередной сдвиг двоичной информации. При этом в триггер 19 коррекции записывается откорректированный информационный символ фиг. 2lj|, который во времени предшествовал искаженному синхросимволу фиг. 2 уJ искаженный синхросимвол показан стрелкой/.

Аналогичным образом производится корректирование другого ошибочно цринятого информационного символам в двоичной последовательности перек:одированных символов, который является искаженным вследствие того, что в момент времени ic регенератором 3 ошибочно зарегистрирован второй символ в соответствующей комбинации неперекодированных символов.

В этом случае в блок 27 блока 2 сравнения в тактовом интервале,предшествующем моменту времени { , записывается число, которое больше последующего второго числа, поступающего на элемент 26 сравнения непосредственно после момента времени -tj-.T.e. абсолютное значение видеосигнала в момент регистрации первого символа данной комбинации неперекодированных символов больше абсолютного значения видеосигнала в момент регистрации последующего второго символа на фиг. 2 2 отрицательный квантованный уровень, предшествующий моменту времени tj и обозначенный цифрой 1, по абсолютной величине больше последующего положительного квантованного уровня, обозначенного цифрой 2. При сравнении этих чисел в блоке 2 сравнения в момент времени . 2о) в триггеры 8 и 9 памяти записываются соответственно единичный и нулевой логические уровни.При этом на вход сумматора 16 по модулю

3895416

два подается логическая 1, а на вход сумматора 20 по модулю два логический . 2гп). С приходом импульса коррекции в момент времени

5 t7 (фиг. 2р на тактовые входы триггеров 15 и 18 коррекции производится коррекция (инвертирование) ошибочно принятого информационного символа, следующего за ошибочно принятым

10 синхросимволом(фиг. 2)(.стрелка, соответствующая моменту времени 1,. как и в предыдущем случае означает, что искаженный информационный символ до этого момента времени еще хранится

J5 в триггере 15 коррекции, после чего происходит его инвертирование.

В последующий момент времени i« производится очередной сдвиг двоичной информации в регистре сдвига, состоящем из триггеров 15,17, 18 и 19 коррекции. В триггер 15 коррекции записывается очередной символ с выхода кодопреобразователя 4(фиг. 2k) , а в триггер 17- коррекции записывается откорректированный информационный символ, который во времени следует за искаженным синхросимволом фйг. 2А j оставшийся искаженным синхросимвол показан стрелкой). В последующие тактовые интервалы двоичная информация последовательно сдвигается во времени, с выхода триггера 19 коррекции (ых. 2)снимается откорректированная последовательность двоичных данных фиг. 2Lj) . Из сравнения дв.оичных последовательностей на первом и втором выходах устройства(фиг. 2jijj) видно, что в откорректированной двоичной последовательности (фиг.2у) остались искаженными только одиночные синхросимволы, а все информационные символы соответствуют передан-/ ным/фиг. 2о|), т.е. произведено корректирование двух ошибочно принятых информационных символов. Если обнаружен сбой (ошибка синхросимвола, а соответствующие два сравниваемых в блоке 2 сравнения числа равны,то в триггер 8 памяти блока 7 коррекции ошибочных символов записывается логический О, который, поступая на вход элемента И 11, запрещает прохождение на его выход импульсного сигнала ошибки, тем самым исключается неправильное корректирование символов в случае, если невозможно достоверно определить наименее надежный символ.

Если же принимаемый сигнал двоичных данных не содержит избыточных одиночных синхросимволов заданной частоты следования, то двоичная информация снимается как и в любом другом известном устройстве для приема сигналов ОФТ с выхода кодопреобразователя 4 (Вых l).

Таким образом, в предлагаемом устройстве повышена помехоустойчивость.

г

-г-г

ZL

вх

JiL

24

JET

26

27

28

29

9

22f

i:

8ш2

19

Фиг.1

-MJL rnJl ri rLrL.

ti

I I I I I jl I III M I I I I 1 I I I Ml I I I I I I

рм. т III p nw f-ч r-чn rЮЦ

м гi|j-и-1ЖЛ1 л ||г т и

j-Ly-TrLRj-LTul T- L

ПП ji ПП jl П

n

Пnl| Пni| FL

I П г I m/ I П r I I П II I

illII II

I II I I I I I III I I I I I I I I J I III I I I I I 1 I

II IIII

I11

IIll

Фия.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Назаров В.И | |||

| Прием сигналов относительной фазовой телеграфии с вращающейся фазой.- Электросвязь, 1964, № 11, с | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР № 915276, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-02-07—Публикация

1983-10-11—Подача