Устройство может быть использо1вано в арифметических устройствах электронных вычислительных машин.

Известны устройства для сложения-вычитания десятичных чисел, выполненные на сумматоре с разбиением его на тетради, сложение S которых выполняется в два этапа: на первом этапе определяются нескорректированные коды групповых сумм и на основании наличия межгрупповых переносов и значений нескорректированных групповых суммкоды их корректировки, а на втором этапе получают скорректированную сумму как результат сложения полученных кодов групповых сумм и корректировок.

Предлагаемое устройство позволяет просто и с наименьшей затратой оборудования и времени решить проблему получения обратного кода десятичного числа и применить новый способ коррекции, упрош,аюш,ий и ускоряюш;ий алгоритм десятичного сложения.

В рассматриваемом устройстве предлагается перед исполнением операции сложения (вычитания) двух десятичных чисел исключить непосредственный перевод отрицательного десятичного числа в обратный код. Вместо обратного кода отрицательного числа берется его инверсия (поразрядное дополнение до 15): -Д 15 -Д (9 -Д) +6, т. е. число будет участвовать в операции с избытком 6.

В этом случае десятичный перенос легко осуществляется с помощью переноса из самого старшего разряда двоичного представления десятичного разряда, т. е. операция

сложения над числами производится целиком по правилам двоичной арифметики. Коррекция положительного результата (прямой код) в десятичных разрядах, где возник перенос, происходит автоматически (вместо «10

переносится «16, т. е. исключаются шесть избыточных единиц); из десятичных 1разрядов, где не возник перенос, необходимо вычесть избыточные шесть единиц.

Вычитание шести (ОНО) заменяется прибавлением десяти (1010) по модулю шестнадцать (игнорируется единица переноса в соседний старший разряд).

Если результат получился отрицательный, его нобходимо ороинвертировать. Перед инвертированием (результата в тех разрядах, где возник перенос, необходимо произвести коррекцию - прибавить шесть (ОНО), так как перенос в этом случае равносилен вычитанию «16 вместо «10. Последующее инвертирование автоматически исключает избыточные шесть единиц, которые были введены инвертированием в начале операции. Так, например, складываем (-В), где А я В - десятичные одноразрядные числа. РезульТаким образом, в этом алгоритме совмещается перевод числа в обратный код с коррекцией результата двоичного сложения.

Для чисел с одинаковыми знаками нредлагается производить операцию в прямом коде и для отрицательных чисел, чтобы избежать введения дополнительного десятичного разряда в случае оереполнения с целью сохранения верного знака результата и применения однотипной коррекции.

Коррекция в этом случае такая же, как и при операциях над положительными числами, т. е. прибавляется шесть в тех разрядах, где возник перенос или где числа -9. В этом случае перед операцией знаки гасятся, знак результата запоминается. Переполнение фиксируется знаковыми разрядами сумматора, т. е. используются цепи двоичной арифметики.

Примеры:

1. 19-88 -69(11.0110.1001) 00.0001.1001

11.1000.1000

а)инвертирование

(-88) 11.0111.0111

б)операция

00.0001.1001

11.0111.0111 11.1001.0000

в)

оно -

коррекция

11.1001.0110

г) 11.0110.1001 - инвертирование 2. - 19 -f 88 69 (00.0110.1001) 11.0001.1001

00.1000.1000

а)инвертирование (-19)- 11.1110.0110

б)операция , Ч-ШО-О О

00.1000.1000

-00.0110.1110

1

00.0110.1111

1010 - коррекция

00.0110.1001 107 (11.0001.0000.0111)

00.0001.1001 Знаки операн00.1000.1000 дов

гасятся.

00.1010.0001 знак результа0110.0110 та запоминает01.0000.0111 ся

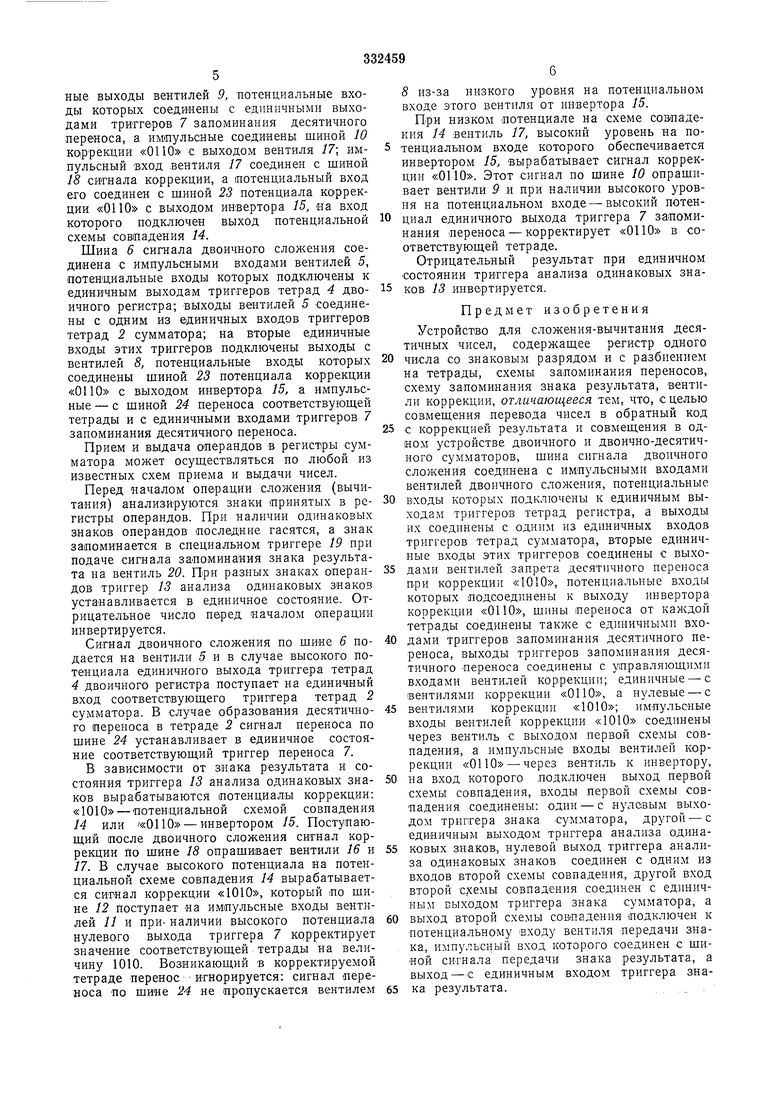

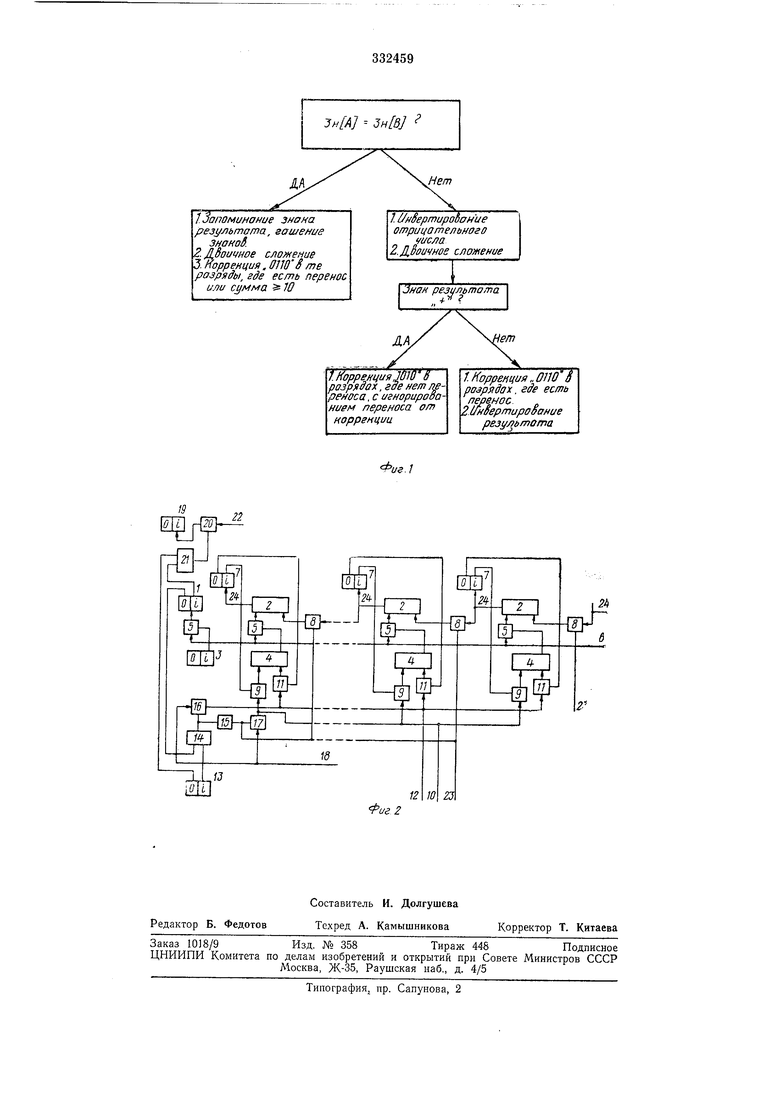

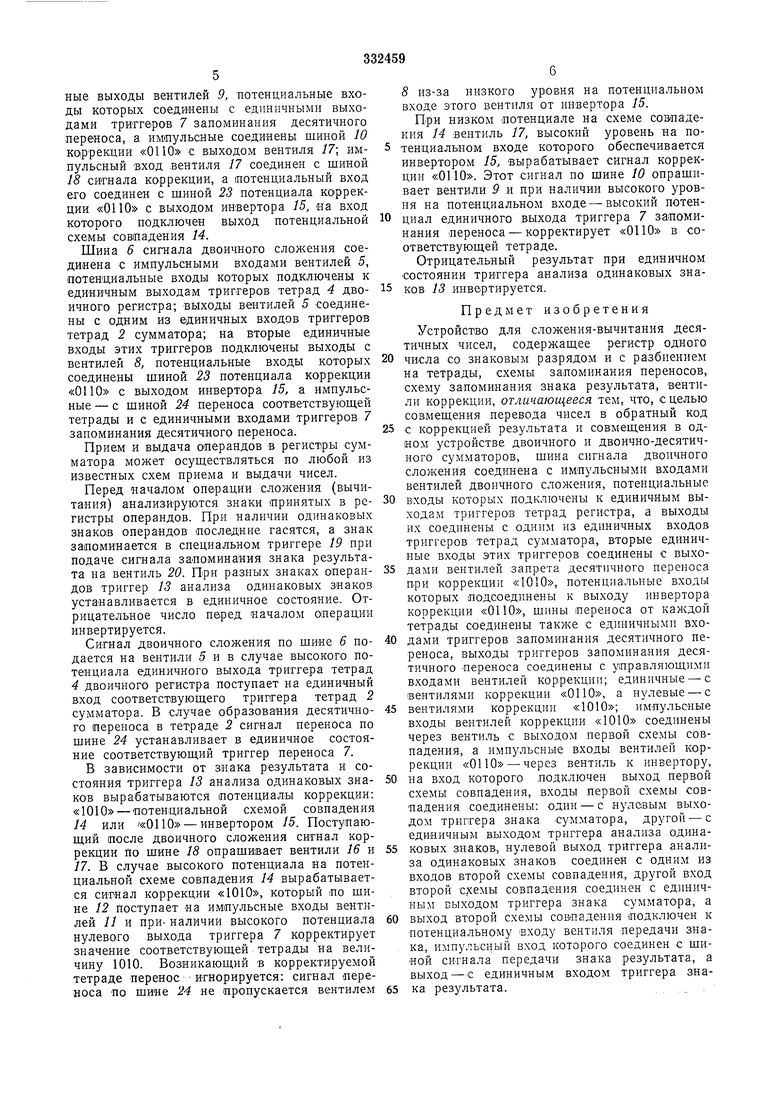

Фиксируется переполнение . На фиг. 1 схематично изображен алгоритм выполнения операций устройством для сложения (вычитания) десятичных чисел; иа фиг. 2 -схема для сложения (вычитания) десятичных чисел.

регистра с небольшим добавлением оборудования, учитываюш;им специфику выполнения операций десятичной арифметики.

Схема содержит:

а) триггер знака сумматора / и сгруппированные потетрадно триггеры двоичных разрядов сумматора - тетрады 2,-позволяюш,ие представить десятичный разряд в коде «8421 ;

б) триггер знака двоичного регистра 3 и триггеры тетрад 4 двоичного регистра;

в) схему двоичного сложения, содержащую вентили 5 и шину 6 сигнала двоичного сложения;

г) схему десятичного переноса, состоящую из триггеров 7 запоминания десятичного переноса и вентилей 8 запрета десятичного переноса при коррекции «1010 ;

д)схему коррекции «ОНО, состоящую из вентилей 9 и шины 10 сигнала коррекции

е)схему коррекции «1010, состоящую из вентилей // и шины 12 сигнала коррекции «1010 ;

ж) схему образования сигналов коррекции, состоящую из триггера 13 анализа одинаковых знаков, первой потенциальной схемы совпадения 14, организующей потенциал коррекции «1010, инвертора 15, выдающего потенциал коррекции «ОНО, вентилей 16 и 17, шины 18 сигнала коррекции;

з) схему запоминания знака результата, состоящую из триггера 19 запоминания знака результата, вентиля 20, второй потенциальной схемы совпадения 21 ,и шины 22 сигнала передачи знака результата;

и) шину 23 потенциала коррекции к) шину 24 переноса соответствующей тетрады.

Единичный выход триггера 13 анализа одинаковых знаков подключен на вход потенциальной схемы совпадения 14, второй вход которой соединен с нулевым выходом триггера / знака сумматора; нулевой выход триггера 13 соединен с одним из входов потенциальной схемы совпадения 21, второй вход которой соединен с единичным выходом триггера 1 знака сумматора, а выход--с потенциальным входом вентиля 20, на импульсный

вход которого подключена шина 22 сигнала передачи знака результата; выход вентиля 20 соединен с единичным входом триггера 19 запоминания знака результата. Выход потенциальной схемы совпадения 14 соединен со

входом вентиля 16, импульсный вход которого соединен с шиной 18 сигнала коррекции; выход вентиля 16 соединен шиной 12 сигнала коррекции «1010 с импульсными входами вентилей 11 потенциальные входы которых

соединены с нулевыми выходами триггеров 7 запоминания десятичного переноса, выходы вентилей 11 соединены с единичными входами триггеров тетрад 4 двоичного регистра. На вторые единичные входы триггеров тетрад 5 ные выходы вентилей 9, потенциальные входы которых соединены с единичными выходами триггеров 7 запоминания десятичного переноса, а импульсные соединены шиной W коррекции «ОНО с выходом вентиля 17; им-5 пульсный вход вентиля 17 соединен с шиной 18 сигнала коррекции, а потенциальный вход его соединен с ш,иной 23 потенциала коррекции «ОНО с выходом инвертора 15, иа вход которого подключен выход потенциальнойЮ схемы совпадения 14. Шина 6 сигнала двоичного соединена с импульсными входами вентилей 5, потенциальные входы которых подключены к единнчным выходам триггеров тетрад 4 дво-15 ичного регистра; выходы вентилей 5 соединены с одним из единичных входов триггеров тетрад 2 сумматора; на вторые единичные входы этих триггеров подключены выходы с вентилей 8, потенциальные входы которых20 соединены шиной 23 потенциала коррекции «ОНО с выходом инвертора 15, а импульсные - с шиной 24 переноса соответствующей тетрады и с единичными входами триггеров 7 запоминания десятичного переноса.25 Прием и выдача операндов в регистры сумматора может осуществляться по любой из известных схем приема и выдачи чисел. Перед началом операции сложения (вычитания) анализируются знаки принятых в ре-30 гистры операндов. При наличии одинаковых знаков операндов последние гасятся, а знак запоминается в специальном триггере 19 при подаче сигнала запоминания знака результата на вентиль 20. При разных знаках операн-35 дов триггер 13 анализа одинаковых знаков устанавливается в единичное состояние. Отрицательное число перед началом операции инвертируется. Сигнал двоичного сложения по шине 6 по-40 дается на вентили 5 и в случае высокого потенциала единичного выхода триггера тетрад 4 двоичного регистра поступает на единичный вход соответствующего триггера тетрад 2 сумматора. В случае образования десятично-45 го переноса в тет:раде 2 сигнал переноса по шине 24 устанавливает в единичное состояние соответствующий триггер переноса 7. В зависимости от знака результата и состояния триггера 13 анализа одинаковых зна-50 ков вырабатываются потенциалы коррекции: «1010 - Потенциальной схемой совпадения 14 или «ОНО - инвертором 15. Поступающий после двоичного сложения сигнал коррекции по шине 18 опращивает вентили 16 и55 17. В случае высокого потенциала на потенциальной схеме совпадения 14 вырабатывается сигнал коррекции «1010, который по шике 12 поступает на импульсные входы вентилей // и при- наличии высокого потенциала60 нулевого выхода триггера 7 корректирует значение соответствующей тетрады на величину 1010. Возникающий в корректируемой тетраде перенос -игнорируется: сигнал переноса по шине 24 не пропускается вентилем65 6 8 из-за низкого уровня на потенциальном входе этого вентиля от инвертора 15. При низком потенциале на схеме совпадения 14 вентиль 17, высокий уровень на потенциальном входе которого обеспечивается инвертором 15, вырабатывает сигнал коррекцин «0110. Этот сигнал но шине 10 опрашивает вентили 9 и при наличии высокого уровня на потенциальном входе - высокий потенциал единичного выхода триггера 7 запоминания переноса - корректирует «ОНО в соответствующей тетраде. Отрицательный результат при единичном состоянии триггера анализа одинаковых знаков 13 инвертируется, „ Предмет изооретения Устройство для сложения-вычитания десятичных чисел, содержащее регистр одного числа со знаковым разрядом и с разбиением на тетрады, схемы запоминания переносов, схему запоминания знака результата, вентили коррекции, отличающееся тем, что, с целью совмещения перевода чисел в обратный код с коррекцией результата и совмещения в одном устройстве двоичного и двоично-десятичного сумматоров, шина сигнала двоичного сложения соединена с импульсными входами вентилей двоичного сложения, потенциальные входы которых подключены к единичным выходам триггеров тетрад регистра, а выходы их соединены с одним из единичных входов триггеров тетрад сумматора, вторые единичные входы этих триггеров соединены с выходами вентилей запрета десятичного переноса при коррекции «1010, потенциальные входы которых аподсоединены к выходу инвертора коррекции «ОНО, шины переноса от каждой тетрады соединены также с единичными входами триггеров запоминания десятичного переноса, выходы триггеров запоминания десятичного -переноса соединены с управляющими входами вентилей коррекции; единичные - с вентилями коррекции «ОНО, а нулевые - с вентилями коррекции «1010 ; импульсные входы вентилей коррекции «1010 соединены через вентиль с выходом первой схемы совпадения, а импульсные входы вентилей коррекции «ОНО - через вентиль к инвертору, на вход которого .подключен выход первой схемы совпадения, входы первой схемы совпадения соединены: один - с нулевым выходом триггера знака сумматора, другой - с единичным выходом триггера анализа одинаковых знаков, нулевой выход триггера анализа одинаковых знаков соединен с одним из входов второй схемы совпадения, другой вход второй схемы совпадения соединен с единичным выходом триггера знака сумматора, а выход второй схемы совпадения подключен к потенциальному входу вентиля передачи знака, импульсный вход которого соединен с ши«ой сигнала передачи знака результата, а выход-с единичным входом триггера знака результата. с

11/я§ертиробание отри LI а тельного исла

2.M,/ff

oavHOS сложение

нам резильтота

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ-ВЫЧИТАНИЯ ДВОИЧНЫХ ЧИСЕЛ | 1972 |

|

SU451078A1 |

| Устройство для суммирования и вы-чиТАНия дВОичНО-дЕСяТичНыХ КОдОВ | 1978 |

|

SU813415A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| УСТРОЙСТВО для СУММИРОВАНИЯ | 1973 |

|

SU393740A1 |

| УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ КОДОВ | 1967 |

|

SU201774A1 |

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1967 |

|

SU190658A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2402803C2 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Устройство для сложения десятичных чисел | 1975 |

|

SU595729A1 |

| РЕВЕРСИВНЫЙ ДЕСЯТИЧНЫЙ СЧЕТЧИК | 1973 |

|

SU374643A1 |

Даты

1972-01-01—Публикация