..,; : . . Изобретение отвосится к области вычислительной техники и быть исцользбваяо в арифметических устройствах для сложвния-«ычитавня двоично-десятичных кодов. Известны устройства для сложения-ш чйтший двоично-десятичных кодов, в кото рых операция вычитания реализуется без перевода отрицательного числа в дополнительный код, а с использованием формирователей инверсных кодов и схем коррекции, юзволяюпшх производить бПаредвН над десят чволми числами по правилам дво ичной арифметики с применением соответн ствующих корректирующих кодов l, jz. В этих устройствах применёйЫ входные it. выходные блоки инвертирования кодов/ пбрвый и второй сумматоры, схемы коррекции И формирования межтетрадаых переносов. Указанные устройства првднаана чены дпя сл женвя.«ычитания чисел, представленных двоично-десятичным парапавль ным кодом, их реализация требует большого объема оборудования, и затрудивет Использование в арифметсгческвх устрбйсрвах последовательного действия. Наиболее близким по технической сущ«. ности к npenni ai vtoMy является последе вательный двоичдо-лесйтный сумматорвь1читатель, содержащий пёркли И второй одноразрядные сумматоры, входной форм1{рователь инверсного кода, блок анализа результата споженвя и бпок , причём вход входного формиров:ателя инверсного вода подуииочен к шине одаогЬ из операндов, у Еравпяюшве входы - к шв нам сложения и вычйтавия,-а выход - ко первого одноразрядного сумматора, /фугой вход которого соединен с шиной другого опершда, а выхад - со входом блока анализа результ ата сложения, уп- ршлшошие вхофг которого ооединени с :шинамв (ев|ия и синхронизации, а выход - со вхОдсян BTOpoix одаоразрядного cybiMatopa, /фугой вход которого соедвнен с выходомблок а i koppeKiunt, первый вход которого 1К дкпючен к выходу переноса первого одноразрядного сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для суммирования и вы-чиТАНия дВОичНО-дЕСяТичНыХ КОдОВ | 1978 |

|

SU813415A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Устройство для сложения и вычитания | 1978 |

|

SU842798A1 |

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

| Устройство для последовательного сложения и вычитаний чисел | 1976 |

|

SU579613A1 |

| Устройство для суммирования двоично-десятичных кодов | 1977 |

|

SU684542A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Арифметико-логическое устройство | 1978 |

|

SU922727A1 |

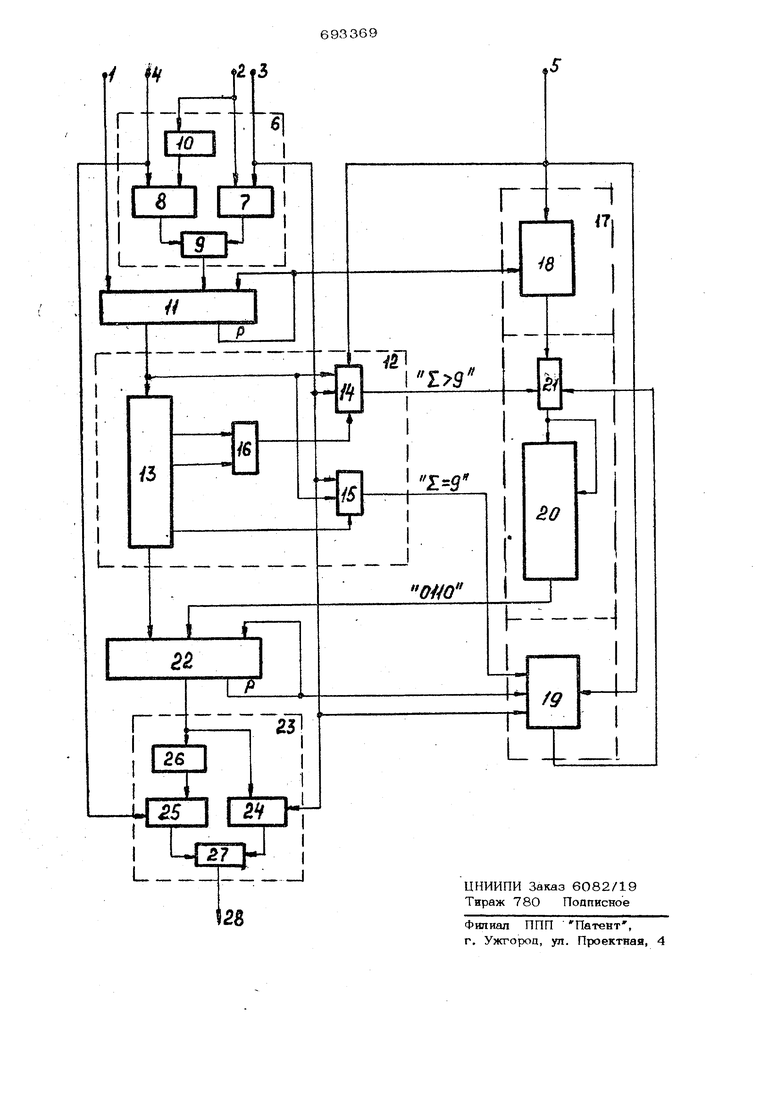

ifnffft-r--T iuti- i:-: Л 36 второй вход - к выходу блока анализа ревультата сложения, а третай и четвертый входы к шинам сложения и синхронизат№9 з. Недостатком данного устройства ЯЕШЯется то, что в нем используюйья два ти-, па корректирующих кодов: ОНО при сложении и 1010 при вычвтаний, фо5 мирование которых осушествляется схемой коррекции с использованием триггера В элементов И, ИЛИ, требуюпйй для управления ее работой четырех синхронизирующих сигналов, сдвинутых во времени. Крбмё вычитании окончательный результат с выхода второ1х сумматора отличается на единицу младшего десятичиого разряда от действительного значения разности, так как используется инверсный а не Дополнительный код отрицательного числа. Поэтому использование этого сумматоранзычитателя в арифметических уст ройствах требует дополнительной коррекций результата второго сумматора при вы читании, а также дополнительной схемы типа регистра сдвига для формирования сдвину1Ь х во времени синхронизирующих сигналов. Целыо настоящего изобретения является упрощение устройства. Для достижения поставленной цели, сумматор- вычитатель содержит выходной формирователь инверсного кода, вход кото рого подключен к вкйсоду второго одноразрядного сумматора,управляющие входы к шинам сложения, и вычитания, а к выходу сумматора-вычитателя, пятйй и шестой входы блока коррекции подключе ны сро-шетственно ко второму выходу бло ка анализа- результата сложения к выходу пёреноса второго одноразрядного сумматора. .; ;. ,. . .. - ..,.. Кроме того, блок коррекции содержит апемен1Ы И и ИЛИ и регистр сдвига, входы первого И второго разрядов которЬго подключены к выходу элемента ИЛИ, входы которого подключены к выходам первого и второго элементов И и второму входу блока коррекхши, первый вход которого подключен к первому входу первого аяементаИ, второй вход которого соединен с четвертым входом блока коррекции, входы второго элемента И соединены с ррёч/ыол, четвертым, пятым и шестым вхо« дами блока коррекции, к вьгходу которого ж дключен выход регистра сдвига. На чертеже изображена схема предлагаемого последрватвлыгого двоично есятнчного сумматора-вычвтателя. 694 Устройство содержит входы 1 и 2 для подачи слагаемых, шины сложения 3 и вычитания 4, шину 5 синхрониаацив для подачи синхронизирующих импульсов с деЛЬЮ выделения межтётрадных переносов, входной формирователь 6 инверсного кода, выполненный на элементах И 7 и 8, ИЛИ 9, НЕ 10, выход которого соединен со входом первого одноразрядного сумматора 11, выходом суммы которого соединен вход блока 12 анализа результата сложения, выполненный на четырехразрядном регист ре 13 сдвига и элементах И 14 и 15, ИЛИ 16. Другие входы блока 12 анализа результата сложения соединены с шиной 3 сложения и шиной 5 синхронизации. Выхода бло|:а 12 анализа результата сложения соединены со входами блока 17 коррекции выполненного на элементах И 18 и 19 и трёхраарядном регистре 20 сдвига и элемента ИЛИ 21. Входы элемента И 18 соединейы с выходом переноса первого одноразрядного сумматора 11 И шиной 5 ёийхронизашй, а входы элемента И 19 соединены ,с шиной 3 сложения, шиной 5 синхронизации, выходом блока 15 анализа результата. Выходы элементов И 18 и 19 соединены со входом регистра 2О сдаиэга через элемент ИЛИ 2J., вход крторого соединен также с выходом 9 блока 12 анализа результата Вьзгход регистра 20 сдаига блока коррекции 17 соеданен со входом второго одноразрядного сумматора 22, выход переноса которого соединен СЬ вХодрм элемента И 19, а выход суммы - со входом выходао-, rt) фо)рмировагеяй 23 инверсного кода, содержащего элементы И 24 и 25, НЕ 26, ц 27, выход 28 выдачи окончательно результата. . JUBa Числа в прямом поеледовательЕЮ дйьично-десятичном Коде поступают на входы 1 н 2. При одинаковых знаках обоих слагаемых (плюс или Минус) на управляющей ш ине Сложения 3 устанавливается уровень , и сложение в первом одноразрядном сумматоре 11 производится в прямых кодах по правилам двоичной арифметики с учетом возникающих переносов. При разных знаках слагаемых уровень устанавливае тся ца шине вычйтателя 4 и большее по абсолютной- величине слагаемое подается на вход 2, в результате чего на вход первого сумматора 11 оно лосту- пает в инверсном коде. При сложении может иметь место нарушение двоично-деся-тчного кода при нолу5 6933696

чений на выходе первого одноразрядногосигнал S , возникаюишй при сложесумматора 11 втетраде суммы числа боль-нии, с выхода элемента И 19 - межтет.

ше 9 или при возникновений межтетрадво-радные переносы второго сумматора 21, .

го переноса на старшего разряда тетрадывозникающие при сложении, когда значение

суммы, которое может быть устранено sрезультата первого сумматора равно 9

сложением результата первого одноразрЯд- -):). Выход суммы второго сумматоного сумматора 11 и выхода регистра ра 22 соединен со вхо/$)М выходного форс корректирующим кодом шесть (оно)мирователя 23 инверсного кода, обеспечпи

на втором одноразрядном сумматоре 22.ваюшего инвертарованве результата вчо- Сложение на втором сумматоре 22 осу- рого сумматора при вычитании. Окончашествляется по правилам двоичнойоельный результат сложения-вычитания и

арифметики с учетом возникающих пере-прямом коде на выход 28 поступает со.

носов. Нарушение кода при сложении мо- второго сумматора 22 при сложении че-

жет также возникнуть на выходе второгорез элементы И 24, ИЛИ 27, а при высумматора 22 при сложении тетрады сум-читании через элементы НЕ 26, И 25,

мы первого сумматора девятъ (lOOl)ИЛИ 27 выходного формирователя 23 инс единицей межтетрадного переноса, воз-версного кода, управление которым осу никающей при коррекции предыдущей тет -ществляется шинами сложения 3 и вычирады. В этом случае также производится ...тания 4.

коррекция сложения с кодом шестьНиже приведены примеры выполнения

(ОНО) на втором сумматоре 22,устройством операций сложения-ш.гчитанвя.

При вычитании необходимость коррек-Пример 1. 273-471 -198

ции результата первого сумматора 11(QQQ 1ООО, знак результатавозникает только при наличии межтетрад- 25запоминается)

ного переноса из старшего разряда тет.а) инвертирование большего числа-471

рады суммы. Коррекция в этом случае(1011, 10ОО 1110)

однотшгаа с коррекцией при сложении иб) операция

осуществляется добавлением к результа-п niii nn i

ту первого сумматора 11 корректяруюпю-30+ iin ii

го кода ОНО на втором сумматоре 22..Т 7 . п

Анализ результата первого сумматора 111О ОООО ООО1 осуществляетсй блоком 12 анализа результата сложения, для чего код с выходав) ОНО ОНО - коррекпня первого сумматора 11 поступает на ре- 51110 6116 0111 гисчр 13, с помощью которого и элемей-где возник тов И 14, 15 и ИЛИ 16 получаются сиг-межтетрадный налы S 9 иS 9 соответствующиеперенос значению тетрадм суммы после первогоj,) OQOI lOOl lOOO - инвертясумйатора 11 больше или равно 9, посту- - -- паюпше йа блок кррреюдии. Выделение19 8 межтетрй1дных переносов первого и второго сумматора 11 и 22, а также сигна-П Р «мер 2. 148+259 407 (О1ОО, 9 и формирования ,ОООО, 0111, знак результата + запокоррект«рующего кода ОНО осущест- минается) вляется на элементах И 14, 18, 19 син- } операция хросигналами, поступающими на шину. 50001 010О 10ОО синхронизации в момент сложения старших О01О О101 1001 разрядов тетрад слагаемых. Корректирую- ... и, , i. i . i г. ,i. i - «« i ший код Olio получается на регистреООН, 101О, ООО1 20, выход третьего разряда которого сое-б) ОНО ОНО динен со входом второго сумматора 22,OlOO -QOOO 6111 - коррекция

На входы первого и второго разрядов -

гистра 20 чере,з элемент ИЛИ 21 посту- 554 О 7 пают с выхода элемента И 18 межтетрадные переносы первого сумматора 11, воз-П р и м е р, 3. - 239-452 -691 пикающие при сложении и вычитании, с(ОНО, 10О1, знак результата - запо- выхода блока анализа результата 12 -минается) а) операция Использрьанйе в данном посдедовательном двойчнб-десятичном сумматорё ычита телб одного типа корректйрзтошего кода ОНО при сложении-вычитании и учет йвовчных переносов в первбм и втором сумматорах позволяет упростать схему сумматора-фычитателя по сравнению с известным за счет уменьшения числа элементов в блоках коррекции в формирования межтетраднЫх переносов, так как при данном типе коррекции не требуются элементе для игнорирования межтетрадных переносов от коррекции на втором сумматоре а ЙЙёМ&НЧЫ для КОММУТЙЦИИ различных коррект ующих кодов при сложении-вычитании. Кроме того, реализация блока коррекции в данном устройстве на двух эле- ментах И, элементе ИЛИ и трехразрядном регистре сдвига, не уменьшая быстродействия блока коррекции по сраБнению с из вёстНЫМ устройством, упростить устройство за счет того, что для управления его работой необходим один сйнхронизируюшнй сигнал, а на четыре сдвинутых во времени сигнала (прототип), формирования которых требуется дополнительная схема типа регистра сдвига. Введение в схему суммато)1а-вычйтатепя вьтходного формирователя инверсного кода помимо однотипности коррекции позволяет получить правильный окончательный результат без дополнительного учета единиян младшего десятичного разряда при вычитаний, что расширяет функциональные возможности устройства, цосксзльку| предлатаемый сумЙатрр -ФЫчататель вьщолняёт функцию, отсутствующую в прототапе, во необходимую в ари4 4етческом устройстве дл:я получения правильного результата. ;-: :.. ; ... / . Формула н в о б р е т е в и я 1, Последовательный двоично-десятичный сулсматор-ш читаТель, содержащий пе вый В второй одноразрядные сумматоры. 6 698. , .. входной формирователь инверсного кода, блок анализа результата сложения и блок коррекции, причем вход входного формирователя инверсного кода подключен к шяне .одного из операндов, унравл$иошае вхоj к шинам сложения и вычитания, а виход ко входу первого одноразряд;1ого сумматора, другой вход которого соединен с Шиной другого операнда, а выход - со входом блока анализа результата спожения управляющие входа которого соединены с шинами сложения и синхронизации, а вы- хйд - йойхвдбМ второго одноразрядного сумматора, другой вход котьрого соединен с выходом блока коррекции, первый йход которого подключен к Кзгходу переноса nepeoits одноразрядного сумматора, второй вход - к выходу блока анализа результата сложения, а третий и четвертый входы - к шинам еложения и синхронизации, о т л и ч а ю щ и и с я тем, что, с целью упрощения сумматора-еьгчитателя, он содержит выходной формирователь инверсного кода, ёХОд которого подключен к выходу Ёторого; одноразрядного сумматора, управпяюшие входЬ - к шинам ело- . женйй и йЫчитания, а вьтход к ныходу суммйтора-вычитателя, пятый и шестой входы блока коррекции подключены соответхзтвенно ко бторому выходу блока анализа резуЛьт-ата сложения и выходу переноса второго одноразрядного сумматора. 2. СумМйтор-вычитатель по п. 1, о т« «/ а ю щи И с я тем, ч То блок . рекции содержит элементы И и ИЛИ в регистр сдвига; входы первого и второго разрядов которого подключены к выходу элемента ИЛИ, входы которого подключены к даходам itepBoix) ивторого элементов И в второму входу блока коррекции, перБьгй Ёхбд K OTOjidro подключён к первому входу первого элемента И, второй вход которого соединен с четвертым входом блока коррекций, вХодаЛвторбго элемента И cbettBHeiiibit с третьим, четвёртым, пятым и трестым входам блока Коррекции к выходу KOTopoi-o подключен выход реriacTpa сдвига. ИстЬчникй информации, прийнйлё во внимание при экспертазе 1.Авторское свидетельство СССР NO 332459, кл. G.06 F 7/50, 1972. 2.Авторское свидетельство СССР № 393740, кл. G 06 F 7/50, 1973. 3.Авторское свидетельство СССР № 3S7364, кл. Q 06 F 7/50, 1973 (прототип)..

Авторы

Даты

1979-10-25—Публикация

1977-06-27—Подача