3

j o;;ui слагаемого в сумматор, первые и вюрые выходы которого подключены к 11срвым п ьторым управляющим входам олока запесеаия кода слагаемого в сум.матор, третьи i; четвертвш выходы олока управлепия запесепием кода слагаемого в сумматор подключепы ко входам прибавлеппя шестп п вычпталпя шесгп тетрад сумматора, выход зпака резулвтата сумматора аодключеп ко второму входу блока управлеыпя, первы11 п BTopoii вв1ходв1 которого подключепы к управляювцпм входам сумматора, а трегпн, четверчъи, пятвп-, шссгой п седьмой выходы - ко вюрому, третьему, четвертому, пятому п шестому входам олока управлеппя запесепием кода елагаемого в сумматор.

Иоставлеппая цель доетпгается также за счет того, что блок управле 1пя запесепием кода слагаемого в сумматор состопт пз п одаотппных узлов управлеппя запесеппим, каждып пз которых содержпт трпггер, элемептв И п ИЛИ, причем единнчпып вход триггера подключеп к соответствующему первому входу блока, а нулевой вход - ко второму вход) блока, третий вход которого подк.почеп, к первым входам первого и втор010 aJicMenioB И, выходы которых 1юдключены к первым входам первого п второго Jлeмeiiтoв rlJiri. четвертьи- вход блока подключеп к первым входам третьего и четвертого алемептов 1-1, ВЫХОДВ1 которых подключепы ко вторым входам первого п второго элсмептов г1Лгт, пятып и пиестой входы блока пoдкJпoчeiiЫ к первым входам пятого к шестого элементов И, вторвш входы которых подключены соответетвеипо к единичному и нулевому выходам TpniT epa, а выходы - к соответствуюшим третьему н четвертому выходам блока, едппичпый выход триггера также подключен ко второму входам первого н четвертого элементов l-i, г. пулевой- ко вторым входам второго н третьего элементов И, выходы первого н второго элементов ИЛИ соедннены е соответствуюн1,ими первым н вторым выходами блока.

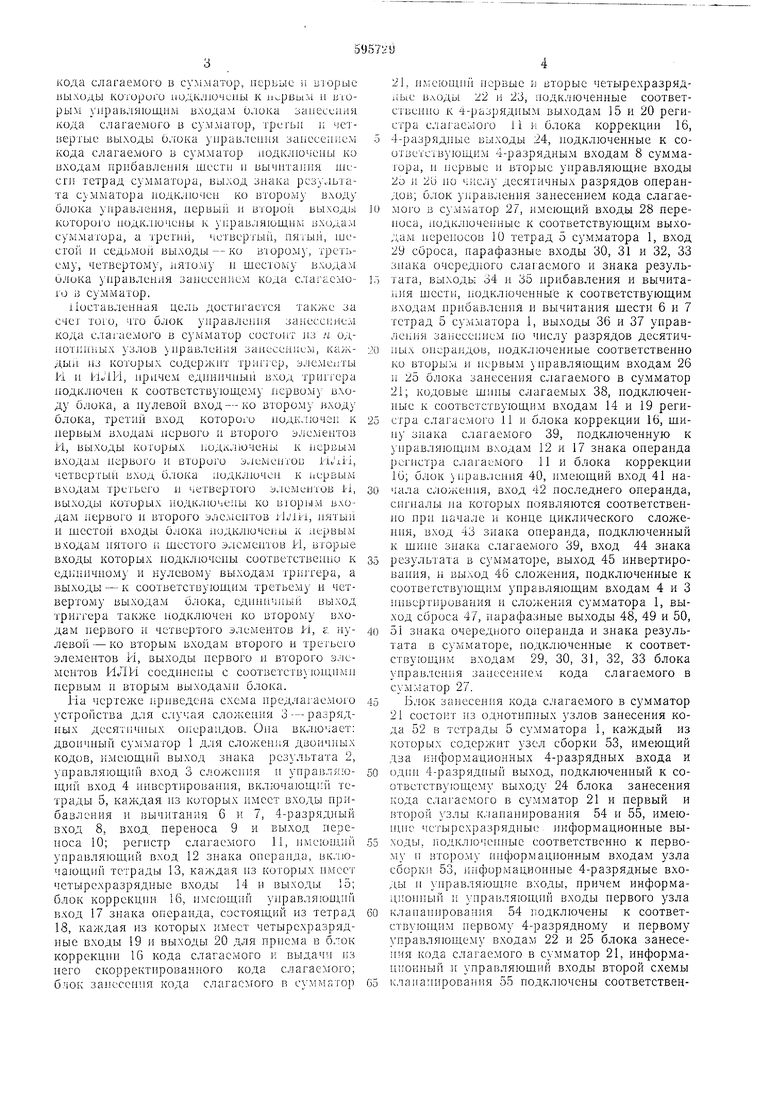

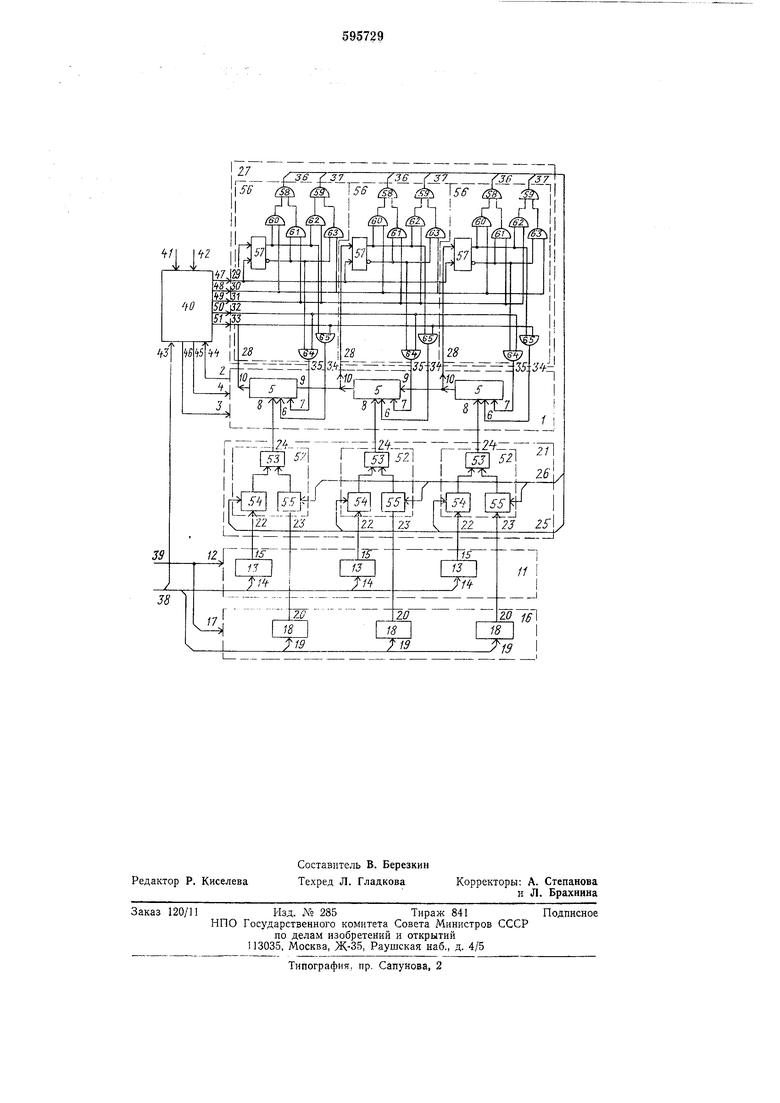

На чертеже приведена ехема предлагаелюго устройства для случая сложения о -разрядных десятичпьгх операндов. Оиа включает: двоичный сумматор 1 для сложения двоичных кодов, имеющий выход знака рез -льтата 2, управляющий вход 3 сложения н управляющнй вход 4 инвертирования, включающий тетрады 5, каждая из которых имеет входы нрибавлепия п вычнтапия б и 7, 4-разрядный вход 8, вход переноса 9 и выход переноса 10; регистр слагаемого И, пмеюилий управляющий вход 12 зпака операпда, включающий тетрады 13, каждая пз которых имеет четырехразрядные входы 14 и выходы 15; блок коррекции 16, имеющий уиравляющий вход 17 знака онеранда, состоящий из тетрад 18, каждая из которых имеет четырехразрядные входы 19 н выходы 20 для приема в блок коррекции 16 кода слагаемого и выдачи из него скорректированного кода елагаелгого; блок занесения кода слагаемого в сумматор

21, имсюодий первые и вторые четырехразрядные входы 22 п 23, подключенные соответетвенно к -разрядным выходам 15 н 20 регистра слагаемого 11 н блока коррекции 16, 4-разрядные выходы 24, нодключенные к соответе1ву ощнм 4-разрядныл1 входам 8 суммагора, н нервые п вторые управляющие входы

20и 2Ь но чнелу десятичных разрядов операндов; блок управления занесением кода слагаемого в сумматор 27, имеющий входы 28 нереноеа, нoдключeiн ыe к соответствующим выходам нерепосов 10 тетрад 5 сумматора 1, вход 29 сброса, парафазные входы 30, 31 и 32, 33 знака очередного слагаемого и знака результата, выходы 34 н 35 нрнбавления н вычитаиня шеети, подключенные к соответствующим входам нрнбавлення и вычитания шести 6 и 7 тетрад 5 еумматора 1, выходы 36 н 37 управле11ия занесеннем по чнслу разрядов десятичных онера ;дов, нодключенные соответственно J-CO BTOpBiM и иервв1М управляющим входам 26 п блока занесения слагаемого в сумматор 21; кодовые шииы слагаемых 38, нодключенные к соответствующим входам 14 и 19 регистра слагаелюго 11 и блока коррекции 16, шину знака слагаемого 39, подключенную к унравляющнм входам 12 и 17 знака онеранда регистра слагаемого И и блока коррекции 16; блок )правлепия 40, имеющий вход 41 начала сложения, вход 42 последнего операнда, еигиалы и а когорых ноявляются соответетвенио при начале п конце циклического сложення, вход 43 знака операнда, подключенный к шине знака слагаемого 39, вход 44 знака результата в сумматоре, выход 45 инвертировання, н выход 46 сложення, нодключенные к соответствующим унравляющнм входам 4 и 3 ннвертирования п еложення сумматора 1, выход сброса 47, нарафазные выходы 48, 49 н 50, 51 знака очередного онеранда н знака результата в сумматоре, нодключенные к соответствуюндим входам 29, 30, 31, 32, 33 блока унравления занееенпем кода слагаемого в сумматор 27.

Блок занееенпя кода слагаемого в сумматор

21СОСТО1ГГ пз однотнпных узлов занесения кода 52 в тетрадв 5 сумматора 1, каждый нз которых содержит узел сборки 53, имеющий два информационных 4-разрядных входа и одии 4-разрядпьи1 выход, подключенный к соответствующему выходу 24 блока занесения кода слагаемого в сумматор 21 и нервый и второй злы к.аиаинрования 54 и 55, имеюи.ие четырехразрядные информационные выходы, подключенные соответственно к первому и второму И1формационным входам узла сборки 53, П формационные 4-разрядные входы п управляющие входы, причем информационный и уиравляющий входы первого узла клаиапирования 54 подключены к соответствующим иервому 4-разрядному и первому управляющему входам 22 и 25 блока занесения кода слагаемого в сумматор 21, ннформаниоиный и управляющий входы второй схемы клапанирования 55 иодключены соответственно ко второму 4-разрядному к второму управляющелп входам 23 и 26 б. занесения кода слагаемого в сумматор 21. Блок управления занесением кода слагаемого в сумматор 27 состоит из однотипных (по ЧИСЛУ десятичных разрядов) лзлов управления занесением 56. каждый из которых содержит триггер 57 фиксапитт пспсноса. единичный вход которого связан с еоотвгтствмощим входом 28 переноса блока пDaвлoRпя занесением кода слагаемого в сум ятоп 27, а нулевой выход присоединен ко входу 29 сбпоса этого же блока, элементы ИЛИ 58 и 59, выходы которых соединены с соответствугощимн выходами 36 и 37 управления закесонием блока зправления занесеннелт кода слагаемого в сумматор 27, элементы И 60, 61, 62, 63, 64, 65. При этом выходы элементов И 60 и 61 подключены ко входам члеметтта ИЛИ 58, выходы элементов И 62 н 63 по ;КЛ1очены ко входам элемента ИЛИ 59, выходы элементов И 64 и 65 подключены к соответствующим выходам 35 и 34 вычнтатпш н прибавления шести данного блока, первый вход элементов И 60, 62 и 65 подключен к едннттчному выходу триггера 57 переноса, к нулевому выходу которого подключены первые входы элементов И 61, 63 и 64, вторые входы элементов И 60 и 63 подключены к входу 30 блока управления занесением кода слагаемого в сумматор 27, который представляет собой прямую ШИНУ парафазного входа операнда, а вторые входы элементов И 61 н 62 подключены ко входу 31 того же блока, который представляет собой инверсную шину парафазного входя знака операнда, втооые входы элементов И 64 и 65 соединены соответственно со входами 32 н 33 блока правлення занесением кода слагаемого в сумматор 27, прямую и инверсную шинами парафазного входа знака результата. Устройство работает следующим образом. В исходном состоянии во всех тетоадах 13 и 18 регистра слагаемого 11 и блока коррекции 16 И в триггерах 57 переноса блока управления занесением кода слагаемого в сумматор 27 устанавливается нулевое значенне. В тетоадах 5 сумматора 1 устанавливается код ОНО. Циклическое суммирование п десятичных онерандов начинается но сигналу б.лока управления 40, который появляется одновременно с ноступлением по кодовым шинам слагаемых 38 первого слагаемого (операнда), который заносится в регистр слагаемого 11 н блок коррекции 16. Если знак первого операнда отрицательный, то его тетрады фиксируются в блоке коррекции 16 в обратном коде, а в регистре слагаемого 11 - в инверсном коде. В этом случае на выходе 49 блока управления 40 будет прнсутствовать сигнал, что при нулевых значениях во всех триггерах 57 переноса приводит к передаче в сумматор 1 содержимого тетрад 18 блока коррекции 16 через узлы клапанирования 55 и сборки 53. Если знак первого ппгп 11-гя л тожи елмыи. то операнд заноС;тг5т в регистр слагао: :ого И г- прямом коде 1 (Ьчксипуотся п блоке коррект.ии 16, с избыткпт 0110 яо вгох тотладах 18. При этом имеет лосто сигнал iia выходе 48 блока управления 40 что при н.ловых зпаче Пях в триггерах 57 тргвсдит к передаче прямого кода из тетпад 18 чороз узлы клапаннрования 57 i; гбопкч 53 :. Т: ;ды 5 сумматора 1. п кодов на iv-r-.M 8 тотРп-1 5 блок управления 40 пырабаТЫЧРОТ гттиал .ч CISOOM ыходс 46, обеснсчиваюптпп двоичное сложеннс содержимого СУМлтгтопя 1 с па входах 8 тетпад 5 н снгг л г. выходо 47. обсстрчиваюпхий cтлпoвк г. 1----ТТ, рсгх трпгггпов 57 пепенпса. В результятс сло: е; ;я первого операнда с содержи П; су-тматопр 1 ни в одной тетраде 5 не возникает переноса, т. о. в триггерах 57 пероппся б. лправлеипя заиссонием кода с.агаомого в с-лт ятоп 27 сохраняются иулсi-v-o значения. Сразу же нослс пересылки кода пспго-о операнда нз регистра cлaгae toгo 11 или блока коррекции 16 по ко.довым шиinr-r сла-ас-лых 38 нроисходнт занесение кода второго операн.да в регистр с.тагасмого П и блока коррекнли 16. Фнксанлш цтфр второго операнда НРОПСХОДНТ так же. как н фшхсация кода первого операнда. Таким образом, в кон110 поррого тактп прибавления первого слагаемого к coдeP:-к;nfo ry сумматора 1 в регнстре 11 блока коррекции 16 уже будет зафнкс рован код второго слагаемого и но 43 в блок управления 40 будет передан его знак. В процессе нрнбавлення второго слагаемого к промежутомголгу результату, находяшсм ся в c м taтope 1. выполняются такие же действия, что н прн нрибавлен15и первого слагаемого. Отлпчио этого такта сложения зактю астс5т в TOM. что в некоторых тетрадах 5 слмматора 1 oжeт ВОЗНИКНУТЬ нсрсиос, что бл.дст загЬнкспровано за счот л-ста товкн в соответствующих трнггерах 57 блока управления занесентсм ко.да слагаемого в с}мматор 27 единичных значеннй. Третье с.дагаемого, которое на момент завернтення такта прибавления второго слагае oгo блдет лжс зафиксировано соотпетствуюTn,v образо-; в псгнстрс слагаемого 11 н б,тока коррекннн 16. нере.дается в сумматор 1 для сложения след чоии1м образом: - если знак третьего слагаемого отрнцато.тыгый (сигнал на выходе 49 блока правле П1Я 40). то р тетрады 5 с мматора 1. г.чо во время предыд 1Н..сго сложсння был вырабо1ан перенос, передастся значение соответствующей тетрады 13 регистра слагаемого 11 (в узле управления заттесением 56 соответствующей тетрады триггер 57 нсреноса находится в единич Ю 1 состоянии, нрнсутствне сигнала на выходе 49 блока уиравлен1 Я 40 открывает элемент И 62, и сигнал с выхода ИЛИ 59 ноступает на первый управляющнй 25 блока занесения слагаемого в сумматор 21 и откроет узел клапанироваиня 54 соответетвующего узла занесения кода 52), а в тетрады 5 сумматора 1, где перенос отсутствовал, будут переданы значения на еоответствующих тетрад 18 блока коррекции 16 (HVлевое значение триггера 57 нереноса и наличие сигнала на выходе 49 блока унравленпя 40 об славлмвает ноявление на выходе элемента ИЛИ 58 сигнала, что. в свою очередь, прнводнт к открыванию второго узла клапаиировання 55 узла заиесеиня кода 52 в блоке занесення кода слагаемого в сумматор 21:

- еслн знак очередного онеранда гголожительиын (нриеутствхет С1тгнал на выходе 48 блока -иравлення 40. то в тетрады 5 сумматора 1, где на нредыдущем такте был перенос, подаютея значения из соответствующих тетрад 18 блока коррекции 16, а в тетрады 5 сумматора 1, где перенос отсутствовал, передаются значення из соответствуюн1нх тетрад 13 регистра слагаемого 11.

Описанный нроиесе блдет повторяться для всех п слагаемых. Поступление последнего слагаемого на лстройство сонровождается подачей на вход 42 блОКа унравления 40 снгиаля. После нпибавления в сумматор 1 последнего операнда в тетрадах 5. где был Hepeiroc. забикснровано пстинное значение десятичных цисЬр искомой десятичной . а в тетрадах 5, где перенос отсутствовал, загЬикеироваио значетттте -ooтвrтeтт IoгIттт ттнфр искомой с лмы с нчбьттко-.- 6 fOnoV Понятие «истинный в лян1ом сллчяо отппсптея к нрямому нлп обратному КОДУ десяTF Horo представ.тения. Для нолучетгия в СУМматоре окончате.тьного резлльтата необходимо содержимое в тетрадах 5, где есть избыток, уменыннть на нгееть.

Кроме того. ес.ли полученный результат нмеет .льный знак, ттеобходимо ппеобразовать его обратный код. зафиксированный в сумматоре 1, в нрямой код. ПОЭТОМУ иосле прибавлсттця поглрдттого слагаемого оеупт.ествляется коррекция тетрад 5 сумматора 1 в зависимости от знака результата v от наличия переноса при последнем слежении, затем при отриттятельном ,тaтe НРОТТЗводитея инвертирование значений во всех тетрадах 5 сумматора 1 (по снгналу на выходе 45 блока управления 40). ПРИ этом, еели знак отрицательный, то координация осуществляется за счет прибавления кода ОНО в те тетрады 5 е Мматора 1. где имел место перепое (сигнал на выходе 51 блока упрзвтения П и нулевое состояние триггера 57 цереноса соответствующем узле управления 5R через элемент И 65 обеспечивает подачу сигнала на вход прибавления тести 6 COOTRPTствующей тетрады 5 сумматора 1. ес.ти знак результата положительный, то при отеутстрии переноса в тетраду 5 сумматора 1 но -отгя сигнал вычитания кода ОНО (сигнал иа р.- ходе 50 блока управления 40. подаваемый на элеАгент И 64 соответствующего узла управления занесением 56).

После завершения ониеанной коррекции ири отрицательном результате осуществляется инвертирование содержимого всех тетрад 5, что позволяет, независимо от знака результата, иолучать значение искомому десятичной п слагаемых в прямом коде.

В раесматриваемом устройстве ири циклическом сложении п слагаемых затраты времени 7,, га формирование десятичной еуммы еоетавляет величину

-- Т-,, + Tz2(i-l) + Tzi,

где 7v4 -время, затрачиваемое на двоичное сложение 4-разрядных операндов (еложение тетрад нервого онеранда с кодом ОНО, зафнксированного в тетрадах сумматора, пли корреки.ии пос,е сложеиия последнего операнда).

-время двоичного еложення представлений десятичных оиераидов. В прототипе для наполнения подобной опеpaiu-nr пеобходимо затратить время

Г.„ 2(«-1)ГЕ2.

Таким образом, в предлагаемом устройстве достигается поставленная цель.

Формула изобретения

1. Устпойетво для сложения десятичных чисел, еоторжапег схмматор, еостояший из /г тетпал. последовательно соединенных между собой цепями переносов, регистр слагаемого, блок занесения кода cлaгae roгo в елмматор и блок уиравлення, причем кодовые игины слагаемых нодключены ко входам регистра слагаемого, (инна знака слагаемого подключена к управляюи1ему ВХОДА региетра слагаемого и первому блока прав.тения. выхолч регистра слагаемого иодк,тючены к входам б тока занесения кода елагаемого в сумматор, в ьходы которого подключены ко входам сумматора, отличающееся телг, что, с целью увеличения быстродействия. -стройетво содержит блок коррекции и блок управления занесением кода елагаемого в сумматор, причем ко входам блока коррекции иолключены кодовые шины слагаемого, а итина знака слагаемого нодключена к управляющему входу блока коррекции, выходы которого подключены к другим входам блока занесения кода слагаемого в сумматор, выходы переносов тетрад сулгматооа подключены к первым входам блока управления занесением кода слагаемого в сумматор, первые и вторые выходы которого подключены к первым и вторым управляющим входам блока занесения кода слагаемого в сумматор, третьи и четвертые выходы блока управления занееением кода слагаемого в годключеиы ко входам прибавления шести и вычитания шести тетрад сумматора, выход знака резлльтата сумматора подключен ко второму входу блока унравления, первый ;; вторе: ; вы::::ды которого подключены к управляющим входам сумматора, а третий, четвертый, пятый, шестой и седьмой выходы - ко второму, третьему, четвертому, пятому и шестому входам блока управления занесением кода слагаемого в сумматор.

2. Устройство по п. 1, отличаю ш,ееся тем, что блок управления занесением кода слагаемого в сумматор состоит из п однотипных узлов управления занесением, каждый из которых содержит триггер, элементы И и ИЛИ, причем единичный вход триггера подключен к соответствующему первому входу блока, а нулевой вход - ко второму входу блока, третий вход которого подключен к первым входам первого и второго элемента И, выходы которых подключены к первым входам первого и второго элементов ИЛИ, четвертый вход блока подключен к первым входам третьего и четвертого элементов И, выходы которых подключены ко вторым входам первого и второго элементов ИЛИ, пятый и

шестой входы блока подключены к первым входам пятого и шестого элементов И, вторые входы которых подключены соответственно к единичному и нулевому выходам триггера, а

выходы - к соответствуюшим третьему и четвертому выходам блока, единичный выход триггера также подключен ко вторым входам первого и четвертого элементов И, а нулевой - ко вторым входам второго и третьего

элементов И, выходы первого и второго элементов ИЛИ соединены с соответствующими первым и вторым выходами блока.

Источники информации,

15 принятые во внимание при экспертизе

1. А. Н. Преснухин и др. Цифровые вычислительные машины, М., «Высшая школа, 1974, с. 137-150.

2. Авторское свидетельство СССР №441562, кл. G 06 7/385, 1972 (прототип).

ira щ гН

. Lr2 i, IZZ 23 I

«

/2

39 /5 /V

3S

2.G

23 2J.

22

15

//

2 //1

20

/J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления десятичных чисел | 1976 |

|

SU744562A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1977 |

|

SU693369A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для суммирования двоично-десятичных чисел | 1980 |

|

SU1001087A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Матричное устройство для умножения двоичных и десятичных чисел | 1983 |

|

SU1200282A1 |

| Суммирующее устройство с контролем | 1983 |

|

SU1140112A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

Авторы

Даты

1978-02-28—Публикация

1975-07-29—Подача