ИзОбретение относится к области вычислительной техники, а именно, к устройствам для автоматического определения интегральных оценок графиков (начального момента любого порядка, коэффициентов Фурье спектральных плотностей, значений автокорреляционных функций и т. д.).

Известны (Время-имлульсные устройства, осуществляющие непосредственную обработку графиков в процессе сканирования ординат и выдающие результат в виде показания счетчика импульсов после полного сканирования графика.

Такие устройства основаны или на последовательном делении числа эталонных (счетных) импульсов с помощью счетчика с переменным коэффициентом деления или на изменения частоты счетных импульсов при переходе от одного разового измерения ординаты графика к другому. Эти устройст1ва реализуют следующий алгоритм вычислений:

д/т/ л

r.(0f:0)-.

/0 i l

Yгде

искомая интегральная оценка (начальный момент) коэффициент Фурье и т. д.; (f(i) - анализируемая функция, записанная графически и заданная г-ми значениями;

ф (г)-весовая функция, определяющая вид искомой оценки и заданная t-ми значениями;

i - порядковый номер ординаты;

Д - шаг между отсчетами ордцнат;

Vc - скоростьсканирования

вдоль ординат графика ;

iui - длительность однократного сканирования г-й ординаты; (i}-частота, требующаяся для однократного сканирования i-й ординаты.

Электромеханические средства программного изменения частоты позволяют использовать весьма ограниченный набор фиксированных

значений требуемых частот.

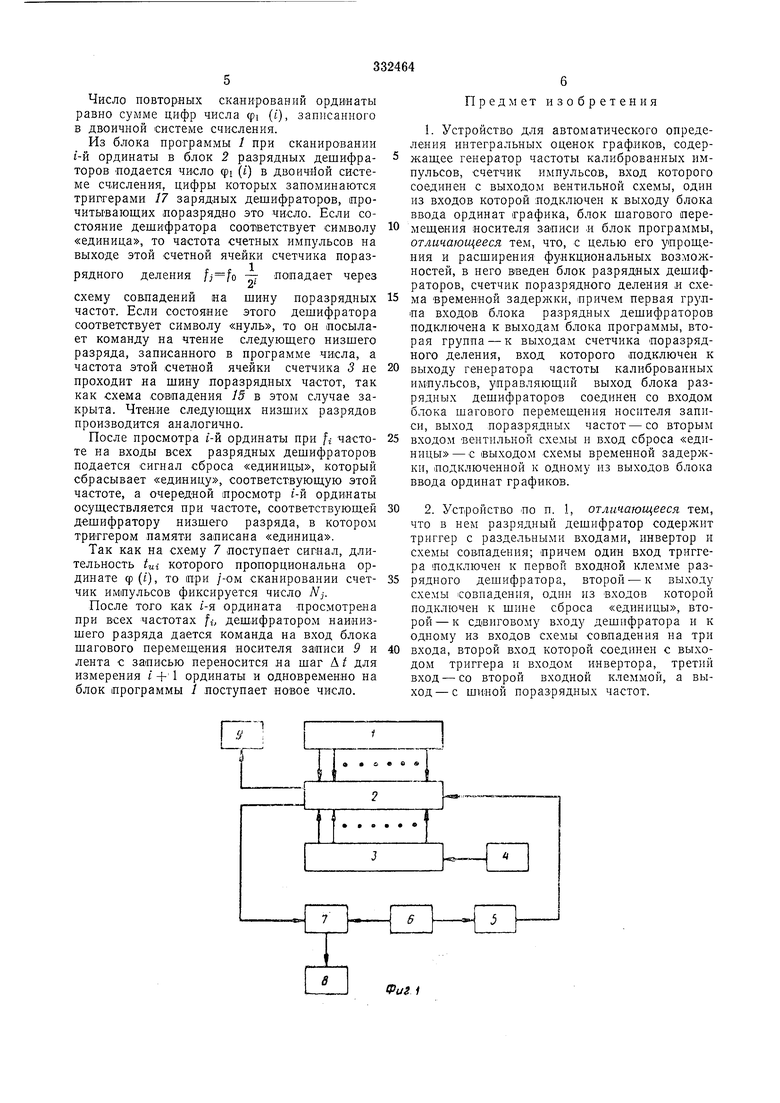

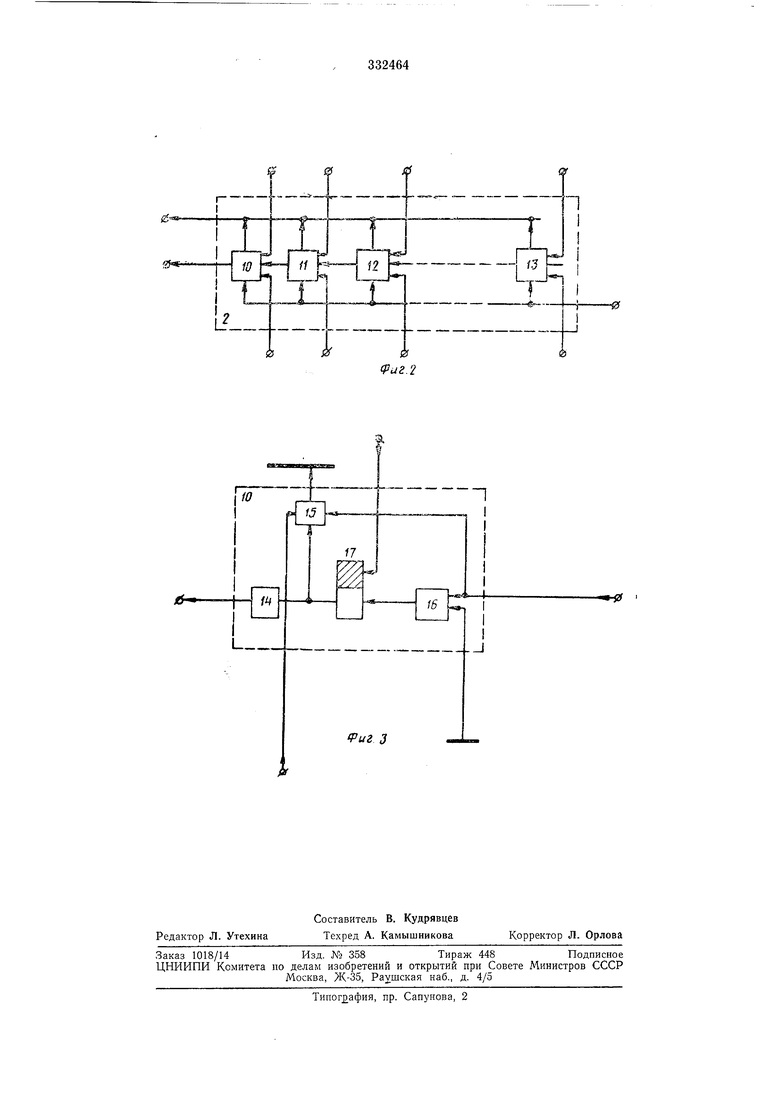

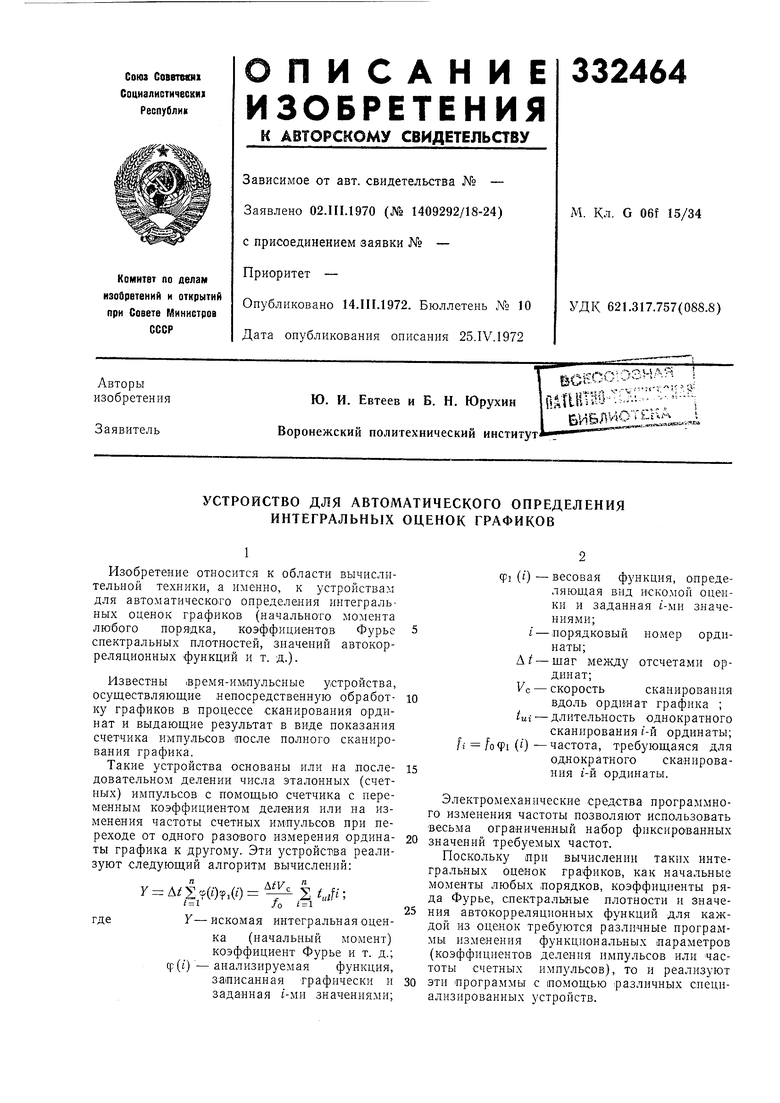

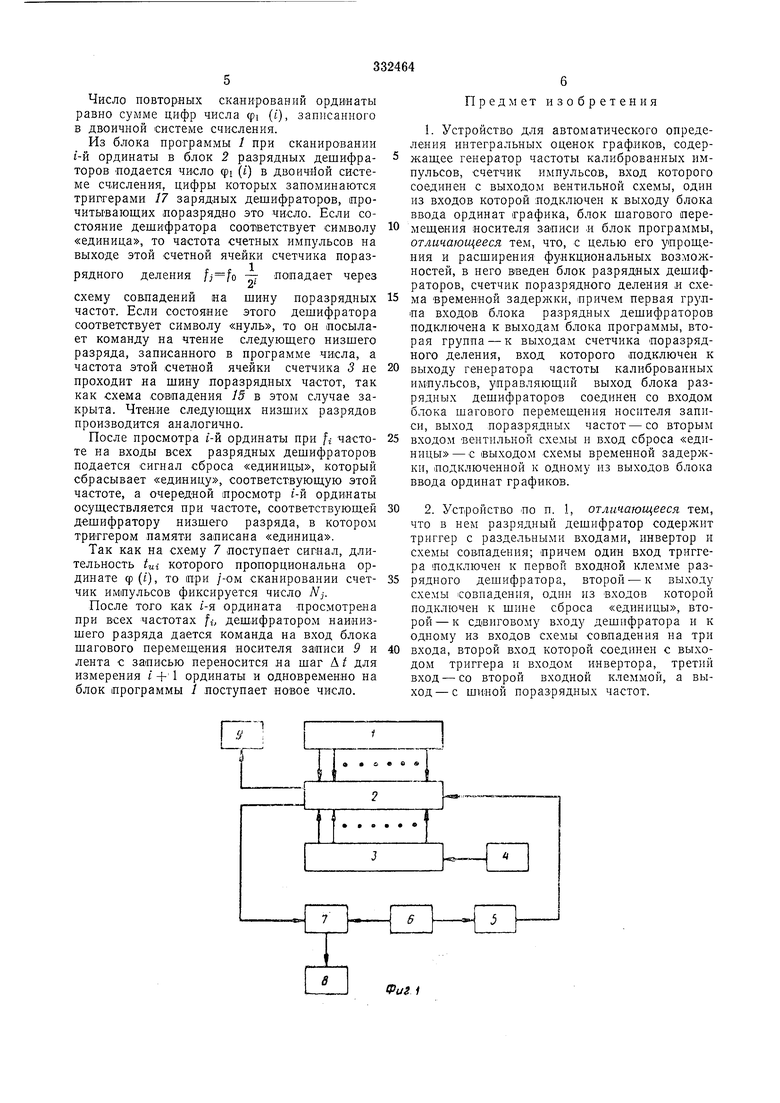

Поскольку при вычислении таких интегральных оценок графиков, как начальные моменты любых порядков, коэффициенты ряда Фурье, спектральные плотности и значекия автокорреляционных функций для каждой из оценок требуются различные программы изменения функциональных параметров (коэффициентов деления импульсов или частоты счетных импульсов), то и реализуют Известное устройство содержит генератор частоты калиброванных импульсов, счетчик импульсов, вход которого соединен с выходом схемы совпадения, один из входов которой подключен к выходу блока ввода ординат графика, блок шагового перемещения носителя записи и блок программы. Целью изобретения является расширение функциональных возможностей устройства. т. е. создание такого устройства для автома- Ю тич&ского определения интегральных оценок графиков, которое, будучи основано на программном изменении частоты счетных импульсов, позволяет определить широкий круг интегральных характеристик. Указанная цель достигается тем, что в устройство введены блок разрядных дешифраторов, счетчик поразрядного деления и схема временной задержки. Причем первая группа входов блока разрядных дешифраторов под- 20 ключена к выходам блока программы, а вторая группа - к выходам счетчика поразрядного деления, вход которого подключен к выходу генератора частоты калиброванных импульсов. Управляющий выход блока разряд- 25 ных дешифраторов соединен со входом блока шагового перемещения носителя записи, выход поразрядных частот - ко второму входу схемы совпадения, а вход сброса «единицы - к выходу схемы временной задержки, под- 30 ключенной к одному ,из выходов блока ввода ординаты графика. Блок разрядных дешифраторов состоит из последовательно соединенных дешифраторов по числу разрядов счетчика поразрядного де- 35 ления. Причем одни выходы разрядных дещифраторов объединены и образуют шину сброса «единицы, другие их выходы также объединены и образуют шину поразрядных частот.40 Каждый разрядный дешифратор содержит триггер с раздельными входами, инвертор и схемы совпадения. Один вход триггера подключен к клемме, входящей в первую группу входов блока разрядных дешифраторов, вто- 45 рой вход - к выходу схемы совпадения на два входа, один из входов которой подключен к шине сброса «единицы, второй - ко входу дешифратора и к одному из входов схемы совпадения на три входа, второй вход 50 которой соединен с выходом триггера и входом инвертора, а третий вход - с входной клеммой, входящей во вторую группу входов блока разрядных дешифраторов, а выход - к шине поразрядных частот.55 Такое построение устройства позволяет сделать его малогабаритным, простым в изготовлении многофункциональным по назначению. На фиг. 1 изображена блок-схема устройства; на фиг. 2 - схема блока разрядных де- 60 шифраторов; на фиг. 3 - схема одного разрядного дешифратора. 5 15 частоты калиброванных импульсов, 5 - схема временной задержки, 6 - блок ввода ординат графиков, 7 - вентильная схема, 8 - счетчик имлульсов, 9 - блок шагового перемещения носителя заииси, 10-13 - разрядные дешифраторы, 14 - инвертор, 15 - схема совпадения на три входа, М схема совпадения на два входа и 17 - триггер. Блок программы / соединен поразрядно с соответствуюш;ими разрядными дешифраторами 10-13 блока 2. Выходы разрядных дешифраторов соединены через общую шину с вентильной схемой 7 и через нее со счетчиком импульсов 8. Другой вход схемы 7 подключен к выходу блока ввода ординат графиков 6. Блок 6 соединен через схему временной задержки 5 и общую шину со всеми входами отдельных разрядных дешифраторов. Выход дешифратора низшего разряда соединен со входом блока шагового перемещения носителя записи 9. Разрядный дешифратор содержит триггер памяти 17 с раздельными входами, две схемы совпадения 15 и 16 и инвертор 14. Один вход триггера 17 соединен с блоком программы /, Второй - с выходом схемы совпадения 16 на два входа, входы которой соединены со схемой временной задержки 5 и выходом соседнего дешифратора 1 высшего разряда. Выход триггера 17 соединен через инвертор 14 с соседним дешифраторол низшего разряда и с одним входом схемы совпадения 15 на три входа, два остальных входа которой соединены с выходом дешифратора высшего разряда и с выходом соответствующей съемной ячейки счетчика поразрядного деления. Выход схемы совпадения 15 подключен к общей шине поразрядных частот. Определение интегральных оценок графиков с помощью предложенного устройства основано на следующем преобразовании исходной формулы: ,, At Ус2 f 1о ,аг , , } , 1п т„п т ,s.....u, С - постоянная устройства; ..щ - цифры числа (fi(i), записанного в двоичной системе счисления, NJ - число импульсов, зафиксированных при /-М сканировании t-й ординаты; Число повторных сканирований ординаты равно сумме цифр числа ф, (i), записанного в двоичной системе счисления. Из блока программы / при сканировании г-й ординаты в блок 2 разрядных дешифра- 5 торов подается число ф1 (i) в двоичной системе счисления, цифры которых запоминаются триггерами 17 зарядных дешифраторов, прочитывающих поразрядно это число. Если состояние дешифратора соответствует символу Ю «единица, то частота счетных импульсов на выходе этой счетной ячейки счетчика поразрядного деления -77 попадает через 2 --г- схему совпадений на шину поразрядных15 частот. Если состояние этого дешифратора соответствует символу «нуль, то он посылает команду на чтение следующего низшего разряда, записанного в программе числа, а частота этой счетной ячейки счетчика 3 не20 проходит на шину поразрядных частот, так как схема совпадения 15 в этом случае закрыта. Чтение следующих низших разрядов производится аналогично. После просмотра 1-й ординаты при fi часто-25 те на входы всех разрядных дешифраторов подается сигнал сброса «единицы, который сбрасывает «единицу, соответствующую этой частоте, а очередной просмотр f-й ординаты осуществляется при частоте, соответствующей30 дешифратору низшего разряда, в котором триггером памяти записана «единица. Так как на схему 7 поступает сигнал, длительность tui которого пропорциональна ординате ф (/), то при /-ОМ сканировании счет-35 чик импульсов фиксируется число Л;. После того как t-я ордината просмотрена при всех частотах /,. дешифратором наинизшего разряда дается команда на вход блока шагового перемещения носителя записи 9 и40 лента с записью переносится на шаг А для измерения +1 ординаты и одновременно на блок программы 1 .поступает новое число.

Г7 Предмет изобретения 1. Устройство для автоматического определения интегральных оценок графиков, содержащее генератор частоты калиброванных импульсов, счетчик импульсов, вход которого соединен с выходом вентильной схемы, один из входов которой подключен к выходу блока ввода ординат графика, блок шагового перемещения носителя записи и блок программы, отличающееся тем, что, с целью его yinpom,eния и расширения функциональных возможностей, в него введен блок разрядных дешифраторов, счетчик поразрядного деления и схема временной задерл ки, причем первая группа входо1В блока разрядных дешифраторов подключена к выходам блока программы, вторая группа - к выходам счетчика поразрядного деления, вход которого подключен к выходу генератора частоты калиброванных импульсов, управляющий выход блока разрядных дешифраторов соединен со входом боТока шагового перемещения носителя записи, выход поразрядных частот - со вторым входом вентильной схемы и вход сброса «единицы -с выходом схемы временной задержки, подключенной к одному из выходов блока ввода ординат графиков. 2. Устройство по п. 1, отличающееся тем, что в нем разрядный дешифратор содержит триггер с раздельными входами, инвертор и схемы совпадения; причем один вход триггера подключен к первой входной клемме раз зядного дешифратора, второй - к вы.ходу схемы совпадения, один из входов которой подключен к шине сброса «единицы, второй - к сдвиговому входу дешифратора и к одному из входов схемы совпадения на три входа, второй вход которой соединен с выходом триггера и входом инвертора, третий вход - со второй входной клеммой, а выход - с шиной поразрядных частот.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| БЕСКОНТАКТНЫЙ КОМАНДОАППАРАТ | 1968 |

|

SU210919A1 |

| УСТРОЙСТВО для СЧИТЫВАНИЯ ОСЦИЛЛОГРАММ | 1968 |

|

SU218546A1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036555C1 |

| СИНХРОННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1992 |

|

RU2037957C1 |

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1983 |

|

SU1162368A1 |

| Устройство для задержки импульсов с программным управлением | 1979 |

|

SU866722A1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| Делитель частоты с дробным автоматическиизМЕНяющиМСя КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU819966A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ И ОТОБРАЖЕНИЯ ИНФОРМАЦИИ | 1992 |

|

RU2101781C1 |

Даты

1972-01-01—Публикация