Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и систем управления.

Известен делитель частоты, содержащий шину входной частоты, счетчик импульсов и дешифратор, входы которого соединены с соответствующими выходами счетчика импульсов, сумматор по модулю 2, первый вход которого соединен с шиной входной частоты, второй - с выходом дешифратора, а выход подключен к счетному входу счетчика импульсов.

Указанный делитель частоты позволит получать любой коэффициент деления в диапазоне от 2N-1 до 2N, где N - число разрядов счетчика импульсов. Уменьшение коэффициента деления достигается за счет организации дополнительных переключений счетчика импульсов без изменения его емкости.

Недостаток этого делителя частоты состоит в низкой надежности работы, так как использование счетчика импульсов, работающего в позиционном двоичном коде, приводит к тому, что помеха, действующая во время счетного импульса, приводит к существенному искажению его содержимого.

Наиболее близким по технической сущности является реверсивный счетчик импульсов, который может использоваться в качестве делителя частоты и содержит N-разрядный регистр, состоящий из триггеров, блок запуска и блок анализа четности в виде соединенных последовательно элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, число которых равно числу триггеров N-разрядного регистра, при этом второй вход каждого, кроме первого, из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с выходом соответствующего ему триггера регистра, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к источнику команд реверса, а выход последнего - с первым ключом и через инвертор - со вторым ключом, через которые общий вход счетчика импульсов соединен со входами блока запуска.

Недостатком этого устройства является невозможность получения коэффициентов деления, лежащих в диапазоне от 2N-1 до 2N.

Цель изобретения - расширение функциональных возможностей путем получения недвоичных коэффициентов деления.

Поставленная цель достигается тем, что в делителе частоты, содержащем N-разрядный регистр, состоящий из триггеров, блок запуска, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и блок анализа четности, включающий в себя соединенные последовательно (N-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, соответствующие входы которого соединены с прямыми выходами триггеров, начиная со второго, N-разрядного регистра и с управляющей шиной устройства, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с прямым выходом триггера первого разряда N-разрядного регистра, а каждый разряд блока запуска содержит первый и второй элементы совпадения, первые входы которых, кроме первого разряда, соединены с выходом первого элемента совпадения предыдущего разряда, первые входы элементов совпадения первого разряда соединены с шиной входной частоты, выход первого элемента совпадения N-го разряда соединен с шиной выходной частоты, выход второго элемента совпадения каждого разряда соединен со счетным входом триггера соответствующего разряда N-разрядного регистра, прямой и инверсный выходы триггера каждого разряда N-разрядного регистра со второго по (N-1)-ый соединены со вторыми входами соответственно второго и первого элементов совпадения последующего разряда блока запуска, прямой и инверсный выходы блока анализа четности соединены со вторыми входами соответственно первого и второго элементов совпадения второго разряда блока запуска, вторые входы первого и второго элементов совпадения первого разряда которого соединены соответственно с инверсным и прямым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом триггера второго разряда N-разрядного регистра.

Указанная совокупность признаков позволяет получать любой коэффициент деления в диапазоне от 2N-1 до 2N путем задания необходимого числа переключений триггера, равного числу измерений состояния задействованного выхода, а общий коэффициент деления делителя частоты равен сумме коэффициентов деления старших разрядов N-разрядного регистра, начиная со второго, равного 2N-1, и числа переключений триггера первого разряда.

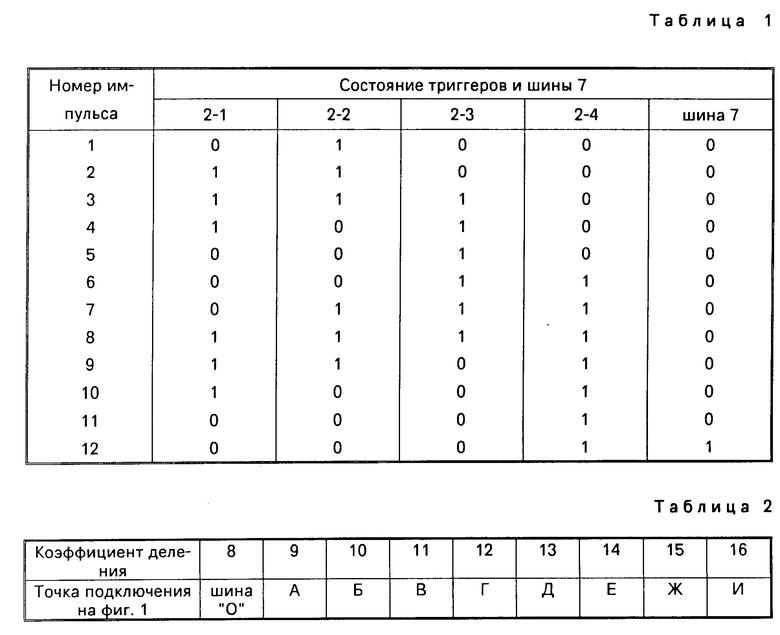

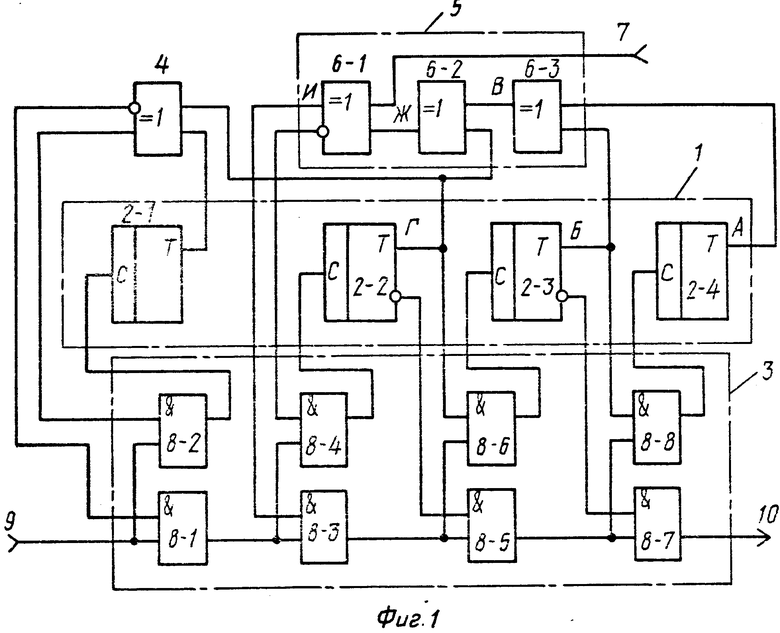

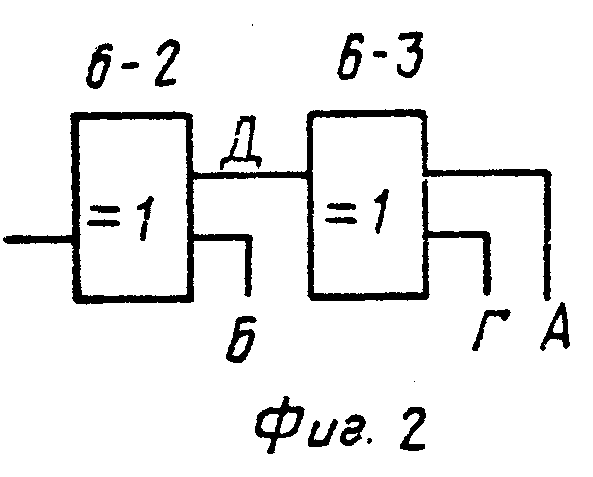

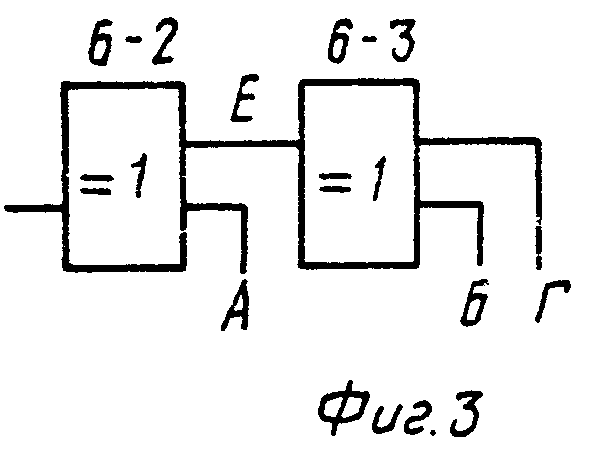

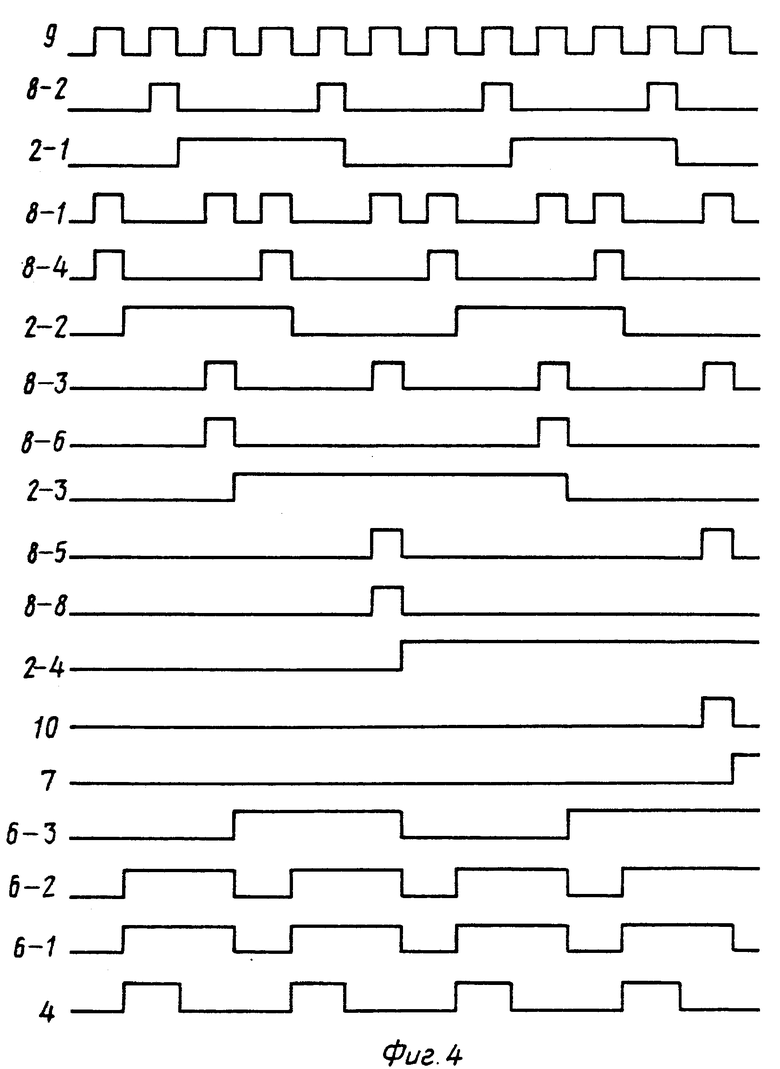

На фиг. 1 изображена структурная электрическая схема делителя частоты (на 12); на фиг.2 и 3 - примеры реализации блока анализа четности; на фиг.4 - временные диаграммы, поясняющие работу делителя частоты (на примере с коэффициентом деления 12).

Делитель частоты (фиг.1) содержит 4-х разрядный регистр 1, состоящий из триггеров 2-1,2-2,2-3 и 2-4, блок 3 запуска, элемент 4 ИСКЛЮЧАЮЩЕЕ ИЛИ и блок 5 анализа четности в виде соединенных последовательно трех элементов 6-1,6-2 и 6-3 ИСКЛЮЧАЮЩЕЕ ИЛИ, соответствующие входы которого соединены с прямыми выходами триггеров, начиная со второго, четырехразрядного регистра 1 и с управляющей шиной 7 устройства, первый вход элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с прямым выходом триггера 2-1, а каждый разряд блока 3 запуска содержит элементы, включающие в себя разряды: 8-1 и 8-2, 8-3 и 8-4, 8-5 и 8-6, 8-7 и 8-8 совпадения, первые входы которых, кроме первого разряда, соединены с выходом первого элемента совпадения предыдущего разряда, первые входы первых разрядов 8-1 и 8-2 элементов совпадения первого разряда соединены с шиной 9 входной частоты, выход четвертого разряда 8-7 первого элемента совпадения соединен с шиной 10 выходной частоты, выход второго элемента совпадения каждого разряда 8-2, 8-4,8-6 и 8-8 соединен со счетным входом триггера 2-1,2-2,2-3 и 2-4 регистра 1, прямой и инверсный выходы триггеров 2-2 и 2-3, соединены со вторыми входами соответственно третьего и четвертого разрядов 8-6 и 8-5, 8-8 и 8-7 второго и первого элементов совпадения блока 3 запуска, прямой и инверсный выходы блока 5 анализа четности соединены со вторыми входами соответственно 8-3 и 8-4 первого и второго элементов совпадения блока 3 запуска, вторые входы первого разряда 8-1 и 8-2 первого и второго элементов совпадения которого соединены соответственно с инверсным и прямым входами элемента 4 ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом триггера 2-2 второго разряда регистра 1.

Делитель частоты работает следующим образом.

В исходном состоянии триггеры 2-1-2-4 регистра 1 находятся в состоянии "0", а на шинах 7,9 и 10 - уровень "0" (логического).

Первый счетный импульс с шины 9 через разряды 8-1 и 8-4 блока 3 поступает на счетный вход триггера 2-2 и задним фронтом вызывает его переключение в состояние "1".

На прямых выходах блока 5 и элемента 4 устанавливается уровень "1". Поэтому второй импульс проходит через разряд 8-2 на счетный вход триггера 2-1 и вызывает его переключение в состояние "1". Аналогичным образом третий импульс вызывает переключение триггера 2-3 в состояние "1" и т.д. в соответствии с табл.1.

Из табл. 1 видно, что старшие разряды регистра 1, начиная со второго, работают в отраженном двоичном коде, а триггер 2-1 первого разряда с задержкой на такт повторяет состояние триггера 2-2 второго разряда. Двенадцатый импульс с шины 9 через разряды 8-1, 8-3, 8-5 и 8-7 поступает на шину 10. Как правило, делитель частоты такого типа устанавливается на входе аналогичного счетчика импульсов, работающего в отраженном двоичном коде. Поэтому двенадцатый импульс изменяет состояние этого счетчика импульсов и уровень напряжения на выходе его блока анализа четности. При этом на шине 7 устанавливается уровень "1".

Далее работа устройства происходит аналогичным образом.

Автономная работа делителя частоты может быть организована путем подключения шины 10 к счетному входу дополнительного триггера и соединения его прямого выхода с шиной 7.

В случае автономной работы схема делителя частоты может быть упрощена за счет исключения одного из элементов ИСКЛЮЧАЮЩЕЕ ИЛИ блока 5, разряда 8-8 блока 3 с одновременным подключением счетного входа триггера 2-4 к выходу разряда 8-5.

При работе устройства в режиме счета числа импульсов шина 7 может быть использована для формирования реверса. При подаче на шину 7 уровня "0" делитель частоты будет работать в режиме суммирования входных импульсов, а при подаче уровня "1" - в режиме вычитания. В этом режиме делитель частоты, схема которого приведена на фиг.1, будет нормально работать до переполнения. Импульсы, поступающие на шину 9 после переполнения, будут проходить на шину 10, не изменяя состояния элементов делителя частоты.

Для организации работы делителя в режиме счета импульсов после переполнения необходимо счетный вход триггера 2-4 подключить к выходу разряда 8-5, исключив разряд 8-8.

Для получения коэффициентов деления в диапазоне от 8 до 16 второй вход элемента 4 должен быть подключен в соответствии с табл.2.

При этом для получения коэффициентов деления, равных 13 и 14, входы элементов 6-2 и 6-3 блока 5 должны быть соединены с выходами триггеров регистра 1 в соответствии с фиг.2 и 3 соответственно.

При съеме информации с других точек делителя частоты могут быть получены дополнительные коэффициенты деления, отличные от приведенных в табл.2. В частности, для делителя частоты на 12, схема которого приведена на фиг.1, приводятся коэффициенты деления в различных точках схемы. Коэффициент деления: 1,5; 3; 6; 8; 12; 24. Выход элементов: 8-1; 8-2; 8-3; 8-4; 2-1; 6-3; 2-3; 2-4; 6-1; 4; 2-2; 8-8; 8-5; 8-6; шина 10.

На временной диаграмме напряжений в различных точках схемы, приведенной на фиг.4, цифрами обозначены номера элементов схемы фиг.1, на выходах которых наблюдаются соответствующие диаграммы напряжений при работе в режиме деления на 12.

Таким образом, совокупность признаков делителя частоты позволяет расширить функциональные возможности по сравнению с прототипом за счет реализации различных недвоичных коэффициентов деления в диапазоне от 2N-1 до 2N, а также за счет одновременной реализации дополнительных недвоичных коэффициентов деления.

Увеличение коэффициента деления относительно 2N-1 достигается путем организации необходимого количества переключений триггера первого разряда регистра. При этом число переключений триггеров за такт выходной частоты является минимальным и равно К-1, где К - коэффициент деления, что позволяет обеспечить необходимый уровень помехоустойчивости устройства за счет уменьшения вероятности сбоя триггеров, устойчивых к воздействию различного рода интенсивных внешних помех в режиме хранения информации, помехоустойчивость которых снижается во время действия счетного импульса.

Расширение функциональных возможностей достигается практически без усложнения схемы устройства. При этом известная схема блока запуска выполнена на двухвходовых элементах совпадения.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕЛИТЕЛЬ ЧАСТОТЫ | 1991 |

|

RU2036555C1 |

| Управляемый делитель частоты следования импульсов | 1989 |

|

SU1709515A1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1160560A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1547057A2 |

| Управляемый делитель частоты | 1982 |

|

SU1046936A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ТЕЛЕВИЗИОННЫХ СИГНАЛОВ | 1991 |

|

RU2014745C1 |

| МНОГОРАЗРЯДНЫЙ УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ | 1996 |

|

RU2119248C1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1997 |

|

RU2151463C1 |

ДЕЛИТЕЛЬ ЧАСТОТЫ, содержащий N - разрядный регистр, состоящий из триггеров, блок запуска, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и блок анализа четности, включающий в себя соединенные последовательно (N-1) элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, соответствующие входы которого соединены с прямыми выходами триггеров, начиная со второго, N - разрядного регистра и с управляющей шиной устройства, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с прямым выходом триггера первого разряда N - разрядного регистра, а каждый разряд блока запуска содержит первый и второй элементы совпадения, первые входы которых, кроме первого разряда, соединены с выходом первого элемента совпадения предыдущего разряда, первые входы элементов совпадения первого разряда соединены с шиной входной частоты, выход первого элемента совпадения N-го разряда соединен с шиной выходной частоты, выход второго элемента совпадения каждого разряда соединен со счетным входом триггера соответствующего разряда N-разрядного регистра, отличающийся тем, что, с целью расширения функциональных возможностей путем получения недвоичных коэффициентов деления, прямой и инверсный выходы триггера каждого разряда N-разрядного регистра со второго по (N-1)-й соединены со вторыми входами соответственно второго и первого элементов совпадения последующего разряда блока запуска, прямой и инверсный выходы блока анализа четности соединены со вторыми входами соответственно первого и второго элементов совпадения второго разряда блока запуска, вторые входы первого и второго элементов совпадения первого разряда которого соединены соответственно с инверсным и прямым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с прямым выходом триггера второго разряда N-разрядного регистра.

| РЕВЕРСИВНЫЙ СЧЕТЧИК ИМПУЛЬСОВ | 0 |

|

SU330554A1 |

Авторы

Даты

1995-03-20—Публикация

1983-10-05—Подача