Изобретение относится к области техники аналого-цифровых преобразователей (АЦП) и может быть использовано в информационных и управляющих вычислительных машинах для одновременного выполнения линейного и нелинейного функционального аналого-цифрового преобразования.

Известные АЦИ, содержащие регистр кода, преобразователь код-аналог, нуль-орган, блок управляющих импульсов, счетчик, дещифратор номера разряда, инвертор, логические схемы «И, «ИЛИ, работающие по методу поразрядного уравновешивания, которые осуществляют линейное преобразование непрерывной входной величины X в цифровой код Z по закону Z cX, где f - постоянный коэффициенг, имеют недостаточно широкие функциональные возможности.

В предлагаемом изобретении расширение функциональных возможностей прео-бразователя достигается тем, что он содержит последовательно включенные дешифратор матрицы, матрицу коэффициентов, сдвиговый регистр и накапливающий сумматор, причем т входов дешифратора матрицы подключены к выходам т старших разрядов регистра кода, (т4-1)-й вход дешифратора соединен с (т+1)-й шиной дешифратора номера разряда, выходы сдвигового регистра через вентили подключены к входам накапливающего сумматора, а т старщих шин дешифратора номера разряда соединены с входами первой схемы «ИЛИ, выход которой подключен к потенциальному входу первой схемы «И непосредственно и к погенциальному входу второй и третьей схем «И через инвертор, причем другой потенциальный вход второй схемы «И соединен с выходом нуль-органа, импульсные входы первой и второй схем «И объединены и подключены к выходу блока управляющих импульсов, другой вход которого соединен с импульсным входом третьей схемы «И, выход последней подключен к управляющему входу сдвигового регистра, а выходы первой и второй схем «И через вторую схему «ИЛИ соединены с управляющими входами вентилей.

Для получения требуемой функциональной зависимости y F(x) устройство осуществляет аппроксимацию исходной функции кусочно-линейной кривой. При этом диапазон изменения входной величины в «пределах , где Дд: - величина кванта, разбивается на 2™ равных по величине участков, нижние границы которых имеют значения Ai(, 2,..., 2). Величина m выбирается, исходя из допустимой погрешности аппроксимации.

Значение аппроксимирующей функции на г-м участке описывается формулой:

где Yi F(Xi) -значение функции в точке Хг;

bi - величина проекции i-ro участка на ось у.

Величина У, представлена в виде суммы постоянных для данной функции коэффициентов uij.

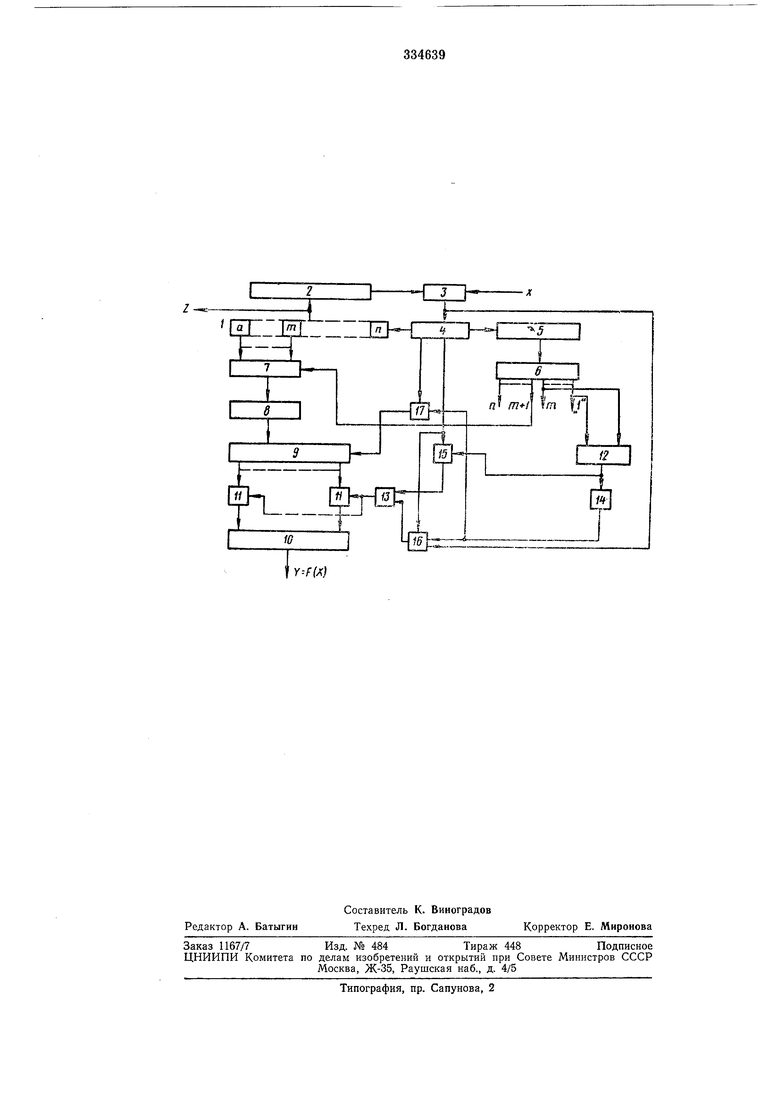

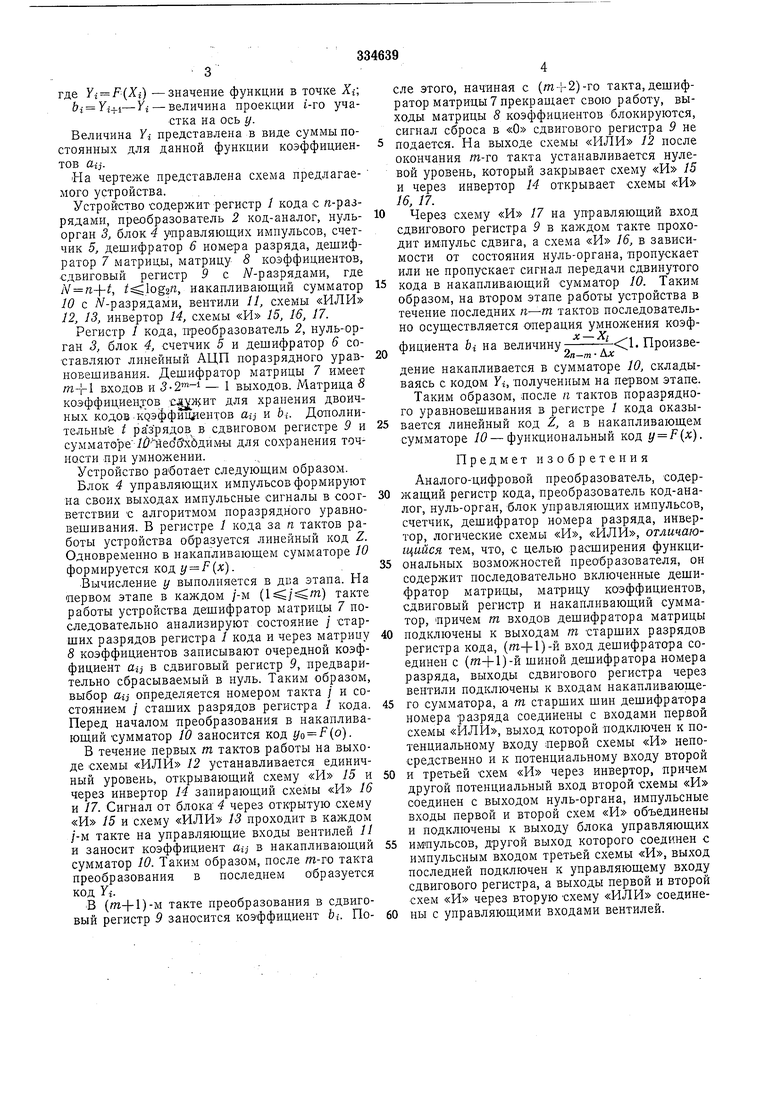

На чертеже представлена схема предлагаемого устройства.

Устройство содержит регистр / кода с tt-разрядами, преобразователь 2 код-аналог, нульорган сЗ, блок 4 управляющих импульсов, счетчик 5, дешифратор 6 номера разряда, дешифратор 7 матрицы, матрицу 8 коэффициентов, сдвиговый регистр 9 с //-разрядами, где N , f log2«, накапливающий сумматор 10 с Л/-разрядами, вентили 11, схемы «ИЛИ 12, 13, инвертор 14, схемы «И 15, 16, 17.

Регистр 1 кода, преобразователь 2, нуль-орган 3, блок 4, счетчик 5 и дещифратор 6 составляют линейный АЦП поразрядного уравновешивания. Дешифратор матрицы 7 имеет входов и 5-2™-1 - 1 выходов. Матрица 8 коэффициен.тов служит для хранения двоичных кодов кдэффиц центов ац и bi. Дополнительные t разрядов в сдвиговом регистре 9 и сумматореч/()- необхЬдимъ1 для сохранения точности при умножении.

Устройство работает следующим образом.

Блок 4 управляющих импульсов формируют на своих выходах импульсные сигналы в соогветствии С алгоритмом поразрядного уравновешивания. В регистре / кода за и тактов работы устройства образуется линейный код Z. Одновременно в накапливающем сумматоре 10 формируется код г/ /(л:).

Вычисление у выполняется в два этапа. На первом этапе в каждом /-м () такте работы устройства дешифратор матрицы 7 последовательно анализируют состояние / старших разрядов регистра 1 кода и через матрицу 8 коэффициентов записывают очередной коэффициент йц в сдвиговый регистр 9, предварительно сбрасываемый в нуль. Таким образом, выбор ац определяется номером такта / и состоянием / сташих разрядов регистра 1 кода. Перед началом преобразования в накапливающий сумматор 10 заносится код (о).

В течение первых m тактов работы на выходе схемы «ИЛИ 12 устанавливается единичный уровень, открывающий схему «И 15 и через инвертор 14 запирающий схемы «И 16 и 17. Сигнал от блока 4 через открытую схему «И 15 и схему «ИЛИ /5 проходит в каждом /-М такте на управляющие входы вентилей И и заносит коэффициент ац в накапливающий сумматор 10. Таким образом, после т-го такта преобразования в последнем образуется код Yi.

В (от+1)-м такте преобразования в сдвиговый регистр 9 заносится коэффициент Ь;. После этого, начиная с (т-г2)-го такта, дешифратор матрицы 7 прекрапхает свою работу, выходы матрицы 8 коэффициентов блокируются, сигнал сброса в «О сдвигового регистра 9 не подается. На выходе схемы «ИЛИ 12 после окончания /п-го такта устанавливается нулевой уровень, который закрывает схему «И 15 и через инвертор 14 открывает схемы «И 16, 17.

Через схему «И 17 на управляющий вход сдвигового регистра 9 в каждом такте проходит импульс сдвига, а схе.ма «И 16, в зависимости от состояния нуль-органа, пропускает или не пропускает сигнал передачи сдвинутого

кода в накапливающий сумматор 10. Таким образом, на втором этапе работы устройства в течение последних п-т тактов последовательно осуществляется операция умножения коэффициента bi на величину-- С1. Произве2л-ш &JC

дение накапливается в сумматоре 10, складываясь с кодом Yi, полученным на первом этапе. Таким образом, после п тактов поразрядного уравновешивания в регистре 1 кода оказывается линейный код Z, а в накапливающем сумматоре 10 - функциональный код y F(x).

Предмет изобретения

Аналого-цифровой преобразователь, содержащий регистр кода, преобразователь код-аналог, нуль-орган, блок управляющих импульсов, счетчик, дешифратор номера разряда, инвертор, логические схемы «И, «ИЛИ, отличающийся тем, что, с целью расширения функциональных возможностей преобразователя, он содержит последовательно включенные дешифратор матрицы, матрицу коэффициентов, сдвиговый регистр и накапливающий сумматор, причем от входов дешифратора матрицы

подключены к выходам т старших разрядов регистра кода, (т+1)-й вход дешифратора соединен с (т+1)-й шиной дешифратора номера разряда, выходы сдвигового регистра через вентили подключены к входам накапливающего сумматора, а от старщих шин дешифратора номера разряда соединены с входами первой схемы «ИЛИ, выход которой подключен к потенциальному входу первой схемы «И непосредственно и к потенциальному входу второй

и третьей схем «И через инвертор, причем другой потенциальный вход второй схемы «И соединен с выходом нуль-органа, импульсные входы первой и второй схем «И объединены и подключены к выходу блока управляющих

импульсов, другой выход которого соединен с импульсным входом третьей схемы «И, выход последней подключен к управляющему входу сдвигового регистра, а выходы первой и второй схем «И через вторую схему «ИЛИ соединены с управляющими входами вентилей.

y--fW

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1226664A1 |

| Цифровой знаковый коррелометр | 1980 |

|

SU962975A1 |

| Самонастраивающееся устройство управления | 1983 |

|

SU1130830A1 |

| ПРЕОБРАЗОВАТЕЛЬ НАПРЯЖЕНИЯ В КОД С САЛ1ОКОНТРОЛЕМ | 1973 |

|

SU379051A1 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1973 |

|

SU365830A1 |

| Устройство для вычисления спектра Фурье | 1983 |

|

SU1121678A1 |

| Устройство для определения координат объекта | 1990 |

|

SU1814196A1 |

Авторы

Даты

1972-01-01—Публикация