1

Изобретение относится к импульсной технике и может быть использовано для преобразования вида 1/ к:д;2 и у-..

Известны аналого-цифровые преобразователи (АЦП), содержащие регистр кода, преобразователь цифра-аналог, нуль-орган, генератор импульсов, распределитель, логические схемы «И и «ИЛИ.

Однако для осуществления функционального преобразования требуются дополнительные аналоговые блоки.

С целью расширения функциональных возможностей в предлагаемый преобразователь введены сдвиговый регистр, регистр квадратов, сумматор, коммутатор, причем выходы распределителя, начиная со второго, подключены через первые логические схемы «И ко входам четных разрядов сдвигового регистра и через логические схемы «ИЛИ - ко входам четных разрядов сумматора, другие входы логических схем «ИЛИ соединены с выходами четных разрядов регистров квадратов, выходы нечетных разрядов которого подключены к соответствующим разрядам сумматора, вторые входы последнего соединены с соответствующими выходами сдвигового регистора, а выходы через вторые логические схемы «И подключены ко входам регистра квадратов; одни входы коммутатора соединены с выходами сумматора, другие входы которого подключены к выходам регистра кода, а выходы - через преобразователь цифра-аналог соединены со входом нуль-органа, выход которого подключен ко вторым входам первых и вторых логических схем «И.

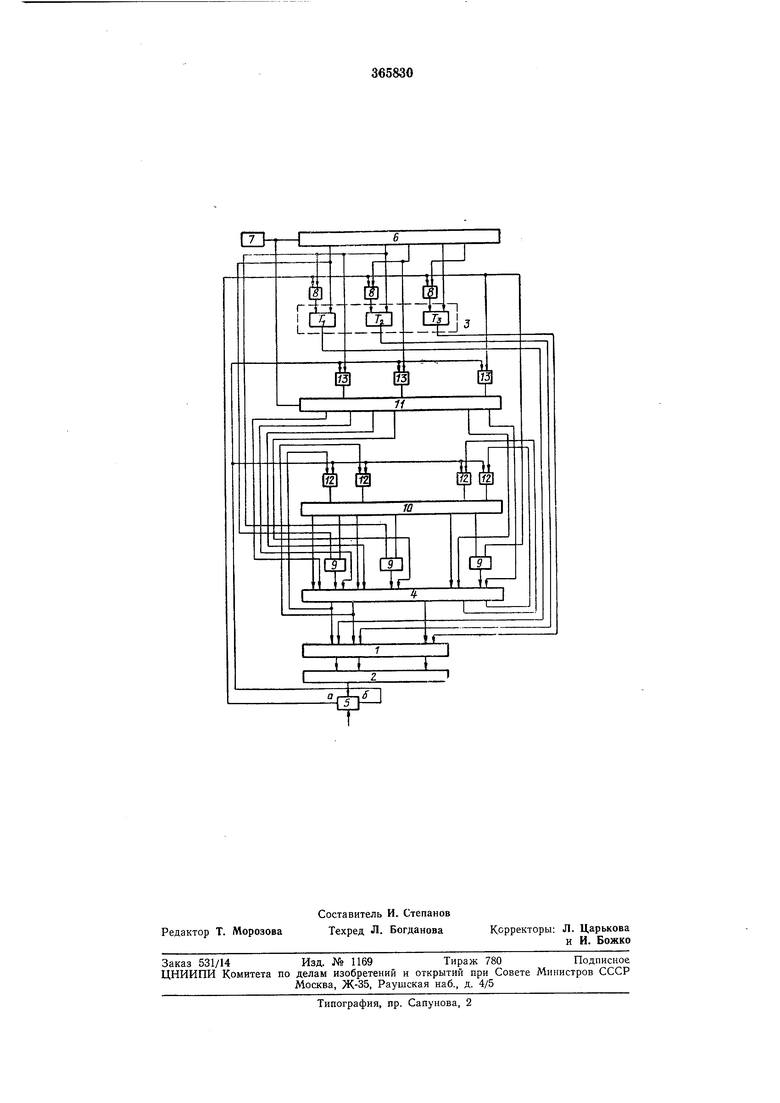

На чертеже приведена блок-схема предлагаемого преобразователя.

Для получения функционального кода вычисляют квадраты линейного кода на каждом шаге поразрядного уравновешивания по формуле

A, (A,i + B1) + ,

где Ai - значение линейного кода на i-ом шаге уравновешивания;

Bi Ai-Ai-i, т. е. значение кода, прибавляемого к линейному коду на i-ou шаге.

Сумма и В не дает переносов и может быть получена обычным логическим сложением на схемах «ИЛИ. Удвоенное произведение представляет собой Л,, сдвинутое на (i-1) разрядов вправо. Устройство работает следующим образом. Сигнал «Признак датчика управляет л-разрядным коммутатором /, пропуская на входы преобразователя 2 цифра-аналог линейный код с триггеров Ti-Г„ регистра 3 кода или квадратичный с п старших разрядов т-разрядного сумматора 4, где т - определяется требуемой точностью функционального

преобразования и может быть выбрана в пределах (п-1). В зависимости от принятого кода преобразователь 2 формирует линейное или функциональное компенсирующее напряжение UK для сравнения с измеряемой величиной Ux. Если , вырабатывается сигнал на выходе а нуль-органа 5, а если , вырабатывается сигнал на выходе б. Распределитель 6 управляющих импульсов, принимая импульсы с генератора 7 импульсов, записывает в триггера регистра 3 кода поочередно «1, начиная со старшего разряда. Получаемые коды на каждом шаге поразрядного уравновешивания через «-разрядный коммутатор / поступают на преобразователь 2, с выхода которого (/к поступает на нуль-орган 5 для сравнения с Us. Если UX.UK, то сигнал с выхода а нуль-органа 5 через схемы 5 «И сбрасывает триггер Ti в «О. Если , то триггер Ti остается в «1. Таким образом, на последнем шаге поразрядного уравновешивания в триггерах Ti-Тп регистра 3 формируется линейный код. Одновременно с линейным формируется код, равный квадрату линейного.

К моменту начала оцифровки устройство находится в нулевом состоянии. Сигнал с первого выхода распределителя 6 через схему «ИЛИ 9 поступает на вход т-разрядного сумматора 4, где суммируется с нулевыми значениями т-разрядного регистра 10 квадратов и от-разрядного сдвигового регистра 11, т. е. в сумматоре 4 получаем квадрат первого значения уравновешиваемого линейного кода.

В зависимости от результата сравнения Ux и UK, если , тогда по сигналу с выхода б нуль-органа 5 содержимое сумматора 4 перезаписывается в регистр 10 квадратов через вторые логические схемы «И 12 и запись «1 во второй разряд сдвигового регистра // через первые логические схемы «И 13 сразу после выполнения сдвига. Если , тогда по сигналу с выхода а нуль-органа 5 сбрасывается триггер Ti регистра 3 линейного кода.

На каждом шаге поразрядного уравновешивания в /п-разрядном сдвиговом регистре // формируется и хранится удвоенное произведение для сложения в сумматоре 4 с суммой

квадратов, которая формируется логическим сложением г-го выхода распределителя 6 с 2г-ным разрядом регистра 10 квадратов, в котором хранится квадратичный код предыдушего шага уравновешивания.

При преобразовании линейной и функциональной величины вида на вход,преобразователя 2 цифра-аналог поступает код с триггеров Ti-Г„ регистра 3, результат снимается с регистра 3 в первом случае и с регистра 10 квадратов во втором случае.

При преобразовании функциональной величины вида на входы преобразователя 2

цифра-аналог поступает код с сумматора 4, а результат снимается с линейного регистра 3.

Предмет изобретения

Аналого-цифровой преобразователь, содержащий регистр кода, преобразователь цифрааналог, нуль-орган, генератор импульсов, распределитель, логические схемы «И, «ИЛИ, отличающийся тем, что, с целью расширения

функциональных возможностей устройства, в него введены сдвиговый регистр, регистр квадратов, сумматор, коммутатор, причем выходы распределителя, начиная со второго, подключены через первые логические схемы «И ко

входам четных разрядов сдвигового регистра и через логические схемы «ИЛИ - ко входам четных разрядов сумматора, другие входы логических схем «ИЛИ соединены с выходами четных разрядов регистра квадратов, выходы

нечетных разрядов которого подключены к соответствующим разрядам сумматора, вторые входы последнего соединены с соответствуюшими выходами сдвигового регистра, а выходы через вторые логические схемы «И подключены ко входам регистра квадратов; одни входы коммутатора соединены с выходами сумматора, другие входы которого подключены к выходам регистра кода, а выходы - через преобразователь цифра-аналог соединены

со входом нуль-органа, выход которого подключен ко вторым входам первых и вторых логических схем «И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1985 |

|

SU1290307A1 |

| Устройство для деления чисел в форме с плавающей запятой | 1988 |

|

SU1566340A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1972 |

|

SU334639A1 |

| Преобразователь кода системы остаточных классов в позиционный код | 1983 |

|

SU1116424A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

| Многоканальный преобразователь угла поворота вала в код | 1980 |

|

SU947895A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

Даты

1973-01-01—Публикация