Изобретение относится к вычислительной технике и предназначено для вычисления по известным кодам прямоугольных координат измеряемой величины кодов ее полярных координат,

Цель изобретения - повьшение точности и быстродействия цифрового преобразователя координат.

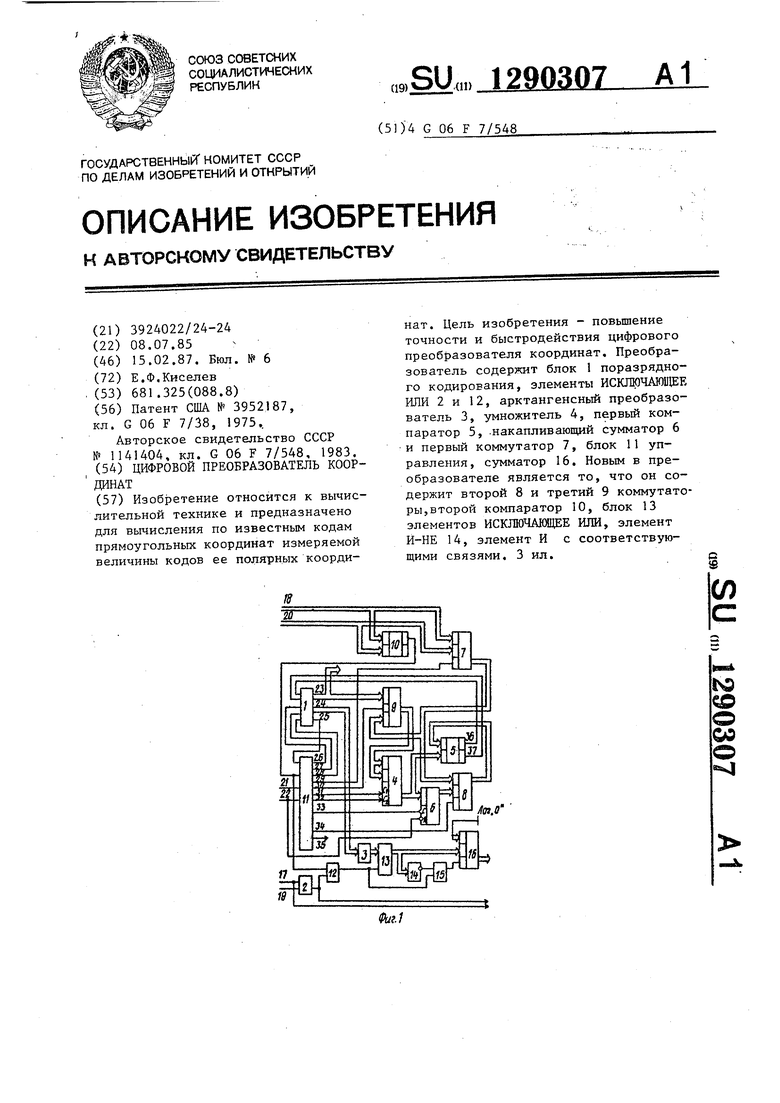

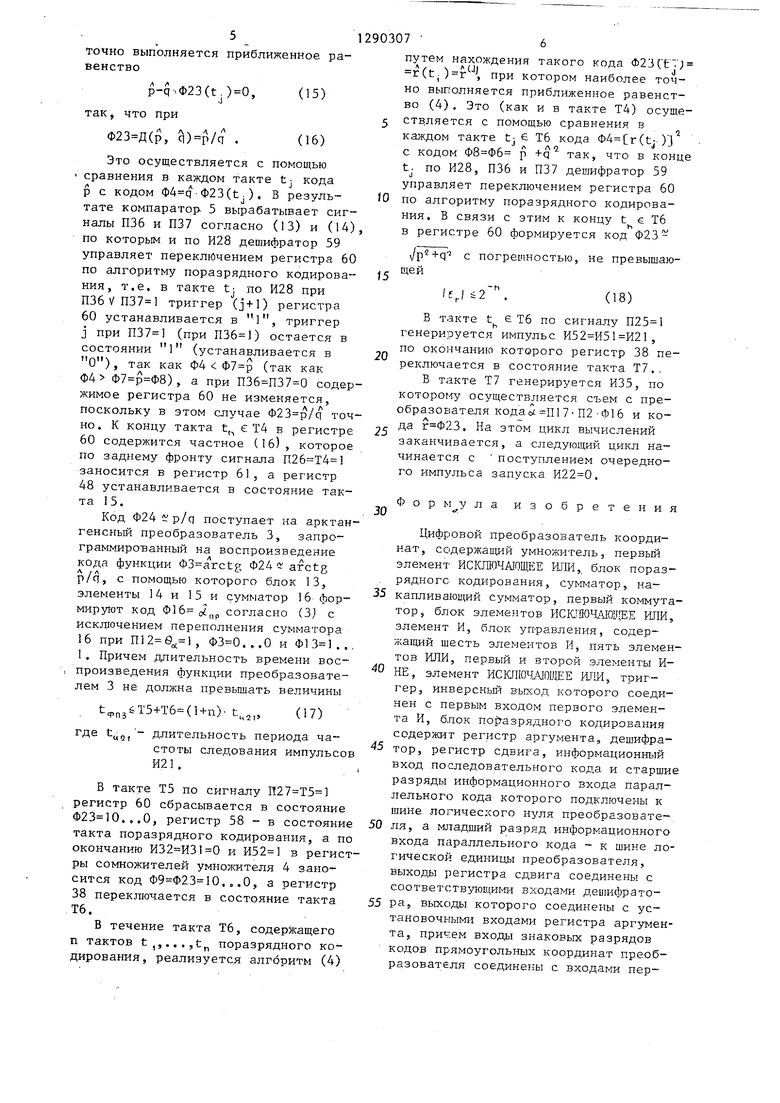

На фиг, 1-3 приведена функциональная схема предлагаемого преобразова- теля координат.

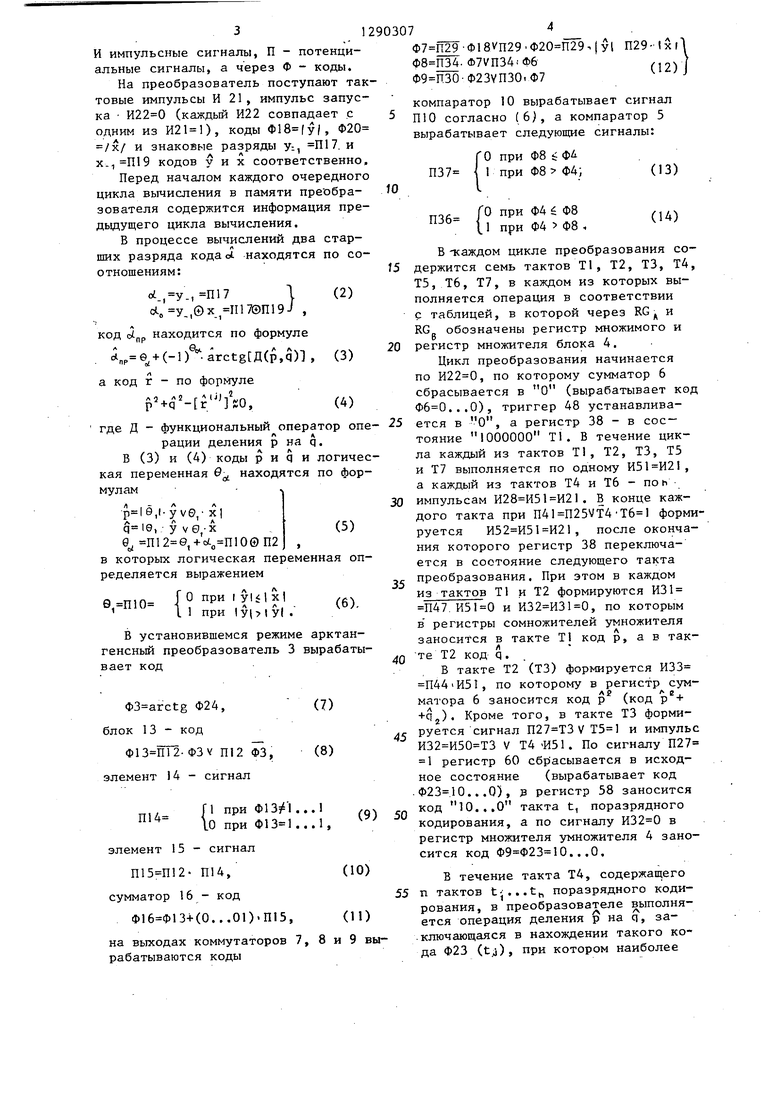

Преобразователь (фиг. 1) содержит блок 1 поразрядного кодирования, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 2, арктангенсный преобразователь 3, за- программированньш на воспроизведение арктангенса, умножитель 4, первый компаратор 5, накапливающий сумматор 6, первый 7, второй 8 и третий 9 коммутаторы, второй компаратор 10, блок 11 управления, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, блок 13 элементов .ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И-НЕ 14, элемент И 15, сумматор 16, вход 7 знакового разряда и вход 18 кода модуля первой прямоугольной координаты, вход 19 знакового разряда на вход 20 кода модуля второй прямоугольной координаты, вход 21 тактовый, вход 22 запуска, первый 23 и второй 24 кодо- вые выходы и управляЕощий выход 25 блока 1, выходы 26-35 блока 11 и управляющие выходы 36 и 37 компаратора 5.

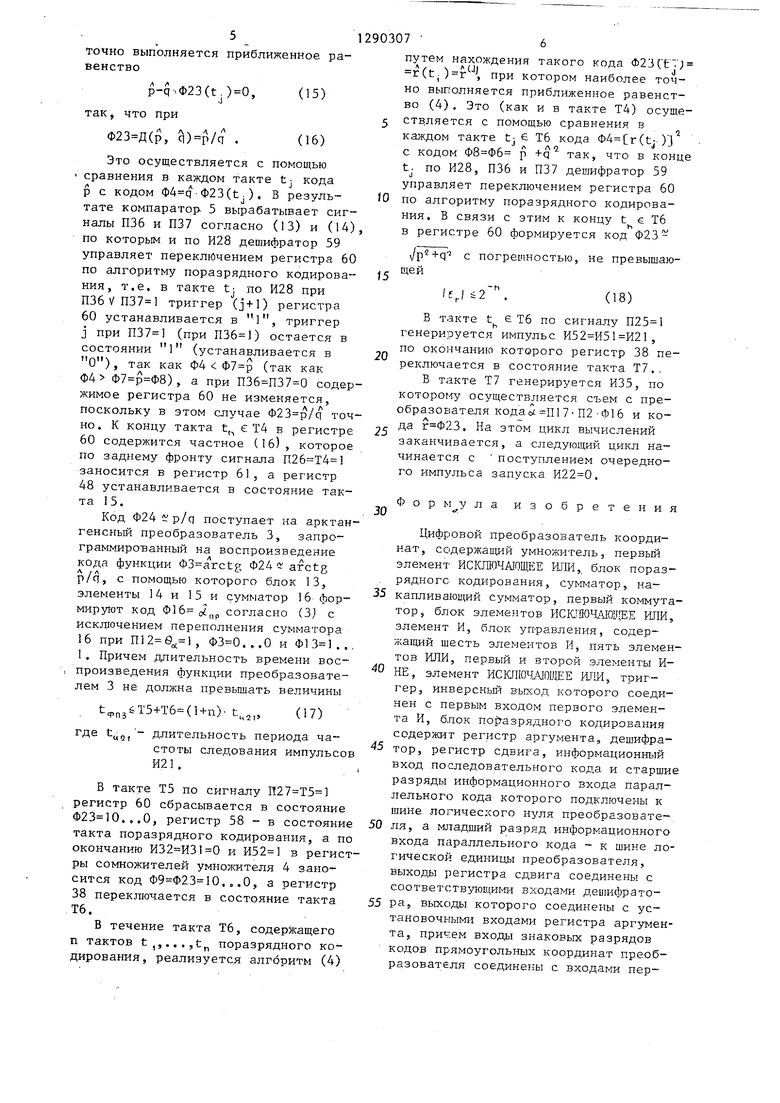

Блок 11 (фиг. 2) содержит сдви- говый регистр 38, первый 39 и второй 40 инверторы, элементы ИЛИ 41-47 с первого по седьмой, триггер 48,первый 49 и второй 50 элементы И-НЕ, элементы И 51-56 с первого по шестой и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 57.

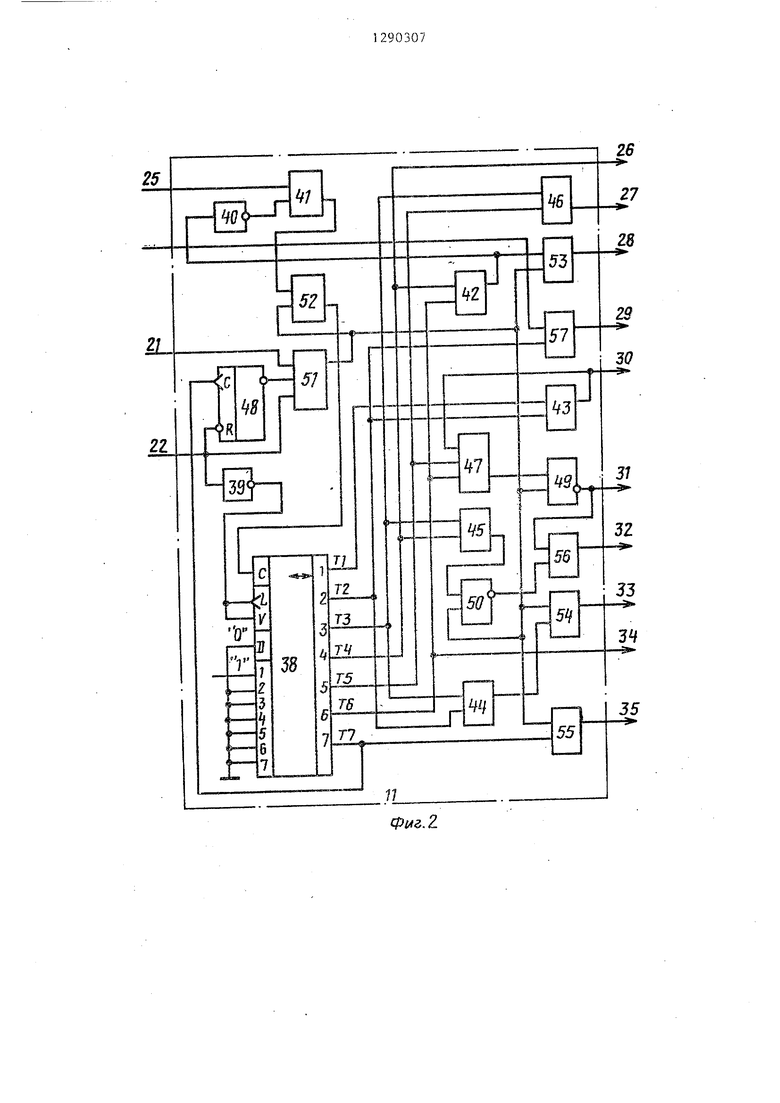

Блок 1 поразрядного кодирования (фиг, 3) содерлсит сдвиговый регистр 58 такта поразрядного кодирования, дешифратор 59, .регистр 60 кода по- разрядного кодирования и регистр 61 результата операции деления.

Предлагаемый преобразрватель выполнен на интеграль 1ых схемах (ИС) серий 133, 533, 556 и 1802 для .

Каждый из коммутаторов 7, 8 и 9 выполнен на трех ИС 533КП11, а каждый из компараторов 5 и 10 - на трех ИС 533СП1.

Умножитель 4 представляет собой ИС 1802ВР4 и содержит регистр множимого, регистр множителя,триггер округления, блок умножения, сдвига- тель, регистр произведения, выходные

буферные усилители, входы записи информации в регистры и управляющие входы (на фиг. 1 не показаны),на которые поданы сигналы, обеспечива- ютщле работу умножителя 4 по .модулям сомно;кителей и комбинационную выдачу произведения с округлением от блока умножения.

Арктангенсный преобразователь 3 выполнен по схеме комбинационного кусочно-линейного функционального преобразователя информации и запрограммирован на воспроизведение по п- разрядному коду аргумента, изменяющемуся от О до 1-2 7 п-разрядного кода арктангенса с весом младшего разряда 2 .11/2.

При этом запись информации в память умножителя 4 производится по положительным фронтам сигналов, действующих на его входах записи, а запись информации в регистр сумматора 6, регистры 38, 58 и 61, сдвиг вправо каждого из регистров 38 и 58 и переключение триггера 48 из О в 1 осуществляются почотражательным фронтам сигналов (по изменениям сигналов с 1 в О), действуюиих на их синхронизируюЕтих входах.

Предлагаемый преобразователь работает циклически я в каждом цикле по (п-1-1)-разрядным кодам у (-1 )

у. и X ( i) -f:2 X; (где . : 1

(у-1) и (х-1) - разрядные цифры знаковых разрядов кодов у и х соответственно) вычисляет сначала (п+2)- разрядный код d. , а затем п-разрядгде у.

и

ный код г)2 1

i-1 , Tj - разрядные цифры 1-го разряда кода у,, X и f соответственно.

Связь между кодом ы и углом характеризуется выражением

-т::2 - - I (.,+о1„4с1,р);

(1)

; 2

разрядные цифры старших разрядов кода оГ; разрядная цифра i-ro ( ,0, 1 ,,, . ,п) разряда кода ы ;

код приведенного угла 7i

cf-nf )

на входах и ВЕ)1ходах преи его составных через

И импульсные сигналы, П - потенциальные сигналы, а через Ф - коды.

На преобразователь поступают тактовые импульсы И 21, импульс запуска (каждый И22 совпадает с одним из ), коды Ф18(у/, Ф20 /х/ и знаковые разряды у, П17. и кодов у и X соответственно.

Перед началом каждого очередного цикла вычисления в памяти преобразователя содержится информация предыдущего цикла вычисления.

В процессе вычислений два старших разряда кода ot находятся по соотношениям:

oi.,y-,ni7 ,©х,П17©П19

}

(2)

код oi находится по формуле

ч

, + (-1) arctg fl(p,q)l, (3)

(4)

а код г - по формуле ,

где Д - функциональный оператор one-

рации деления р на q. В (3) и (4) коды р и q и логическая переменная в находятся по формулам

Q,l- у ve, х1

. У ve,-x(5)

0 , + сЛ„ П100П2 в которых логическая переменная определяется выражением

в,п10 1° Р .

L 1 при 1у(|у( .

В установившемся режиме генсный преобразователь 3 вает код

Ф3 агс1§ Ф24, блок 13 - код

. ФЗУ П12 ФЗ, элемент 14 - сигнал

П14

1 при ...1 10

при ... 1, элемент 15 - сигнал

П14,

сумматор 16 - код

(0...01).П15,

на выходах коммутаторов 7, 8 рабатываются коды

Ф7 П29Ф18Vn29Ф20 П29.(уI П29- Iх( . Ф7УП34|Ф6,.„.

Ф9 ПЗО-Ф23УПЗО.Ф7

компаратор 10 вырабатывает сигнал П10 согласно (6), а компаратор 5 вырабатывает следующие сигналы:

Ю7П36

О при Ф8 t Ф4 I при Ф8 Ф4;

V.

Го при Ф4 Ф8

и

при Ф4 Ф8

(13)

(14)

15

20

e- 25

с30

35

40

45

9) 50

)

55

)

ыБ тсаждом цикле преобразования содержится семь тактов Т1, Т2, ТЗ, Т4, Т5, Т6, Т7, в каждом из которых выполняется операция в соответствии с таблицей, в которой через RG j и RG обозначены регистр множимого и регистр множителя блока 4.

Цикл преобразования начинается по , по которому сумматор 6 сбрасывается в О (вырабатывает код ...0), триггер 48 устанавливается в О, а регистр 38 - в состояние 1000000 Т1. В течение цикла каждый из тактов Т1, Т2, ТЗ, Т5 и Т7 выполняется по одному , а каждый из тактов Т4 и Т6 - поh импульсам . В конце каждого такта при П41 П25УТ4 16 1 формируется , после окончания которого регистр 38 переключается в состояние следующего такта преобразования. При этом в каждом из тактов Т1 и Т2 формируются И31 П47. и , по которым в регистры сомножителей умножителя заносится в такте Т1 код р, а в так- те Т2 код q.

В такте Т2 (ТЗ) формируется И33 n44iH5I, по которому в регистр сумматора 6 заносится код р (код +qj). Кроме того, в такте ТЗ формируется сигнал Т5 и импульс V Т4 И51. По сигналу П27 1 регистр 60 сбр асывается в исходное состояние (вырабатывает код ...0), э регистр 58 заносится код 10...О такта t, поразрядного кодирования, а по сигналу в регистр множителя умножителя 4 заносится код ...0.

В течение такта Т4, содержащего и тактов t--...t поразрядного кодирования, в преобразователе выполняется операция деления р на q, за- ключающаяся в нахождении такого кода Ф23 (tj), при котором наиболее

точно выполняется приближенное равенство

(t.)0, (15)

J

так, что при

(р, ci) . (16)

Это осуществляется с помощью сравнения в каждом такте tj кода

р с кодом (йi). В резуль-

J

тате компаратор 5 вырабатывает сигналы П36 и ПЗУ согласно (13) и (14) по которым и по И28 дешифратор 59 управляет переключением регистра 60 по алгоритму поразрядного кодирова- ния, т.е. в такте tj по И28 при П36УП37 1 триггер (j+1) регистра 60 устанавливается в 1, триггер j при (при П36) остается в состоянии (устанавливается в О), так как ФА (так как Ф4 ), а при содержимое регистра 60 не изменяется, поскольку в этом случае Ф23 р/с| точно. К концу такта t, е Т4 в регистре 60 содержится частное (16), которое по заднему фронту сигнала заносится в регистр 61, а регистр 48 устанавливается в состояние такта 15.

Код Ф24 г; p/q поступает на арктан генсный преобразователь 3, запрограммированный на воспроизведение кода функции 03 arctg Ф24 arctg p/q, с помощью которого блок 13, элементы 14 и 15 и cyм iaтop 16 фор

мируют код согласно (3) с исключением переполнения сумматора 16 при ), ...0 и Ф13.,, 1. Причем длительность времени воспроизведения функции преобразователем 3 не должна превышать величины

t,,6T5+T6-(l+n)- t,,,.

(17)

где ty,j, - длительность периода частоты следования импульсов И2,

В такте Т5 по сигналу регистр 60 сбрасывается в состояние .,.0, регистр 58 - в состояние такта поразрядного кодирования, а по окончанию и в регистры сомножителей умножителя 4 заносится код ,.0, а регистр 38 переключается в состояние такта Т6.

В течение такта Т6, содержащего п тактов t,,...,t поразрядного ко дирования, реализуется алгоритм (4)

путем нахождения такого кода Ф23(. ; r(t.)f { при котором наиболее точно выполняется приближенное равенство (4). Это (как и в такте Т4) осуществляется с помощью сравнения в

2

ка}кдом такте tj е Т6 кода (1 )3 с кодом р +q так, что в конце t. по И28, П36 и П37 дешифратор 59

J

управляет переключением регистра 60 по алгоритму поразрядного кодирования, В связи с этим к концу t е Т6 в регистре 60 формируется код -f-q щей

с погрешностью, не превыш-аюf / 2

(18)

В такте t е Т6 по сигналу

о

генерируется импульс , по окончанию которого регистр 38 переключается в состояние такта Т7,, В такте Т7 генерируется И35, по которому осуществляется съем с преобразователя кодаы П1 7- П2 Ф16 и кода , На этом цикл вычислений заканчивается, а следующий цикл начинается с поступлением очередного импульса запуска ,

Формула изобретения

Цифровой преобразователь координат , содержацщй умножитель, первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ,, блок поразрядного кодирования, сумматор, накапливающий сумматор, первый коммутатор, блок элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент И, блок уп-равления, содержащий шесть элементов И, пять элементов ИЛИ, первый и второй элементы ИНЕ, элемент ИСКЛЮЧ УОЩЕЕ ИЛИ, триггер, инверсный выход которого соединен с первым входом первого элемента И, блок по газрядного кодирования содержит регистр аргумента, дешифратор, регистр сдвига, информационный вход пО Сшедовательного кода и старшие разряды информационного входа параллельного кода которого подключены к шине логического нуля преобразователя, а младший разряд информационного входа параллельного кода - к шине логической eдинип з преобразователя, выходы регистра сдвига соединены с соответствующими входами дешифратора, выходы которого соединены с установочными входами регистра аргумента, причем входы знаковых разрядов кодов прямоугольных координат преобразователя соединены с входами первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, тактовый вход и вход запуска преобразователя соединены с вторым входом первого элемента И и входом установки триггера и объединен с третьим входом первого элемента И блока управления соответственно, выход блока элементов ИСКЛЮЧАЮиДЕЕ ИЛИ соединен с входом первого слагаемого сумматора, вход второго слагаемого сумматора подключен к шине логического нуля преобразователя, вход перноса сумматора соединен с выходом элемента И преобразователя, отличающийся тем, что, с целью повышения быстродействия, он содержит второй и третий коммутаторы, первую и вторую схемы сравнения, арктангенсный преобразователь, второй элемент ИСКШОЧАЮЩЕЕ ИЛИ, элемент И-НЕ, а блок управления дополнительно содержит регистр сдвига, два элемента ИЛИ, два элемента НЕ, а блок поразрядного кодирования дополнительно содержит регистр результата, входы кодов модулей первой и второй прямоугольных координат соединены с первыми и вторыми информационными входами первого коммутатора и первой схемы сравнения соответственно, выход Больше которой соединен с первыми входами второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ блока управления и второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ преобразователя, выход первого коммутатора соединен с первыми информационными входами второго и третьего коммутаторов, выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вход знакового разряда кода первой прямоугольной координаты преобразователя соединен с выходами старших разрядов кода угла преобразователя,выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с вторым входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом блока элементов ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом элемента.И преобразователя второй вход которого соединен с выходом элемента И-НЕ преобразователя, входы которого соединены с выходами блока элементов ИСКЛЮЧАЮЩЕЕ РШИ, второй вход которого соединен с выходом арктангенсного преобразователя, информационный вход которого подключен к выходу регистра результата блока поразрядного кодирования, выход регистра аргумента

0

5

0

5

0

5

0

5

0

5

которого соединен с выходом кода модуля полярного радиуса преобразователя и с вторым информационным входом второго коммутатора, выход которого соединен с входами множи- мого и множителя умножителя, входы разрешения записи множителя и множимого которого соединены с выходами первого элемента И-НЕ и второго элемента И блока управления соответственно, выход умножителя соединен с информационным входом второй схемы сравнения, второй информационный вход третьего коммутатора соединен с выходом накапливающего сумматора, управляющий вход третьего коммутатора соединен с первым выходом регистра сдвига блока управления, выход третьего комтчутатора соединен с вто- ры1-1 информационным входом второй схемы сравнения, выходы Больше и Меньше которой соединены с соответствующими входами дешифратора блока поразрядного кодирования, выход которого соединен с первым входом первого элемента ИЛИ блока управления, второй выход регистра сдвига и выход второго элемента ИЛИ блока управления соединены соответственно с входом разрешения записи регистра результата и с соответствующим входом дешифратора, выход тре- -тьего элемента И блока управления соединен с установочным входом регистра сдвига и соответствующим входом дешифратора блока поразрядного кодирования, выходы элемента ИСКЛЮ- ЧАЮ01ЕЕ РШИ и третьего элемента ИЛИ блока управления соединены с управляющими входами первого и второго коммутаторов соответственно, выходы четвертого и пятого элементов И блока управления соединены с входом разрешения записи накапливающего сумматора, с выходом импульса конца цикла преобразования преобразователя, выходы сумматора соединены с выходами младших разрядов кода угла преобразователя, шина кода 10...О и шина логического нуля преобразователя подключены к информационным входам.и входам последовательного кода сдвигового регистра блока управления соответственно, первьй выход регистра сдвига блока управления соединен с первыми входами четвертого и пятого элементов ИЛИ блока управления, второй выход регистра сдвига блока управления соединен с

9

первым входом шестого элемента ИЛИ и вторым входом четвертого элемента ИЛИ блока управления, третий и четвертый вьшоды регистра сдвига блока управления соединены с первым входом третьего элемента ИЛИ и с вторыми входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и третьего элемента ИЛИ, с первым входом седьмого элемента ИЛИ соответственно блока управления, пятый выход сдвигового регистра блока управления соединен с вторыми выходами шестого и седьмого элементов ИЛИ и первым входом второго элемента ИЛИ блока управления, шестой и седьмой выходы сдвигового регистра блока управления соединены с вторыми входами второго и пятого элементов ИЛИ и с первым входом пятого элемента И, счетным входом триггера блока управления соответственно, вход запуска преобразователя через первый элемент НЕ соединен с входом установки сдвигового регистра блока управления, счетный вход которого соединен с выходом шестого элемента И блока управления, выход первого элемента И блока управления соединен с первыми входами третьего, четвертого, шестого элементов И, вторым входом

9030710

пятого элемента И и первыми входами первого и второго элементов И-НЕ блока управления, выход второго элемента И-НЕ блока управления соединен

5 с вторым входом второго элемента И блока управления, выход четвертого элемента ИЛИ блока управления соединен с вторым входом третьего элемента И и через второй элемент НЕ - с

fO вторым входом первого элемента ИЛИ блока управления, выход третьего элемента ила блока управления соединен с третьим входом пятого элемента ИЛИ блока управления, выход которого сое15 динен с вторым входом первого элемента И-НЕ блока управления, выход которого соединен с первым входом второго элемента И блока управления, второй вход которого соединен с вы20 ходом второго элемента И-НЕ блока

управления, второй вход которого соединен с выходом шестого элемента ИЛИ блока управления, выход седьмого элемента ИЛИ-соединен с вторым входом

25 четвертого элемента И, выход первого элемента ИЛИ блока управления соединен с вторым входом шестого элемента И блока управления, выходы регистра аргумента блока поразрядного ко30 дирования соединены с информационны- ми входами регистра результата.

Ф1.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Цифровой преобразователь координат | 1977 |

|

SU742944A1 |

| Цифровой преобразователь координат | 1979 |

|

SU873239A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Устройство для деления | 1990 |

|

SU1746378A1 |

| Цифровой преобразователь тригонометрических функций | 1986 |

|

SU1327094A1 |

| Устройство для деления | 1990 |

|

SU1728860A1 |

| Цифровой преобразователь координат | 1979 |

|

SU842801A1 |

| Цифровой преобразователь координат | 1985 |

|

SU1257638A1 |

| Цифровой преобразователь полярных координат в прямоугольные координаты | 1987 |

|

SU1441390A1 |

Изобретение относится к вычислительной технике и предназначено для вычисления по известным кодам прямоугольных координат измеряемой величины кодов ее полярных координат. Цель изобретения - повышение точности и быстродействия цифрового преобразователя координат. Преобразователь содержит блок 1 поразрядного кодирования, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 2 и 12, арктангенсный преобразователь 3, умножитель 4, первый компаратор 5, .накапливающий сумматор 6 и первый коммутатор 7, блок 11 управления, сумматор 16. Новым в преобразователе является то, что он содержит второй 8 и третий 9 коммутаторы, второй компаратор 10, блок 13 элементов ИСКЛЮЧАЩЕЕ ИЛИ, элемент И-НЕ 14, элемент И с соответствующими связями. 3 ил. (Л с:

Составитель З.Шершнева Редактор М.Дылын Техред Л.Олейиик

Заказ 7902/46 Тираж 673 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4

Фиг.З

Корректор r.PeLUBTHHK

| Патент США № 3952187, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой преобразователь координат | 1983 |

|

SU1141404A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-02-15—Публикация

1985-07-08—Подача