Изобретение относится к области техники связи и вычислительной техники.

Известны устройства для декодирования двоичных циклических кодов Хэмминга, исправляющих одиночные ошибки, содержащие регистры сдвига, сумматор по модулю 2 и логические элементы.

Недостатками таких устройств являются аппаратурная избыточность и сложность базисных элементов.

Цель изобретения - повышение надежности и упрощение схемы устройства.

Предлагаемое устройство дает возможность исправить единичную ошибку самого устройства при выдаче информации с выходного разряда регистра сдвига.

Декодирующая способность устройства основывается на использовании произвольного проверочного соотношения циклических кодов Хэмминга, имеющего вид: 2@ ai/ii 0, где 2@-означает суммирование по модулю два, а ai; /ii 0; 1.

Кодовый вектор циклического кода (, 2™-т-1) содержит серию из нулей, имеющих длину не более, чем m-1.

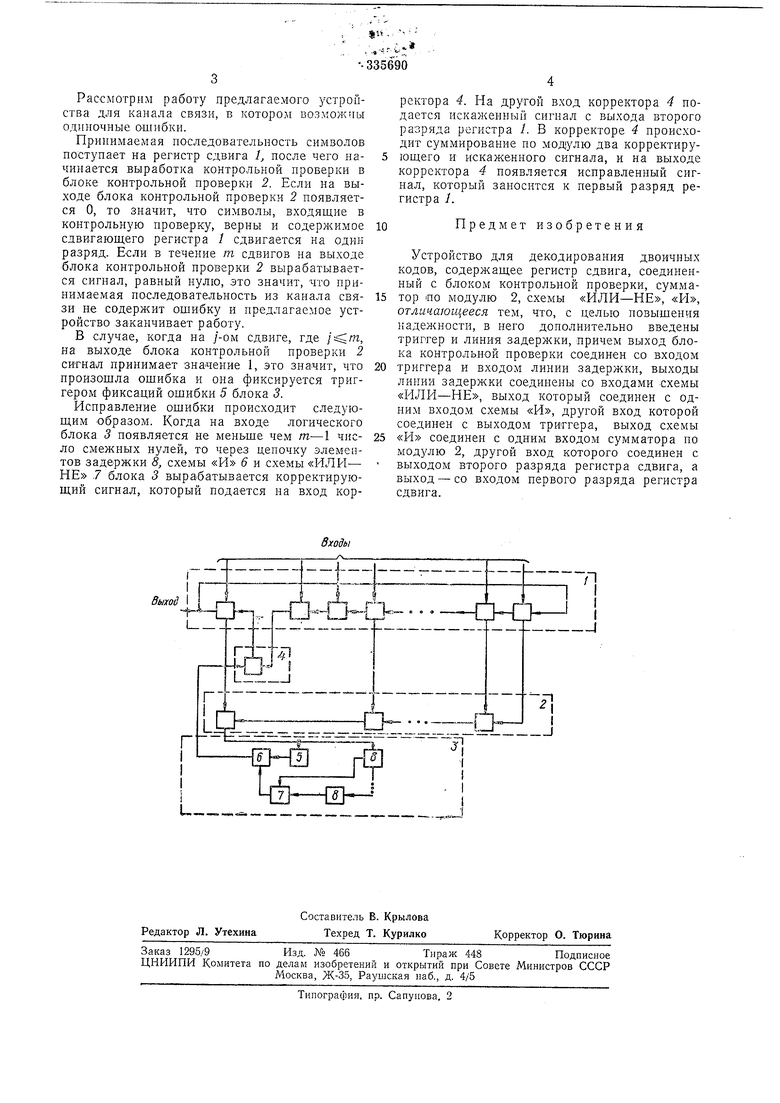

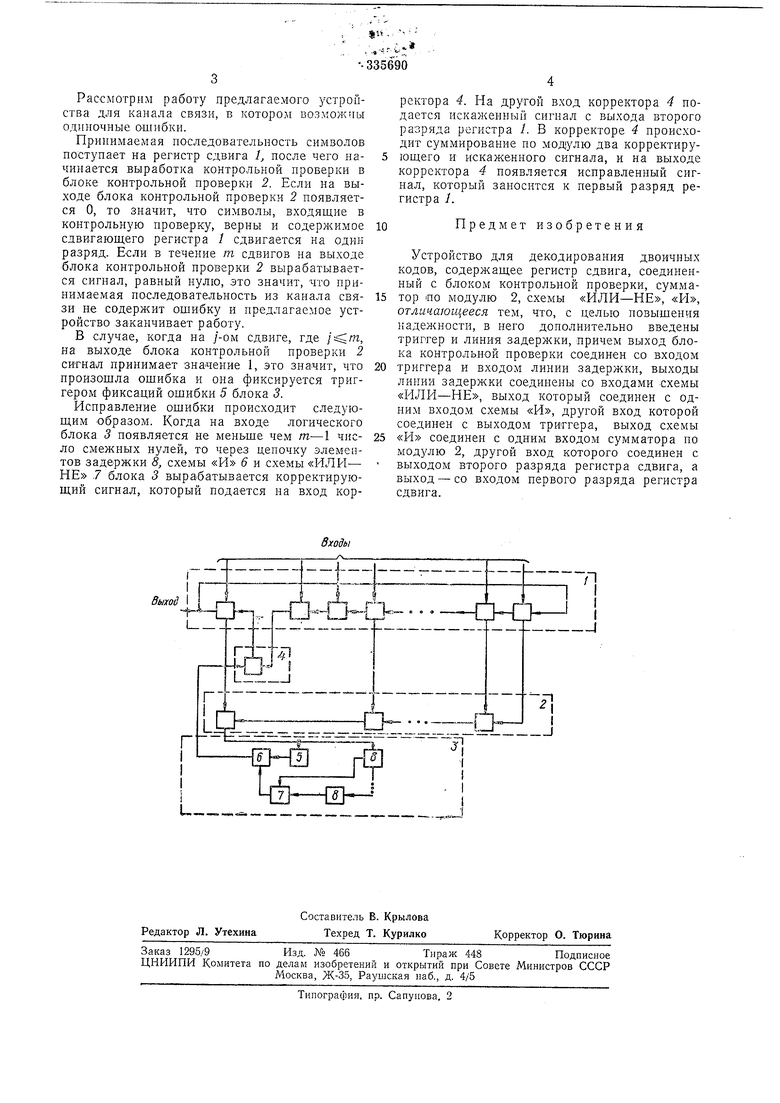

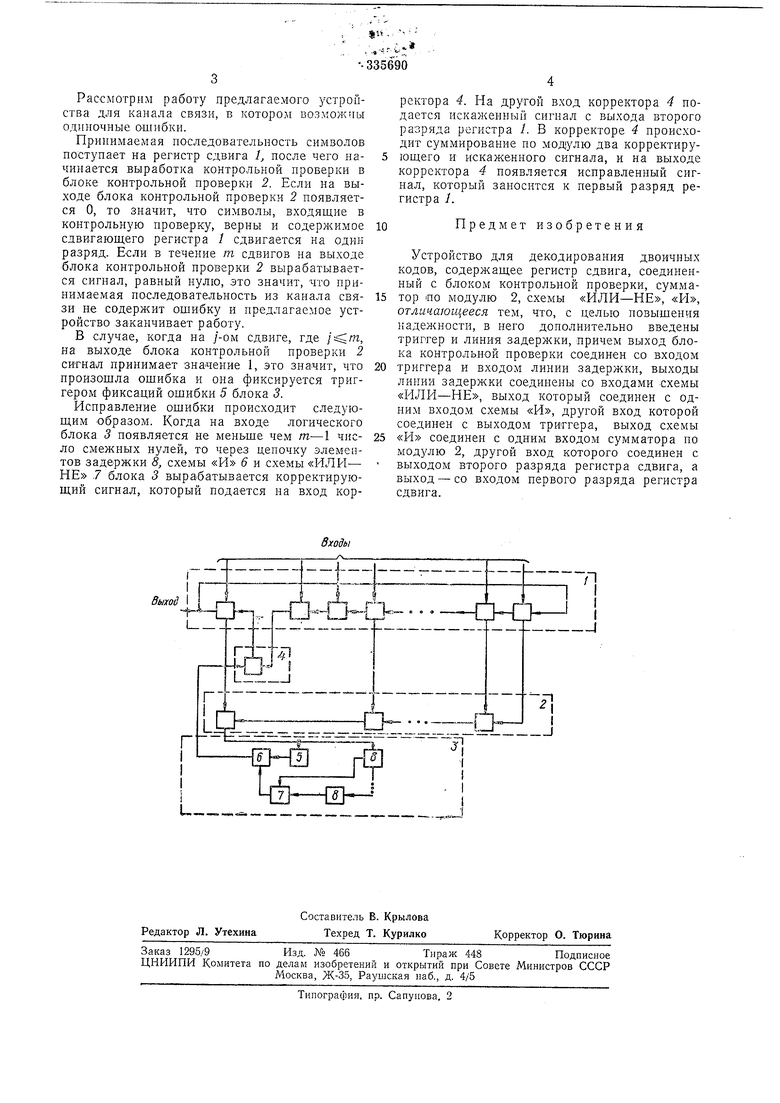

Устройство для декодирования двоичных кодов Хэмминга содержит сдвигающий регистр /, блок контрольной проверки 2, логический блок 3 и корректор 4. Логический

блок 3 содержит триггер фиксаций ошибки 5, логическую схему «И 6, логическую схему «ИЛИ-НЕ 7 и цепочку элементов задержки 8.

Сдвигающий регистр 1 соединен со входами йлока контрольной проверки 2, выход которого соединен со входом логического блока 3. Выход последнего соединен с одним входом корректора 4, ко второму входу которого подключен выход второго разряда сдвигающего регистра /. Выход корректора 4 соединен со входом первого разряда регистра /.

Вход логического блока 3 подключен ко входаА триггера фиксаций ошибки 5 и цепочки элементов задержки 8. Единичный выход триггера фиксаций ошибки 5 подключен к первому входу схемы .«ИЛИ 6. Выходы цепочки элементов задержки 8 подключены ко входам схемы «ИЛИ-НЕ 7, выход которой

подключен ко второму входу схемы «И. Выход схемы «И служит выходом блока 3.

Рассмотрим работу предлагаемого устройства для канала связи, в котором возможны одиночные ошибки.

Принимаемая иоследовательность символов поступает на регистр сдвига 1, носле чего начинается выработка контрольной проверки в блоке контрольной проверки 2. Если на выходе блока контрольной проверки 2 появляется О, то значит, что символы, входящие в контрольную проверку, верны и содержимое сдвигающего регистра / сдвигается на один разряд. Если в течение т сдвигов на выходе блока контрольной проверки 2 вырабатывается сигнал, равный нулю, это значит, что прини.маемая последовательность из канала связи не содерн ит ошибку и предлагаемое устройство заканчивает работу.

В случае, когда на /-ом сдвиге, где , на выходе блока контрольной проверки 2 сигнал принимает значение 1, это значит, что произощла ощибка и она фиксируется триггером фиксаций ощибки 5 блока 3.

Исправление ощибки происходит следующим образом. Когда на входе логического блока 5 появляется не меньще чем т-1 число смежных нулей, то через цепочку элементов задержки 8, схемы «И 6 и схемы «ИЛР1- НЕ 7 блока 3 вырабатывается корректирующий сигнал, который подается на вход корцг.:

..

.335690

ректора 4. На другой вход корректора 4 подается искажеиный сигнал с выхода второго разряда регистра /. В корректоре 4 происходит суммирование по модулю два корректирующего и искаженного сигнала, и на выходе корректора 4 появляется исправленный сигнал, который заносится к первый разряд регистра 1.

Предмет изобретения

Устройство для декодирования двоичных кодов, содержащее регистр сдвига, соединенный с блоком контрольной проверки, сумматор ПО модулю 2, схемы «ИЛИ-НЕ, «РЬ, отличающееся тем, что, с целью повышения надежности, в него дополнительно введены триггер и линия задержки, причем выход блока контрольной проверки соединен со входом

триггера и входом линии задержки, выходы линии задержки соединены со входами схемы «ИЛИ-НЕ, выход который соединен с одним входом схемы «И, другой вход которой соединен с выходом триггера, выход схемы

«PI соединен с одним входом сумматора по модзлю 2, другой вход которого соединен с выходом второго разряда регистра сдвига, а выход - со входом первого разряда регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Корректор ошибок | 1989 |

|

SU1810909A1 |

| СПОСОБ ИСПРАВЛЕНИЯ МНОГОКРАТНЫХРАЗНЕСЕННЫХ И СОСРЕДОТОЧЕННЫХВ ПАКЕТЫ ОШИБОК | 1972 |

|

SU428435A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1149318A1 |

| Устройство для контроля накопителя | 1973 |

|

SU470867A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Устройство для хранения информации с контролем | 1989 |

|

SU1691897A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО ДИСКРЕТНОГО РЕГУЛИРОВАНИЯ КОЭФФИЦИЕНТА ПЕРЕДАЧИ | 1971 |

|

SU292215A1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

Выход I

-t1

LirrTzz:

Даты

1972-01-01—Публикация