(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ НАКОПИТЕЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Запоминающее устройство с автономным контролем | 1977 |

|

SU684620A1 |

| Запоминающее устройство с исправлением ошибок | 1979 |

|

SU920845A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU964737A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Устройство для исправления ошибок | 1974 |

|

SU544151A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1048520A1 |

| Декодирующее устройство | 1989 |

|

SU1681388A1 |

| УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК | 1971 |

|

SU311269A1 |

| Декодирующее устройство | 1989 |

|

SU1644223A1 |

1

Настоящее изобретение относится к области запоминающих устройств.

Известно устройство для контроля наконителя, например постоянного или полуностоянного, содержащее декодирующий блок, вход которого подсоединен к выходу накопителя, счетчик, выход которого соединен со входами индикатора и наконителя, схему останова и блок управления.

Известное устройство исправляет одиночные и обнаруживает двойные ошибки.

Недостатком известного устройства является то, что в случае ошибок более высокой кратности оно производит ложные исправления, вырабатывая сигнал «двукратная ощибка только при наличии двойных и некоторых других ошибок четной кратности.

Описываемое устройство отличается от известного тем, что оно содержит схему «И, переключатель режима работы и схему «Запрет, входы которой подключены к соответствующим выходам декодирующего блока и блока управления, а выход - ко входам схемы останова и счетчика, выход схемы «И соединен с одним из входов декодирующего блока, первый вход - с выходом блока управления, второй вход через переключатель - с одним нз входов блока управления и соответствующими входами счетчика и схемы «Занрет.

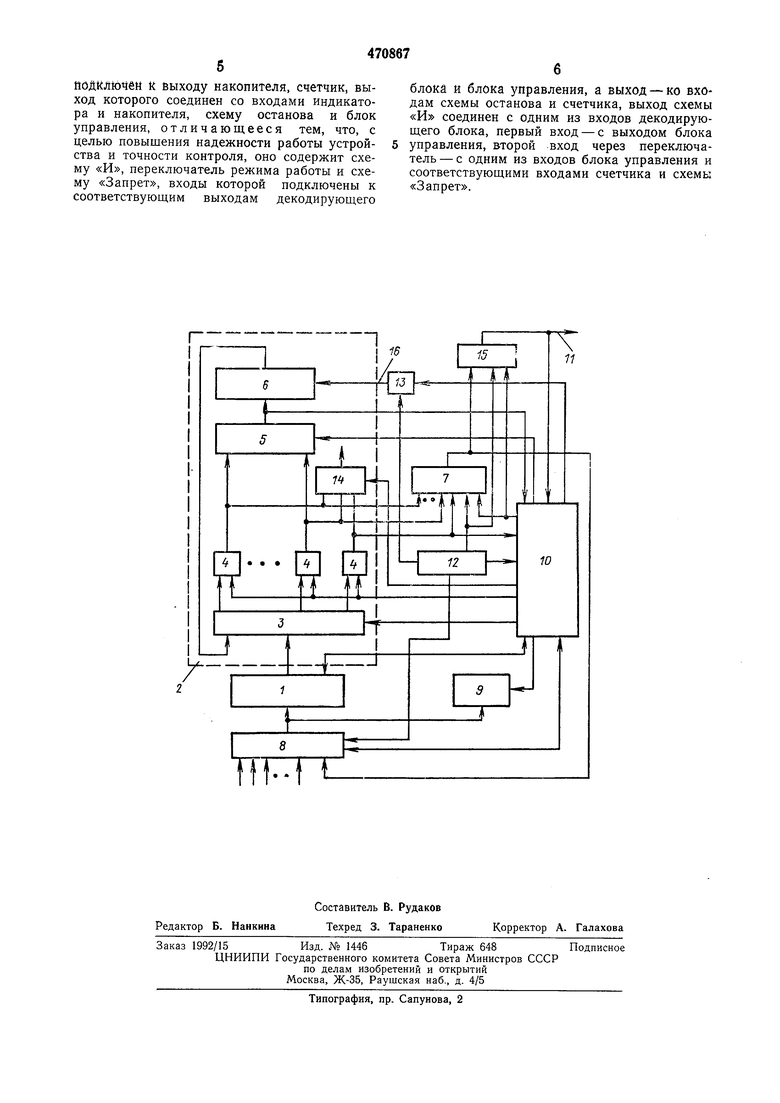

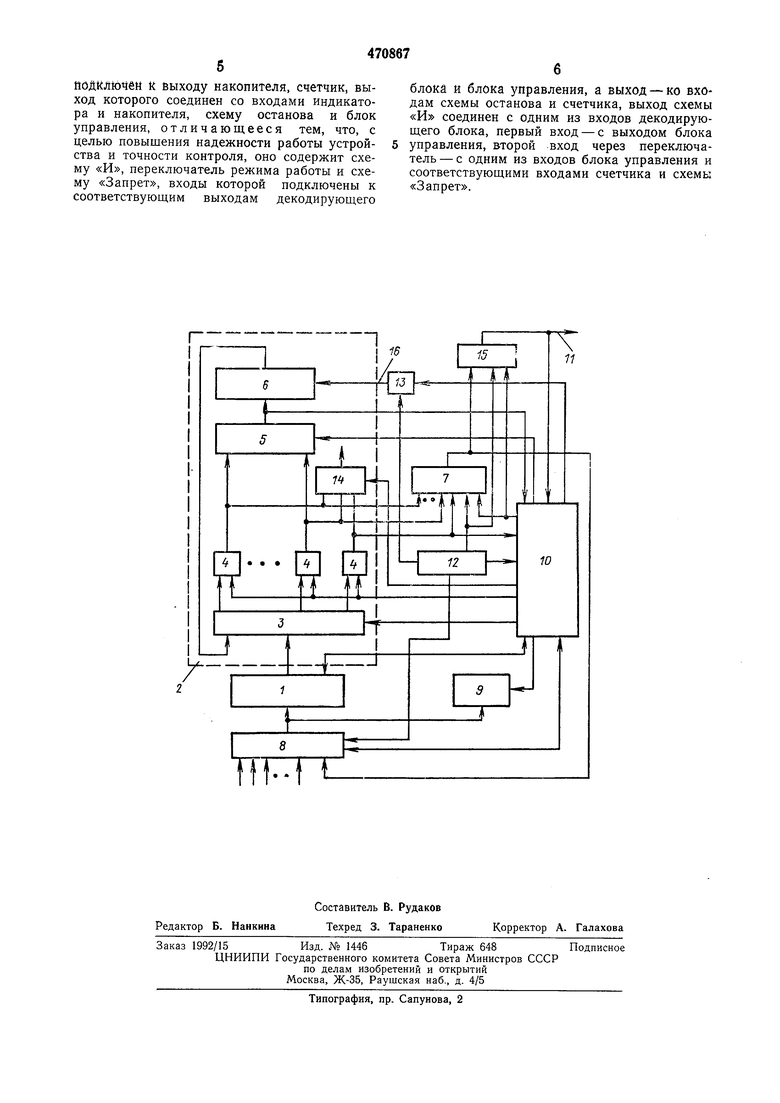

Указанные отличия позволяют повысить надежность работы устройства и точность контроля. На чертеже изображена блок-схема устройства.

Устройство содержит накопитель 1, с выхода которого при подаче на его вход кода адреса и имнульса запроса считывается {т + -rk) -разрядное число (где т - количество

информационных разрядов, ()-количество контрольных разрядов кода Хэмминга с кодовым расстоянием ), декодирующий блок 2 кода Хэмминга в составе и-разрядного (где + /г) приемного регистра 3 параллельного действия, единичные входы которого подсоединены к выходным шинам накопителя , k сумматоров 4 по модулю два, соединенных с выходами регистра 3, /-разрядный регистр коррекции 5, входы которого нодсоединены к выходам сумматоров 4, кроме последнего, дешифратор коррекции 6, входы которого подключены к выходам регистра коррекции 5, а выходные шины - к счетным входам триггеров регистра 3.

Устройство, кроме того, содержит схему «Запрет 7, счетчик 8, индикатор 9, блок управления 10, соединенный с выходной шиной 11, переключатель 12 режима работы, схему «И 13. В состав блока 2 также входит

схема 14 выработки сигнала «двукратная

ошибка, соединенная с последним (правым - па чертеже) сумматором 4. Устройство также содержит схему остапова 15. Входы схемы «Запрет 7 подключены к соответствующим выходам блоков 2 и 10, а выход - ко входам схемы 15 и счетчика 8. Выход 16 схемы «И 13 соединен с одним из входов блока 2, первый вход - с выходом блока управления 10, второй - с одним из выходов переключателя 12, другие выходы которого соединены со входами блока 10, счетчика 8 и схемы 7.

Устройство может работать в режимах «Проверка или «Коррекция. Переключение из одного режима работы в другой происходит переключателем 12 режима работы.

В режим «Проверка устройство контроля переводится перед включением накопителя 1 в рабочий режим с целью обнаружения и устранения обнаруживаемых ошибок любой кратности.

Во время работы наконителя в составе цифровой вычислительной машины (ЦВМ) устройство контроля переводится в режим «Коррекция с целью исправления одиночных и обнаружепия двукратн ых ошибок, возникших после автономной проверки.

Устройство работает следуюшим образом.

Перед запуском устройства счетчик 8, регистры 3 и 5 сигналом «сброс устанавливаются в состояние «О.

В режиме «Проверка счетчик 8 отключается от ЦВМ, на один из входов схемы 7 подается разрешаюш,ий потенциал, схема 13 закрывается, блокируя работу дешифратора коррекции 6.

При пуске производится последовательное обрашение к адресам накопителя 1, коды которых задаются состоянием счетчика 8. Счетчик 8 перебрасывается в следуюшее состояние от счетных импульсов, поступаюш,их с выхода схемы 7. Счетные импульсы на выходе схемы 7 вырабатываются при наличии нулевого кода на выходах сумматоров 4 синхронизирующих импульсов, поступающих с блока управления 10, и разрешающего потенциала с переключателя 12.

Каждое считанное с выхода накопителя 1 число переписывается в регистр 3, с которого поступает на входы сумматоров 4. Каждый из сумматоров 4, кроме последнего, проверяет на четность определенный набор разрядов считанного числа. Последний сумматор 4 проверяет на четность весь «-разрядный набор считанного числа.

Если после декодирования числа на выходах сумматоров 4 установился нулевой код, это свидетельствует об отсутствии ошибок ввода и считывания проверяемого числа. С поступлением синхронизирующего импульса схема 7 формирует счетный импульс, перебрасывающий счетчик 8 в следующее состояние. Считывается и проверяется новое число и т. д.

Если после декодирования числа па выходе хотя бы одного из сумматоров 4 установился

ненулевой код, на выходе схемы 7 счетный сигнал не формируется и счетчик 8 остается в том же состоянии. Схема останова 15 вырабатывает сигнал «Останов, условием выработки которого является отсутствие счетного сигнала с выхода схемы 7, наличие синхронизирующего сигнала с блока унравления 10 и положение переключателя 12 в состоянии «Проверка. Определение адреса числа, при

считывании которого была обнаружена ошибка, производится определением состояния счетчика 8, осуществляемого визуально с помощью индикатора 9.

Причина ошибки устраняется. Счетчик 8,

регистры 3 и 5 устанавливаются в «О и устройство запускается снова.

Проверка накопителя 1 продолжается до тех пор, пока устройство не проработает без останова в течение времени, которое больше

требуемого, для последовательного опроса и проверки всех чисел, хранимых в накопителе. В режиме «Коррекция на один из входов схемы 7 и на вход схемы 15 посредством переключателя 12 подается нулевой сигнал, блокируя их работу. Схема 13 открыта для пропускания синхронизирующих импульсов, поступаюших с блока управления 10 и стробирующих работу дешифратора коррекции 6. На входы счетчика 8 из ЦВМ поступает код

адреса числа. С приходом сигнала запроса с выхода накопителя 1 считывается и декодируется я-разрядное число.

В результате декодирования на выходах сумматоров 4, кроме последнего, устанавливается код, представляющий собой двоичное изображение номера искаженного разряда, который запоминается регистром коррекции 5. Результат проверки па четпость всех разрядов с выхода последнего сумматора 4 поступает в блок управления 10.

Если носле декодирования числа на регистре коррекции 5 и на выходе последнего сумматора 4 установились нулевые коды, это указывает на отсутствие ошибки и считанное

число выдается в ЦВМ без корректировки.

Если после декодирования числа на регистре коррекции 5 окажется код, отличный от нуля, а на выходе последнего сумматора 4 - единица, то на соответствующей шине дешифратора 6 появится сигнал коррекции, воздействующей на счетный вход триггера искаженного разряда регистра 3, в результате чего ошибка исправляется.

В остальных двух случаях (на регистре 5 -

ненулевой код, на выходе последнего сумматора 4 - нуль, и наоборот) обнаруживаются не корректируемые ошибки, при которых схема 14 выработки сигнала «Двукратная ошиб ка вырабатывает сигнал «Ошибка. Эти

ошибки устраняются переводом устройства контроля в режим «Проверка.

Предмет изобретения

Устройство для контроля накопителя, содержащее декодирующий блок, вход которого

ПбДКлючем к выходу накопителя, счетчик, выход которого соедииен со входами индикатора и накопителя, схему останова и блок управления, отличающееся тем, что, с целью повышения надежности работы устройства и точности контроля, оно содержит схему «И, переключатель режима работы и схему «Запрет, входы которой подключены к соответствующим выходам декодирующего

1 I-

/

блока и блока управления, а выход - ко входам схемы останова и счетчика, выход схемы «И соединен с одним из входов декодирующего блока, первый вход - с выходом блока управления, второй вход через переключатель - с одним из входов блока управления и соответствующими входами счетчика и схемы «Запрет.

Авторы

Даты

1975-05-15—Публикация

1973-05-17—Подача