Изобретение относится к области цифровой вычислительной техники и может быть использовано -в запоминающих устройствах цифровых вычислительных машин.

Известны постоянные запоминающие устройства (ЗУ) с непосредственной выборкой, например постоянное запоминающее устройство трансформаторного типа, в котором для записи кодов используются многообмоточные трансформаторы.

Однако такое устройство требует большого объема, оборудования и большого объема монтажных работ при записи информации (кодовый провод в наихудшем случае прошивает столько сердечников, сколько разрядов содержит код).

Кроме того, в нем применяются разнообразные элементы для выполнения логических и запоминающих функций, и невозможно интегральное исполнение всего ЗУ.

Целью изобретения является повышение надежности ЗУ, сокращение объема оборудования, унификация применяемых элементов и Обеопечение интегрального иополнения ЗУ с непосредственной выборкой.

Эта цель достигается тем, что в качестве накопителя применен счетчйк в режиме последовательного счета, а для выделения определенных кодов - временный дискриминатор, состоящий из п кольцевых переочетных схем.

Коэффициеиты пересчета PI, PZ, ., РП этих схем и чИ|Сло разрядов т счетчика связаны соотношением Р, -, РП. Кроме того, в устройстве применена общая схема «ИЛИ и программное устройство. Программное устройство выполнено на логических вентилях, входы которых подключены к тем элементам кольцевых пересчетных схем, порядковый номер которых равен остатку от деления порядкового номера временного импульса, выделяющего определенный код, на число элементов кольцевой пересчетной схемы, и к определенным выходным ячейкам дешифратора адреса, представляющим собой много-кодовые

схемы «ИЛИ. Счетчик, кольцевые пересчетные схемы и адресный регистр охвачены логической обратной связью с выхода общей схемы «ИЛИ через элемент задержки для установки всей схемы в исходное положение

после выборки необходимого кода.

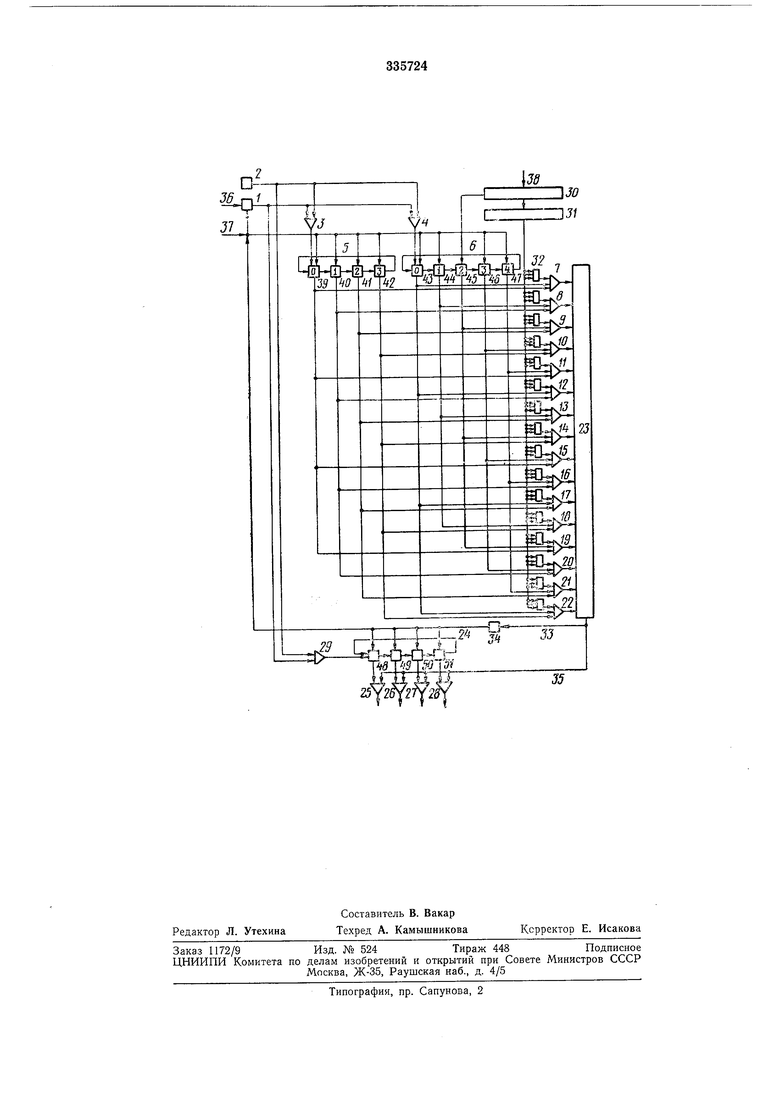

На чертеже изображена блок-схема предложенного ЗУ.

ЗУ состоит из схемы пуска и останова /, задающего генератора 2, входных вентилей 3

и 4, кольцевых пересчетных схем 5 и б, логических вентилей 7-22 общей схемы «ИЛИ 23, счетчика 24, выходных вентилей 25-28, входного вентиля 29, регистра адреса 30, дешифратора адреса 5/, выходными ячейками 32 «ИЛИ, логической обратной связи 33 через элемент задержки 34, стробирующей связи 55, входной связи пуска и останова 36, входной связи устанОВКи в исходное состояние 37 и входной связи ycTaHOBiKH адреса 38. Кольцевая пересчетная схема 5 состоит из элемента «О 39, элемента «1 40, элемента «2 41, элемента «3 42. Кольцевая пересчетная схема 6 состоит из элемента «О 43, элемента «1 44, элемента «2 45, элемента «3 10 46 и элемента «4 47. Счетчик 24 состоит из элементов 48-51. Логические вентили 7-22 образуют устройство, предназначенное для выделения временных импульсов от О до 15. Связи на входы вентилей 7-22 заведены с15 тех элементов кольцевых пересчетных схем, порядковый номер которых равен остатку от деления порядкового номера временного импульса, выделяющего необходимый код, на число элементов кольцевой пересчетной схе-20 мы, и с выходных ячеек 52 дешифратора адреса 31. ЗУ работает следующим образом. Перед обращением к устройству кольцевые пересчетные схемы 5 и б, счетчяк 24 и регистр25 адреса 30 устанавливаются в исходное состояние с приходом импульса на входную связь установки в исходное состояние 57. С входной связи установки адреса 55 код адреса записывается в регистр адреса 30. В дещифраторе30 адреса 31 возбуждается одна из выходных ячеек 52. Разрешающий сигнал с этой ячейки поступает на один из трех входов одного из вентилей 7-22. Задающий генератор вырабатывает импуль-35 сы, поступающие на входные вентили 3, 4 к 29, с которых сигналы поступают соответст«венно в кольцевые дересчетные схемы 5 и 5, а также на счетчик 24 только при поступлении сигнала на входную связь 36, запускающую40 схему 1. Сигнал, пришедший со схемы /, разрешает прохождение импульсов задающего генератора 2 через входные вентили 3, 4 и 29. В элементы «О 39 и 43 схем 5 и 5 и элемент 50 счетчика 24 записывается «1. С при.ходом45 каждого импульса с задающего генератора 2 «Ь переносится в следующие элементы схем 5 и б, а содержимое счетчика 24 изменяется на «1. Как только на всех входах одного из вентилей 7-22 появятся сигналы, выходной50 5 сигнал с этого вентиля поступает на общую схему «ИЛИ 23. С выхода схемы 23 сигнал поступает сразу в логическую обратную связь 55 и стробирующую связь 55. Сигнал стробирующей связи 55 разрешает считывание информации, записанной к этому моменту времени в счетчике 24, и на выходных вентилях 25-28 появляется необходимый код. Сигнал с выхода схемы «ИЛИ 23, .поступающий в логическую обратную связь 55, задерлсивается элементом задержки 34 и затем после появления кода на выходах вентилей 25-28 устанавливает схемы /, 5 и 5, счетчик 24 и регистр адреса 30 в исходное состояние. ЗУ готово к следующему обращению, Предмет изобретения Постоянное запоминающее устройство с непосредственной выборкой, состоящее из регистра адреса, дещифратора адреса с многовходовыми схемами «ИЛИ на его выходах, тразрядного счетчика со схемами «И на его выходах, п кольцевых пересчетных схем, коэффициенты пересчета Р, РЧ ... Р„ которых и число разрядов т счетчика связаны соотношением , PZ, ... РП логических вентилей, выходы которых подключены к общей схеме «ИЛИ, задающего генератора, схемы пуска и останова, выходы которых подключены ко входам входных вентилей, схемы установки в исходное положение и линии задержки, отличающееся тем, что, с целью повышения надежности и сокращения размеров постоянного запоминающего устройства, входы логических вентилей соединены с выходами многовходновых схем «ИЛИ адресного дешифратора и с выходами элементов кольцевых пересчетных схем, порядковый номер которых равен остатку от деления порядкового номера временного импульса, выделяющего определенный код, на число элементов кольцевой пересчетной схемы, а выходы логических вентилей соединены со входами общей схемы «ИЛИ, выход которой подключен ко входам схем «И т-разрядного счетчика и ко входу линии задержки, которая, соединяя выход общей схемы «ИЛИ со входом схемы установки в исходное положение, образует обратную логическую связь.

35

| название | год | авторы | номер документа |

|---|---|---|---|

| ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1972 |

|

SU337823A1 |

| Программируемый контроллер | 1984 |

|

SU1453404A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

| Запоминающее устройство с резервированием | 1980 |

|

SU963088A1 |

| Устройство для обмена данными между источником и приемником информации | 1988 |

|

SU1557566A1 |

| Многокоординатная система числового программного управления | 1972 |

|

SU448435A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| Способ фазового управления вентильным преобразователем | 1985 |

|

SU1257784A1 |

| Устройство для программного управления | 1981 |

|

SU1003020A1 |

| Программируемый контроллер | 1985 |

|

SU1509887A2 |

Даты

1972-01-01—Публикация