Изобретение отиосится к области вычислительной техники и может быть использовано в устройствах отсчета времени и в других операционных счетных устройствах.

Известны счетчики со схемой считывания текущего значения кода, содержащие входные шины счетных импульсов и импульса считывания, пеночку из последовательно соединенных через первые импульсные выходы триггеров со счетным входом, потенпиальные выходы которых через вентили считывания подключены к выходным кодовым шипам.

Недостатком известных устройств Я1вляется низкое быстродействие устройства, так как время считывания достигает времени периода следования входных и-мпульсов.

Цель изо бретения - сокращение времени считывания.

Это достигается тем, что в устройство введены входные триггеры счетных нмпульсо.в н считывания, первые входы которых связаны с шинами счетных импульсов и считывания, а выходы - с входами дополнительного триггера и нервыми входамИ двух схем «НЕ-И, вторые входы которых связалы с выходами соответствующих олеч дополнительного триггера, а выходы схем «НЕ-И соединены соответственно с счетным входом триггера младшего разряда счетчика и с управляющими входамн вентилей считывания, связанными также с лииией задержки; вторые им;пульспые выходы триггеров разрядов счетчика через схему «ИЛИ -подключены ко второму входу входного триггера счетных импульсов, а выход линии задержки связан со вторым входом входного триггера считыван-ия.

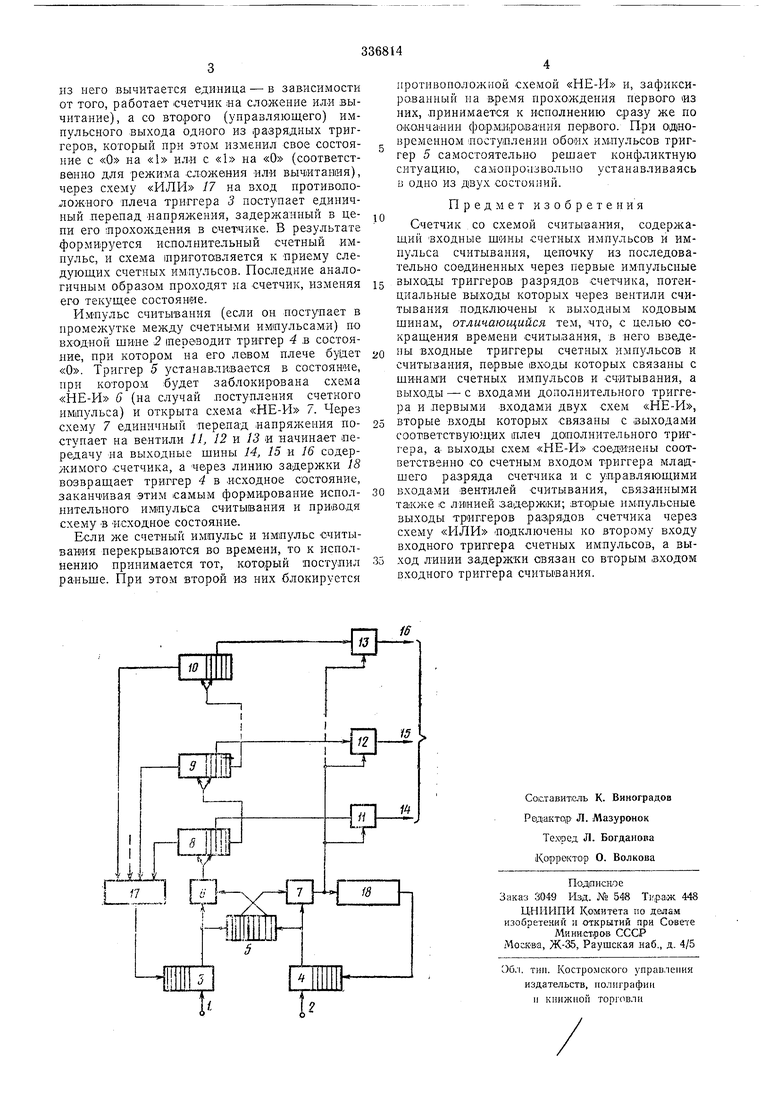

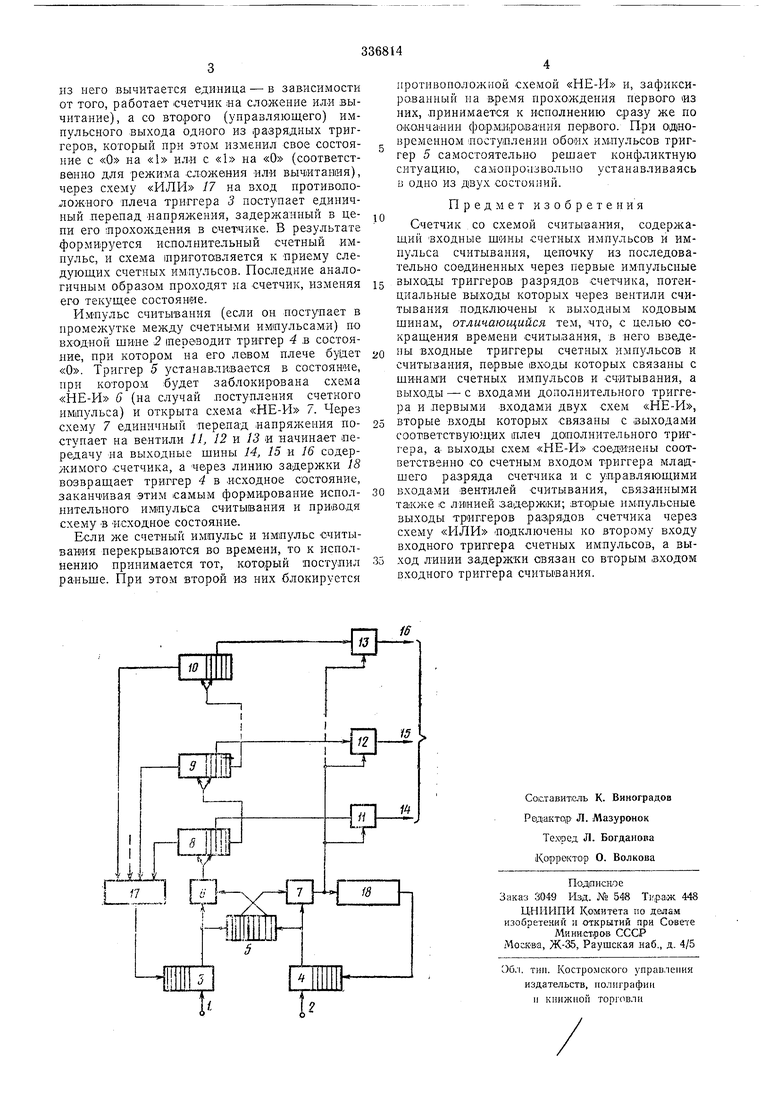

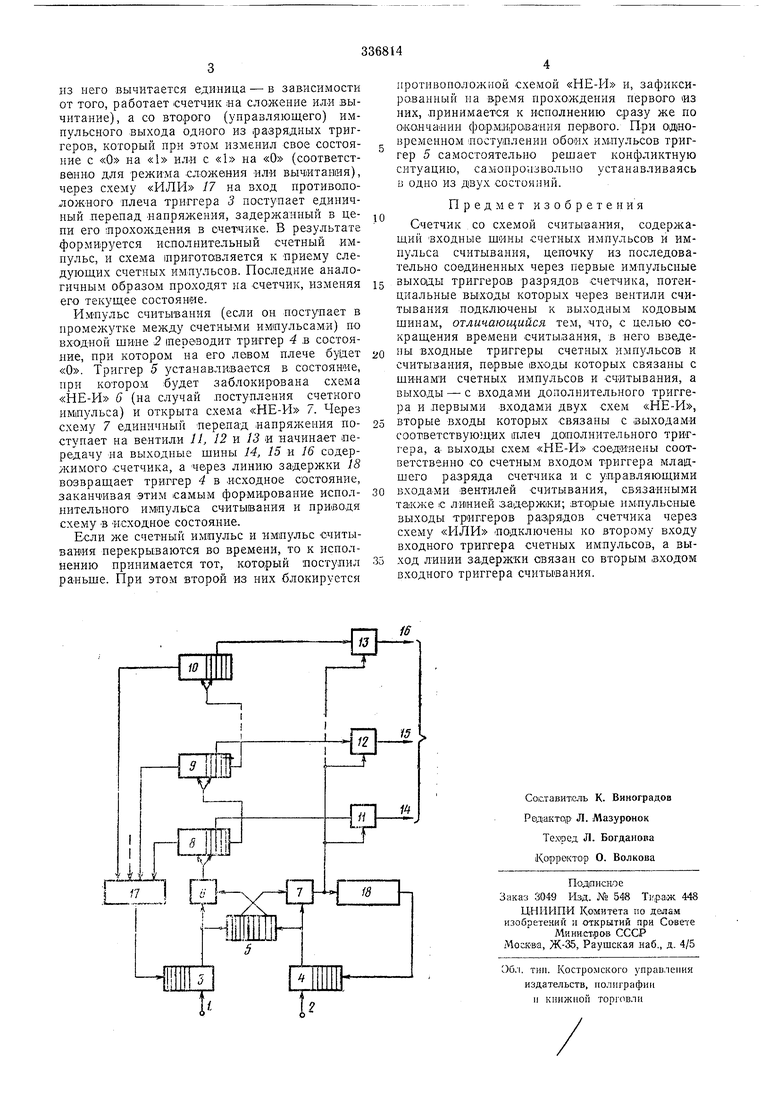

На чертеже приведена схема устройства.

Устройство содерл ит .входную шину счетных импульсов / и входную шину импульса считывания 2, соответствуюпгне им входные триггеры 3 и 4, триггер синхронизапии 5 со схемами «НЕ-И 6 и 7 па его выходах, счетчик со счетным входом, содержащий разрядные триггеры S, 9 и 10, вантилл считывания //, 12 и 13 с выходными ШПнами 14, 15 и 16, соответственно, собирательную схему «ИЛИ 17 п линию задержки 18 (например, пеночку инверторов). Заштрихованным плечам триггеров соответствуют сигналы «О.

Нри работе схемы каждый счетный импульс iia шине 1 переводит триггер 5 в состояние «О п, если триггер 4 находится в состоянии, ноказанном на чертеже, переводит триггер 5 в состоян-ие, нри котором на его «правом плече сохраняется состояние «О, а на левом - возникает «1. Нри этом выключается схема «НЕ-И 7. включается схема «HE-PI 6 и единичный |Перепад напряжепия поступает на вход счетчика. Носледпий .изменяет свое состояние (к его со-держимому добавляется или

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ РЕВЕРСИВНЫЙ СЧЕТЧИК | 1971 |

|

SU311405A1 |

| ИЗОБРНТ37М. Кл. Н 0.3k 23/04УДК 621.374.4(088.8) | 1973 |

|

SU407426A1 |

| Устройство синфазирования тактовых импульсов | 1971 |

|

SU497875A1 |

| Генератор импульсов с управляемойчАСТОТОй | 1979 |

|

SU834940A2 |

| ПЛКЙТНО-ИХШЕСЙА*ЬИБ;1ИО'^ЕКАГ. Л. Биланов | 1972 |

|

SU342297A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА В ЧАСТОТУ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2037960C1 |

| Измеритель длительности импульсов | 1990 |

|

SU1714535A1 |

| Генератор импульсов | 1986 |

|

SU1406735A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Дискретная линия задержки | 1980 |

|

SU961123A1 |

Даты

1972-01-01—Публикация