Изобретение относится к области вычислительной техники и может быть применено в аналого-цифровых вычислительных системах.

Известны делительные устройства, использующие устройства умножения с комбинированным представлением информации, включенные в цепь обратной связи решающего усилителя.

Такое конструктивное исполнение известных устройств не позволяет применять их в матричных моделях, так как проводимость, включения и обратную связь решающего усилителя, влияет на значение всех коэффициентов данной строки системы уравнений.

Цель изобретения - расширение функциональных возможностей устройства.

Это достигается тем, что в него дополнительно введены два п-разрядных следящих преобразователя аналог-код, устройство памяти и цифровой блок церемножения. При этом цифровой выход нервого п-разрядного следящего преобразователя аналог-код соединен с устройством памяти, цифровой выход второго - с цифровым блоком неремножения, а аналоговый выход второго преобразователя- с аналоговым входом п-разрядного резистора. Цифровой блок перемножения связан с управляющим входом п-разрядного кодоуправляемого резистора, устройство памяти соединено с управляющим входом fe-pазрядного кодоуправляемого резистора и с цифровым блоком перемножения. Делимое Xi и делитель х поступают на входы п-раз5 рядных следяющих преобразователей аналог-код.

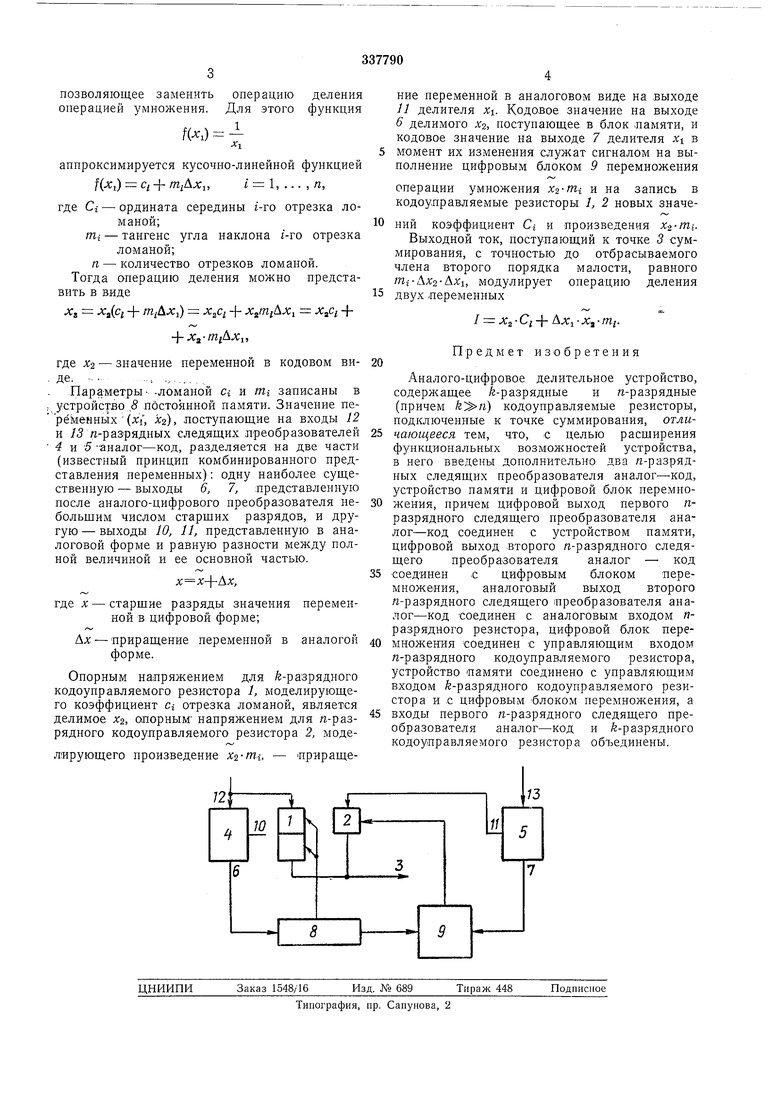

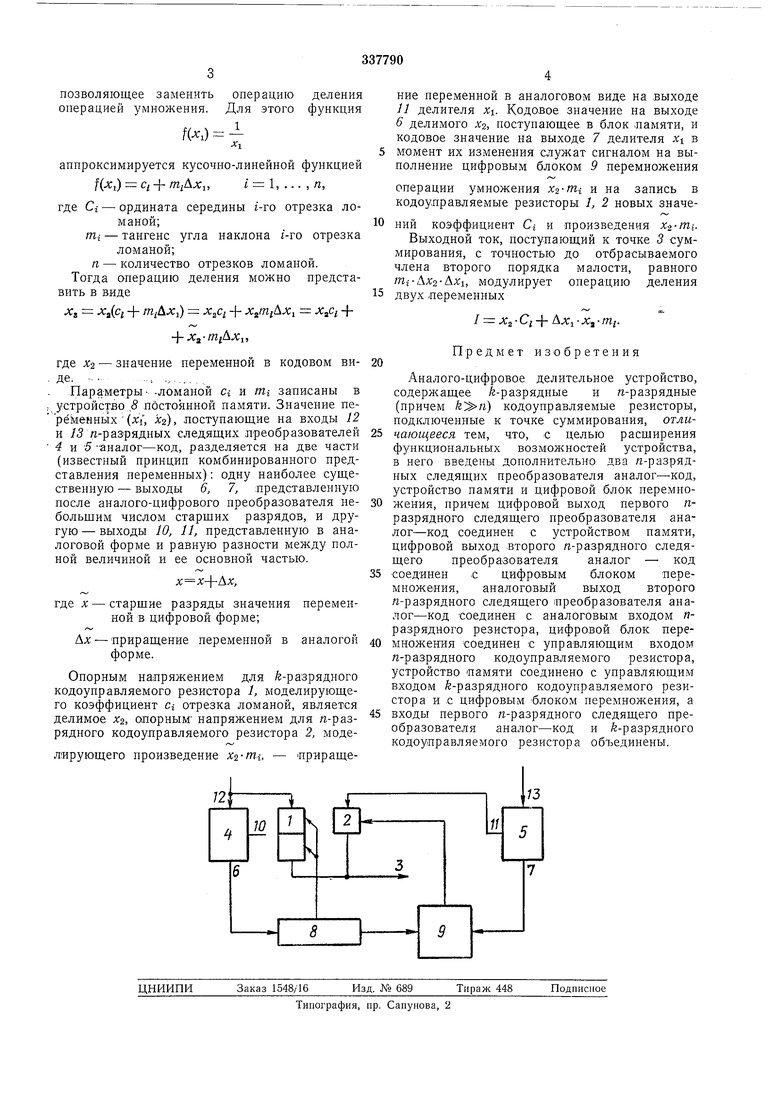

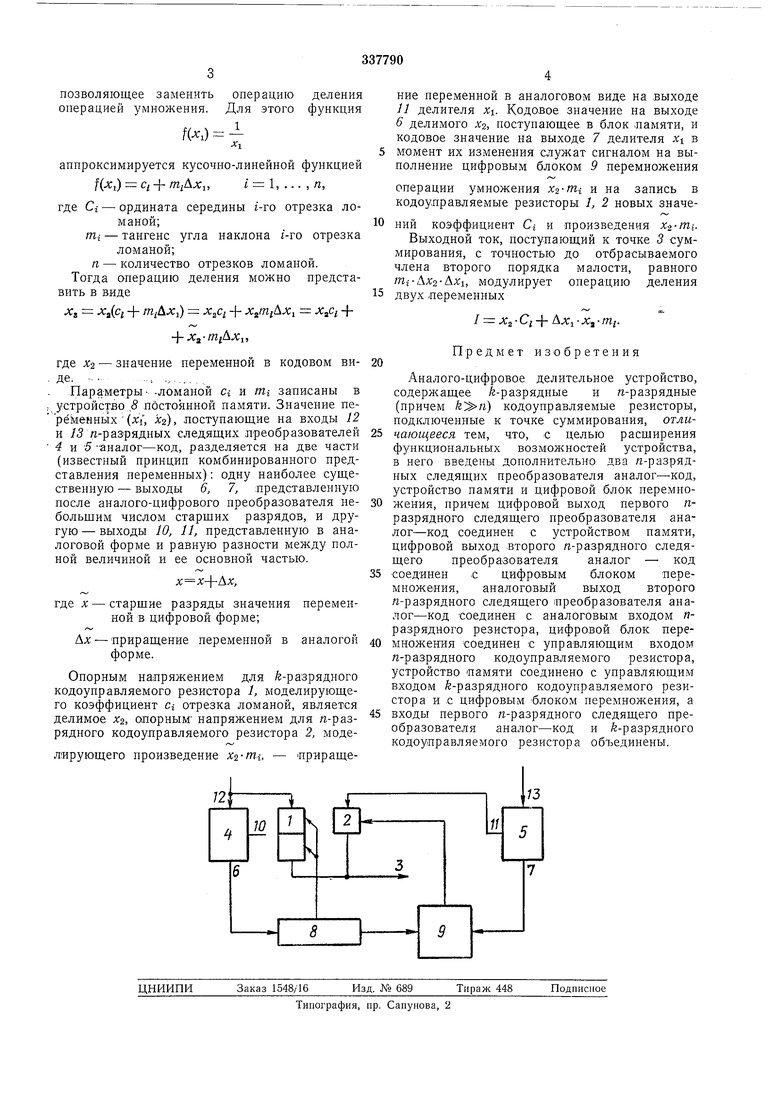

Па чертеже показано предлагаемое устройство.

0 Оно состоит из й-разрядного кодоуправляемого резистора , п-разрядного кодоуправляемого резистора 2 (причем ), подключенных к точке 3 суммирования, и двух д-разрядных следяющих преобразователей 4 и 5

5 аналог-код. Выходы 6 -ц 7 преобразователей-цифровые (кодовые) - соединены соответственно с устройством 8 памяти, выдающим значения кодов в А-разрядный кодоуправляемый резистор 7, и с цифровым блоком 9 перемножения, выдающим значения кодов в п-разрядный кодоуправляемый резистор 2. Выходы 10 Е 11 - аналоговые, причем напряжение в виде приращения переменной с выхода 11 является опорным напряжением

5 «-разрядного кодоуправляемого резистора 2. Устройство работает следующим образом.

позволяющее заменить операцию деления операцией умножения. Для этого функция

-

1 аппроксимируется кусочно-линейной функцией

/(jCi) 01 + ,/ 1, . . . , л,

где Сг - ордината середины i-ro отрезка ломаной;mi - тангенс угла наклона г-го отрезка

ломаной;

п - количество отрезков ломаной. Тогда операцию деления можно представить в виде

ATj . Xa(Ci -f ) - X,,Ci + , JCjQ -f - Xy-IHil Xi,

где X2 - значение переменной в кодовом виде. - ....

Пара-метры -ломаной d и /Пг записаны в устройство 8 пбстоянной памяти. Значение перёменнь1х (хь хг), поступающие на входы 12 и /5 «-разрядных следящих преобразователей 4 и 5 -аналог-код, разделяется на две части (известный принцип комбинированного представления переменных): одну наиболее существенную - выходы 6, 7, представленную после аналого-цифрового преобразователя небольшим числом старших разрядов, и другую - выходы JO, 11, представленную в аналоговой форме и равную разности между полной величиной и ее основной частью.

,

где X - старшие разряды значения переменной в цифровой форме;

А.Х--приращение переменной в аналогой форме.

Опорным напряжением для -разрядного кодоуправляемого резистора 1, моделирующего коэффициент Сг отрезка ломаной, является делимое Xz, опорным- напряжением для «-разрядного кодоуправляемого резистора 2, моделирующего произведение , - приращение неременной в аналоговом виде на выходе 1 делителя х. Кодо.вое значение на выходе 6 делимого Х2, поступающее в блок ламяти, и кодовое значение на выходе 7 делителя Xi в момент их изменения служат сигналом на выполнение цифровым блоком 9 перемножения

операции умножения и на запись в кодоуправляемые резисторы 1, 2 новых значений коэффициент Сг и произведения x-y-mt. Выходной ток, поступающий к точке 3 суммирования, с точностью до отбрасываемого члена второго порядка малости, равного tni-Ax2-Axi, модулирует операцию деления двух переменных

I Axi-x,-m{.

Предмет изобретения

Аналого-цифровое делительное устройство, содержащее -разрядные и п-разрядные (причем ) кодоуправляемые резисторы, подключенные к точке суммирования, отличающееся тем, что, с целью расширения функциональных возмолсностей устройства, в него введены дополнительно два /г-разрядных следящих преобразователя аналог--код, устройство памяти и цифровой блок перемножения, причем цифровой выход первого празрядного следящего преобразователя аналог-код соединен с устройством памяти, цифровой выход второго «-разрядного следящего преобразователя аналог - код

соединен -с цифровым блоком перемножения, аналоговый выход второго «-разрядного следящего преобразователя аналог-код соединен с аналоговым входом яразрядного резистора, цифровой блок перемножения соединен с управляющим входом «-разрядного кодоуправляемого резистора, устройство памяти соединено с управляющим входом -разрядного кодоуправляемого резистора и с цифровым блоком перемножения, а

входы первого п-разрядного следящего преобразователя аналог-код и й-разрядного кодоуправляемого резистора объединены.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое делительноеуСТРОйСТВО | 1979 |

|

SU809225A1 |

| Устройство для решения линейных систем алгебраических уравнений | 1985 |

|

SU1325464A1 |

| Аналого-цифровое множительное устройство | 1974 |

|

SU499569A1 |

| АНАЛОГО-ЦИФРОВОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО | 1997 |

|

RU2123720C1 |

| Устройство для контроля и оценки среднего значения аналогового сигнала | 1988 |

|

SU1674159A1 |

| Гибридное множительное устройство | 1985 |

|

SU1325521A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СОПРОТИВЛЕНИЙ И ПРИРАЩЕНИЯ СОПРОТИВЛЕНИЯ | 2003 |

|

RU2249223C1 |

| Цифровой следящий привод | 1980 |

|

SU930247A1 |

| Цифро-аналоговый многофункциональный преобразователь | 1982 |

|

SU1062732A2 |

| Устройство коррекции | 1987 |

|

SU1499507A1 |

Даты

1972-01-01—Публикация