1

Изобретение относится к вычислительной технике и может быть использовано в управляющих системах и гибридных вычислительных устройствах для преобразования в следящем режиме аналоговых величин в коды с одновременным вычислением их нропзвсдсшп в цифровом виде.

Известны аналого-цифровые множительные устройства, содержащие реверсивные счетчики множимого и множителя, выходы которых соединены с узлами токовой компенсации, подключенными свонми выходами к блокам формирования сигналов управления, выходы положительного и отрицательного приращения которых соединены соответстзеипо со входами сложеиия и вычитания реверсивных счетчиков, сумматор и элементы «И прямого кода множимого, соединенные с единичными выходами реверсивного счетчика множимого. Известные аналого-цифровые множительные устройства для перемножения двух аналоговых величии требуют п тактов для преобразования аиалоговых величин в коды и п тактов для их перемножения, что снижает общее быстродействие устройства. Кроме того, сумматор и реверсивный счетчик множителя должны иметь цепи сдвига содержимого вправо, что усложияет их структуру. Предлагаемое устройство отличается тем, что, с целью повыщения его быстродействия, оио дополнительно

содержит элементы «И обратного кода множимого, элемеиты «И прямого и обратного кодов множителя, основные и дополнительный блоки разделения, блок управлепня и линию

задержки, причем, единичные и нулевые выходы реверсивного счетчика множителя и пулевые выходы реверсивного счетчика множимого соединены со входами элементов «И прямого и обратного кода множителя и элемептами «И обратного кода множимого соответственно, а выходы элементов «И прямого и обратного кода мнол ;нтеля и множимого нодключены через основные блокн разделения ко входам сумматора каждого разряда, выход

положительного и отрицательиого приращения блока формирования сигнала управления множимого и множителя соединены с управляющими входами элемента «И нрямого и об1) кода множителя и множимого соответствеино, а также через дополнительный блок раздс:1е: ия и линию задержки со входами основных блоков разделения, нодключенных ко входу младтпего разряда сумматора, единичный и пулевой выходы блока управления соединены со входами блока формирования сигналов управлепня множимого и множителя соответственно.

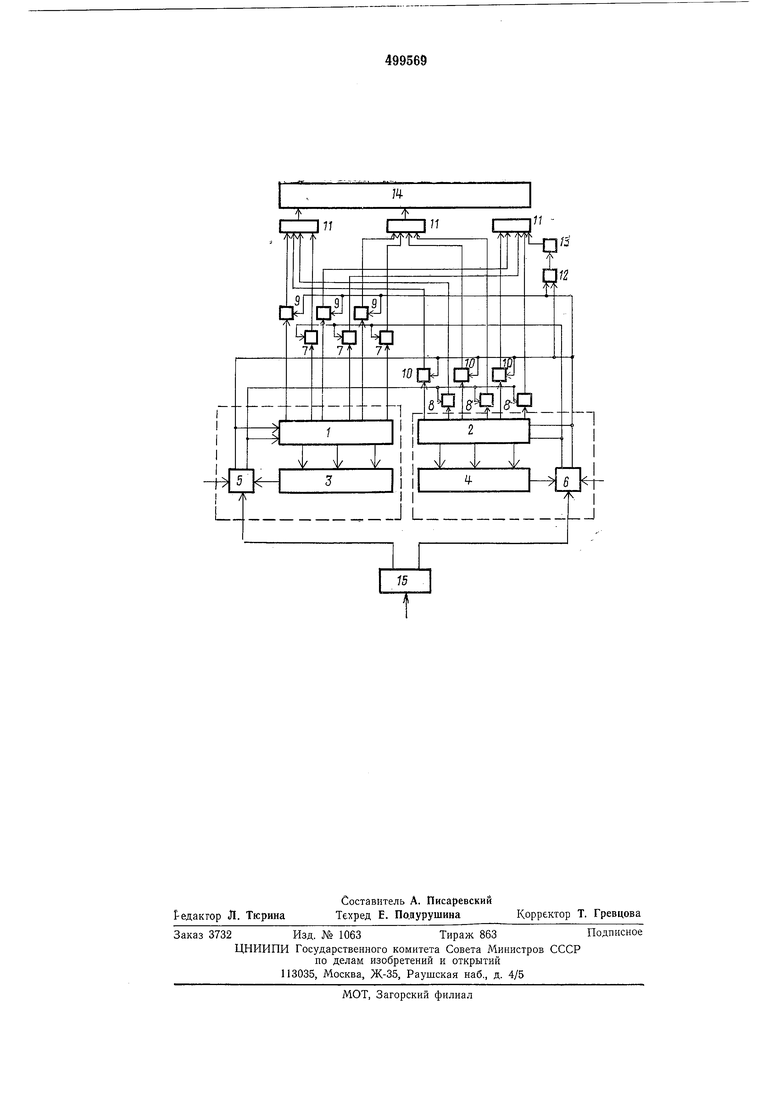

Схема предлагаемого устройства представлена на чертеже. Оно состоит из реверсивного счетчика множимого 1, реверсивного счетчика множителя 2, узла токовой компенсации множимого 3, узла токовой компенсации множителя 4, блоков формирования сигналов управления множимого 5 и множителя 6, элементов «И прямого кода множимого 7 и множителя 8, элементов «И обратного кода множимого 9 и множителя 10, основных блоков разделения 11, дополнительного блока разделения 12, линии задержки 13, сумматора 14 и блока управления 15.

На входы блоков формирования сигналов управления множимого 5 и множителя 6 поступают аналоговые величины множимого (л;) и множителя (у) соответственно. Цифровые коды множимого и множителя накапливаются в реверсивных счетчиках 1 и 2. Импульсы тактовой частоты (/т ) поступают на счетный вход блока управления 15, с выходов которого сигналы поступают на управляющие входы блоков формирования сигналов управления множимого 5 и множителя б так, что в четных тактах работает аналого-цифровой преобразователь множимого, а в нечетных тактах работает аналого-цифровой преобразователь множителя.

Работа устройства происходит в соответствии с формулами

+ sign(x-Xt)2-,(1)

+ s-ign(y-yi)(2)

Zi+i Xi+tyi+i Xiyi + sign(x-Xi)yi2 + slgn{y-y,)xi+i2-,(3)

где X и у - аналоговые значения множимого и множителя;

А;И У; - коды текущих значений множимого и множителя - содержимое реверсивных счетчиков множимого 1 и множителя 2 соответственно;

2; - код текущего значения искомого произведения - содержимое сумматора 14.

Для четного и нечетного тактов работы предлагаемого устройства формула (3) соответственно принимает вид

zi xi+ yi Xiyi+sign(x-Xi)y;2- , (4) zl Xi+iyi+i zi+i zl+sign(y-yi)Xi+i процессе преобразования аналоговых значений множимого и множителя в коды в следящем режиме в соответствии с формулами (4) и (5) производится вычисление текущего значения произведения множимого на

множитель. При этом в зависйМбстй бт знака приращения множимого и множителя на сумматоре 14 производится сложение или вычитание сдвинутых на п разрядов вправо значеНИИ множимого и множителя с предыдущим значением произведения (х-у). Время вычисления произведения в следящем режиме равно двум тактам (/ 2). Результат вычис/ т

ления Zi получается в цифровом коде на сумматоре 14.

Формула изобретения

Аналого-цифровое множительное устройство, содержащее реверсивные счетчики множимого и множителя, выходы которых соединены с узлами токовой компенсации, подключенными своими выходами к блокам формирования

сигналов управления, выходы положительного и отрицательного приращения которых соединены соответственно со входами сложения и вычитания реверсивных счетчиков, сумматор и элементы «И прямого кода множимого, соединенные с единичными выходами реверсивного счетчика множимого, отличающееся тем, что, с целью повышения быстродействия устройства, в него дополнительно введены элементы «И обратного кода множимого, элементы «И прямого и обратного кодов множителя, основные и дополнительные блоки разделения, блок управления и линия задержки, причем единичные и нулевые выходы реверсивного счетчика множителя и нулевые выходы реверсивного счетчика множимого соединены со входами элементов «И прямого и обратного кода множителя и элементами «И обратного кода множимого соответственно, а выходы элементов «И прямого и обратного

кода множителя и множимого подключены через основные блоки разделения ко входам сумматора каждого разряда, выход положительного и отрицательного приращения блока формирования сигнала управления множимого и множителя соединены с управляющими входами элемента «И прямого и обратного кода множителя и множимого соответственно, а также через дополнительный блок разделения и линию задержки со входами основных

блоков разделения, подключенных выходом ко входу младщего разряда сумматора, единичный и нулевой выходы блока управления соединены со входом блока формирования сигналов управления множимого и множителя соответственно.

s

п

i7 n

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровое делительное устройство | 1974 |

|

SU546906A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Многоканальный цифровой коррелятор | 1984 |

|

SU1290352A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1994 |

|

RU2097828C1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Устройство для умножения двоичных чисел | 1990 |

|

SU1711152A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для умножения | 1989 |

|

SU1732341A1 |

| Устройство для умножения | 1986 |

|

SU1427361A1 |

Авторы

Даты

1976-01-15—Публикация

1974-02-01—Подача