Изобретение предназначено для систем передачи и приема цифровой информации и используется для циклического декодирования групповых (и, и)-кодов, корректирующих все одиночные ошибки.

РСНОВНЫМ недостатком существующих устройств декодирования групповых (п, k)1ШДРЗ является малое быстродействие, которое обусловлено большим количеством тактов, требующихся для декодирования прин.яТЬ1Х кодовьхх комбинаций.

Цель изобретения - упрощение схемы устройства и увеличение его быстродействия.

В предлагаемом устройстве эта цель достигает использованием проверочного регистра в залиси проверочных цифр (первый цикл) и в режиме обратного счета (второй цикл) для достижения исходного состояния с целью обнаружения места одиночной ошибки и ее исправления.

Для выявления исходного состояния (00...011) используется логическая схема «И, входы которой подключаются к проверочному регистру-счетчику, а выход - ко вторым входам двухвходовых логических схем, через которые подаются сигналы на исправление одиночных ошибок.

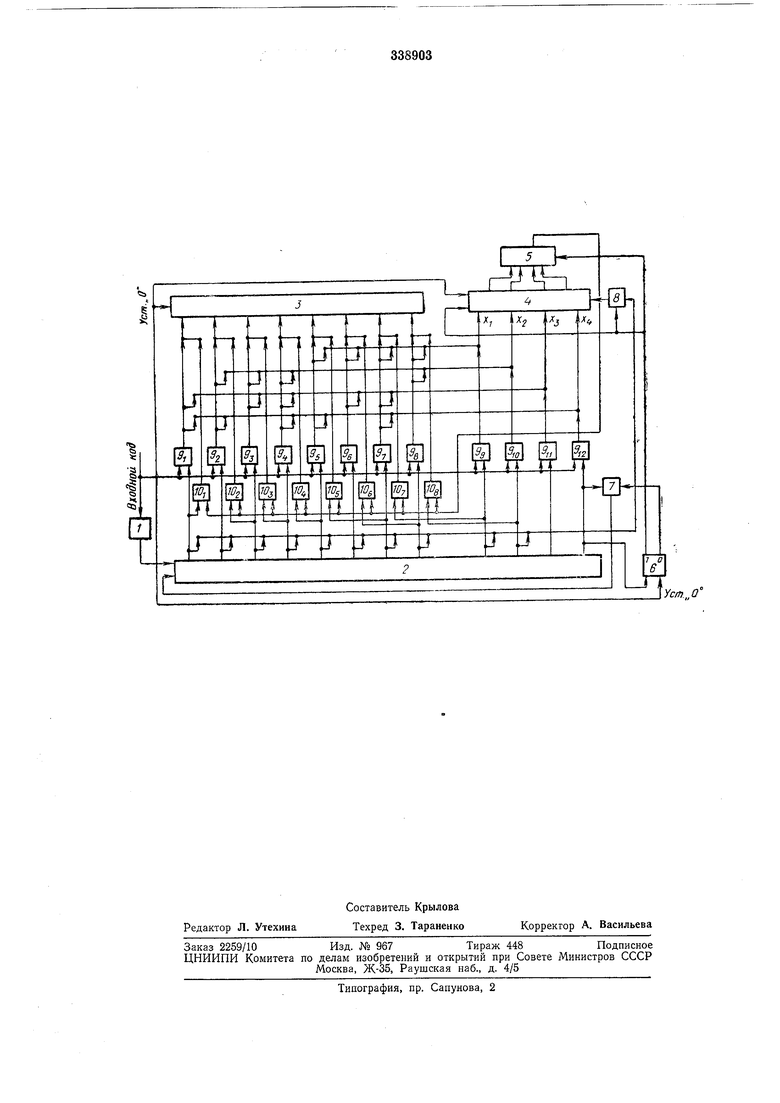

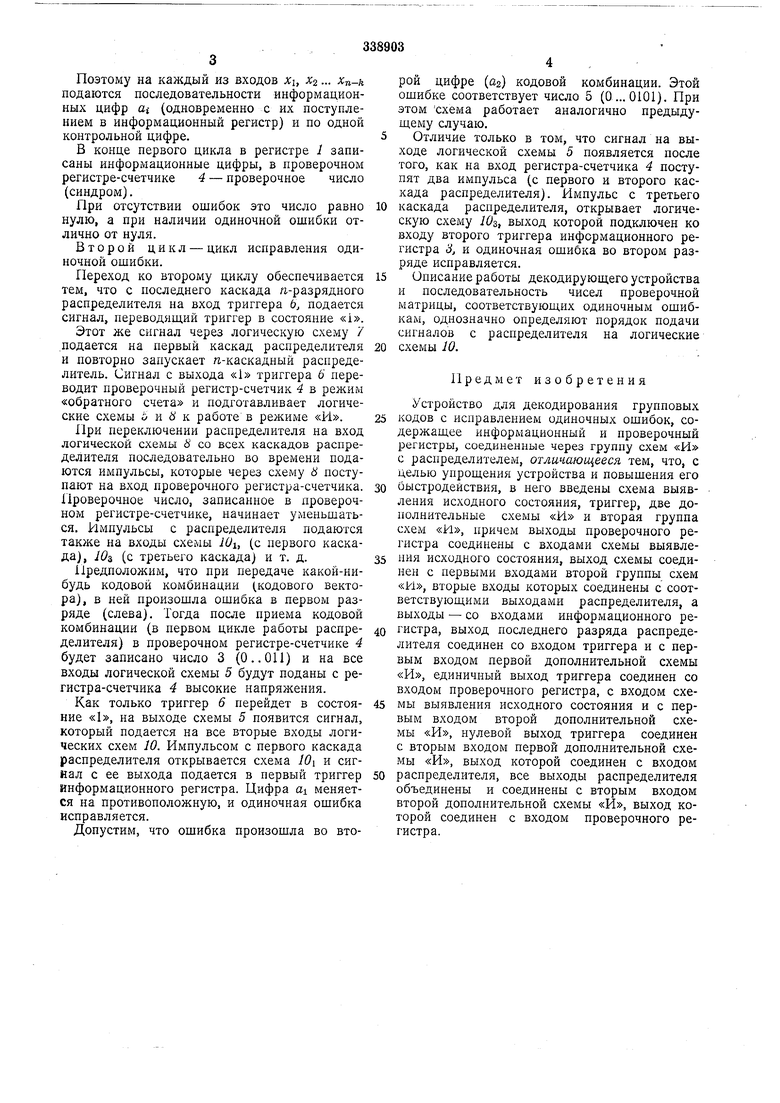

мы декодирования маркера /, распределителя 2, информационного регистра 3, проверочного регистра-счетчика 4, схемы выявления исходного состояния 5, управляющего триггера 6, двухвходовых логических схем 7-10.

Работа схемы разбивается на два цикла.

Первый цикл - цикл записи принимаемой кодовой комбинации.

Входной последовательный двоичный код, состоящий и,з маркера и цифр Ci-f-a, поступает на вход устройства. В течение первого цикла работь распределителя код записывается в регистры.

Импульс, получающийся на выходе схемы / в результате декодирования маркера, запускает распределитель и устанавливает в нуль информационный регистр 3, проверочный регистр 4 и управляющий триггер 6. Цифры входного кода записываются в информационный и проверочный регистры через логические схемы 9.

Проверочные цифры в групповых (п, k) -кодах образуются по правилам, имеющим вид:

25

.

Поэтому на каждый из входов Xi, Х2... Xn-k подаются последовательности информационных цифр ui (одновременно с их поступлением в информационный регистр) и по одной контрольной цифре.

В конце первого цикла в регистре 1 записаны информационные цифры, в проверочном регистре-счетчике 4 - проверочное число (синдром).

При отсутствии ошибок это число равно нулю, а при наличии одиночной ошибки отлично от нуля.

Второй цикл - цикл исправления одиночной ошибки.

Переход ко второму циклу обеспечивается тем, что с последнего каскада д-разрядного распределителя на вход триггера Ь, подается сигнал, переводящий триггер в состояние «i.

Этот же сигнал через логическую схему 7 .подается на первый каскад распределителя и повторно запускает п-каскадный распределитель. Сигнал с выхода «1 триггера 6 переводит проверочный регистр-счетчик 4 в режим «обратного счета и подготавливает логические схемы i и и к работе в режиме «И.

При переключении распределителя на вход логической схемы 8 со всех каскадов распределителя последовательно во времени подаются импульсы, которые через схему в поступают на вход проверочного регистра-счетчика. Проверочное число, записанное в проверочном регистре-счетчике, начинает уменьшаться. Импульсы с распределителя подаются также на входы схемы lOi, (с первого каскада), 10 (с третьего каскада) и т. д.

Предположим, что при передаче какой-нибудь кодовой комбинации (кодового вектора), в ней произошла ошибка в первом разряде (слева). Тогда после приема кодовой комбинации (в нервом цикле работы распределителя) в проверочном регистре-счетчике 4 будет записано число 3 (0..011) и на все входы логической схемы 5 будут поданы с регистра-счетчика 4 высокие напряжения.

Как только триггер 6 перейдет в состояние «1, на выходе схемы 5 появится сигнал, который подается на все вторые входы логических схем 10. Импульсом с первого каскада распределителя открывается схема lOi и сигнал с ее выхода подается в первый триггер информационного регистра. Цифра ai меняется на противоположную, и одиночная ошибка исправляется.

Допустим, что ошибка произошла во второй цифре (us) кодовой комбинации. Этой ошибке соответствует число 5 (0... 0101). При этом схема работает аналогично предыдущему случаю.

Отличие только в том, что сигнал на выходе логической схемы 5 появляется после того, как на вход регистра-счетчика 4 поступят два импульса (с первого и второго каскада распределителя). Импульс с третьего

каскада распределителя, открывает логическую схему Юг, выход которой подключен ко входу второго триггера информационного регистра 3j и одиночная ошибка во втором разряде исправляется.

Описание работы декодирующего устройства и последовательность чисел проверочной матрицы, соответствующих одиночным ошибкам, однозначно определяют порядок подачи сигналов с распределителя на логические

схемы 10.

Предмет изобретения

Устройство для декодирования групповых

кодов с исправлением одиночных ошибок, содержащее информационный и проверочный регистры, соединенные через группу схем «И с распределителем, отличающееся тем, что, с целью упрощения устройства и повышения его

быстродействия, в него введены схема выявления исходного состояния, триггер, две дополнительные схемы «И и вторая группа схем «И, причем выходы проверочного регистра соединены с входами схемы выявления исходного состояния, выход схемы соединен с первыми входами второй группы схем «И, вторые входы которых соединены с соответствующими выходами распределителя, а выходы - со входами информационного регистра, выход последнего разряда распределителя соединен со входом триггера и с первым входом первой дополнительной схемы «И, единичный выход триггера соединен со входом проверочного регистра, с входом схемы выявления исходного состояния и с первым входом второй дополнительной схемы «И, нулевой выход триггера соединен с вторым входом первой дополнительной схемы «И, выход которой соединен с входом

распределителя, все выходы распределителя объединены и соединены с вторым входом второй дополнительной схемы «И, выход которой соединен с входом проверочного регистра.

j

ВЧ

O1

J

и i ш S

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ГРУППОВЫХ кодов | 1973 |

|

SU374603A1 |

| Устройство для декодирования (п,к)кодов | 1974 |

|

SU526083A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМОШИБОК | 1970 |

|

SU264774A1 |

| Устройство для декодирования /п,к/ кодов | 1976 |

|

SU638966A2 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ И ОБНАРУЖЕНИЕМ МНОГОКРАТНЫХОШИБОК | 1970 |

|

SU273516A1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| СПОСОБ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА И ДЕКОДЕР ДЛЯ СИСТЕМЫ ПЕРСОНАЛЬНОГО РАДИОВЫЗОВА | 1994 |

|

RU2108667C1 |

| Логическое запоминающее устройство | 1978 |

|

SU771720A1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

,j-r-j-r r-j T-j

Ус/г,0°

Авторы

Даты

1972-01-01—Публикация