34

торого соединены с входами первого дешиф-За счет этого обеспечивается повышение

ратора и с выходами регистра частного ибыстродействия устройства по сравнению с

регистра-счетчика остатка, выход элемен-известным устройством.

та ИЛИ соединен со вторым входом второгоРежим 11 - режим исправления ошибки,

элемента И, йыход которого соединен с еди- 5Этот режим осуществляется также за один

ничным входом триггера.цикл работы распределителя.

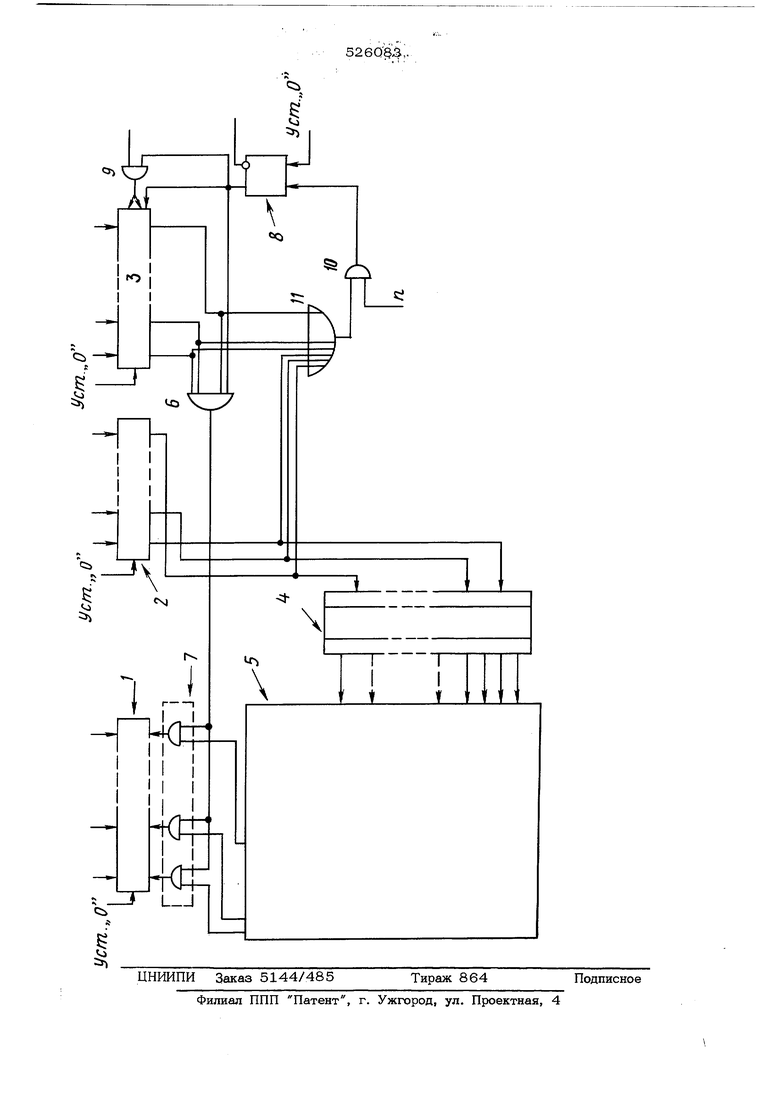

Схема устройства приведена на чертеже. переходе триггера 8 в состояние 1 Устройство состоит из информационного« О вырабатывается импульсрегистра 1, регистра 2 частного, регистра- « повторного запуска распресчетчика 3 остатка, дешифраторов 4 и 5,

блока б выявления исходного состояния, груп- Р° потенциальный сигнал с выпы элементов И 7 управляющего триггера 8, триггера подается на вход блока 6 элементов И 9 и 10, элемента ИЛИ 11 ивыявления исходного состояния, на управляраспределителя (не показан).ютт вход регистра-счетчика остатка 3 для Устройство работает в двух режимах. переключения его в режим обратного счета Режим I - режим записи кодовой ком- « ° первого элемента И 9. бинации. Этот режим осуществляется за один В соответствии с величиной частного на цикл работы распределителя. В начале режи-выходе одной из шин первого дешифратора 4 ма на провода установки в нуль (уст. О) „в конце первого режима появляется потенциподается импульс, который устанавливает вальный сигнал, который подается на вход нуль информационный регистр 1, регистрвторого дешифратора о. Правые входы двухчастного 2, регистр-счетчик остатка 3 ивходовых элементов И этого дешифратора управляющий триггер 8. Затем за один циклподключены к соответствующим выходным работы распределителя осуществляется- за- js™инам первого дешифратора, а левые входыпись информационных цифр в информационныйк шинам, на которые подаются сигналы с регистр и - проверочных цифр в регистр част-соответствующих каскадов распределителя, ного и регистр-счетчик остатке. В информа-Количество двухвходовых элементов И во ционном регистре 1 записывается информа-втором дешифраторе равно количеству исправционная часть кодовой комбинации. Провероч-д ляемых ошибок, а количество элементов ИЛИные цифры образуются в соответствии с урав-количеству информационных разрядов k. нениями проверки из информационных и конт- При переключении распределителя сигнарольных ЦИФР принимаемой кодовой комбина-лы с его выходов через элемент задержки ции. Проверочное число состоит из двух час-и первый логический элемент И 9 поступатей: частного (первые Р цифр), которое ® общий счетный вход регистра-счетчизаписывается в регистр частного, и остаткака остатка 3. Число, записанное в регистре(последние П - fe - Г цифр), которыйсчетчике остатка, начинает уменьщаться. записывается в регистр-счетчик остатка. Ее-Как только это число станет равным О...О1, ли проверочное число равно нулю, на этомна выходе блока 6 выявления исходного содекодирование принятой кодовой комбинации 40стояния появляется потенциальный сигнал, заканчивается. Если проверочное число от-который подается на все правые группыдвухлично от нуля, что свидетельствует о нали-входовых элементов И 7. Следующий импульс чии исправляемых ошибок кратности i ираспределителя, поступив на одну из шин меньше (или неисправляемых ошибок кратное-второго дешифратора 5, проходит через соти больше t ) на выходе элементов ИЛИИ 45ответствуюшие элементы И и ИЛИ дешифрапоявляется сигнал, который будет подан натора и поступает на левые входы элеменпервый вход второго элемента 10. Па другойтов И 7 (на t или менее входов в соотвход этой схемы (обозначенный буквой П )ветствии с кратностью исправляемой ошибки), с выхода последнего каскада распределителяСигналы с выходом элементов И 7 поступапоступает импульс, который переводит управ- 50К) в информационный регистр и ошибка буляющий триггер 8 в состояние 1.дет исправлена. При дальнейшем переключеПо окончании первого режима все прове-нии распределителя сигнал на выходе блока рочное число будет записано в регистре част-выявления исходного состояния исчезает. Сигного (первые t цифр) и в регистре счет-нал с выхода последнего каскада распредечика остатка (последние П - te -г цифр). 56лителя проходит через элемент И 10 и поПри этом частное декодируется дешифрато-ступает на вход установки триггера в состо- ром 4, на соответствующей выходной щине ко-яние 1, но так как триггер находится в торого появляется сигнал по окончании первогососто5шии 1, его состояние не изменяетрежима. Остаток же декодируется во второмся. Па этом заканчивается декодирование режиме 60принятой кодовой комбинации.

526О83

10ГГ (- ПТТТ -ГТЯ

Таким образом, предложенное устройство позволяет повысить быстродействие и упрощается за счет того, что часть проверочного числа, записанная в регистре частного, декодируется дешифратором, остаток проверочного числа декодируется последовательно во времени во втором режиме - режиме исправления ошибки. Кроме того, если проверочное число равно нулю, сигнал для перевода устройства в режим исправления ошибки не вырабатывается и декодирование кодовой комбинации в этом случае осуществляется за один цикл работы приемного распределителя.

Формула изобретения

Устройство для декодирования (П., fe ) кодов, содержащее информационный регистр, регистр частного, регистр-счетчик остатка, два дешифратора, блок выявления исходного состояния, группу элементов И, триггер и два элемента И, причем первый и второй дешифраторы, группа элементов И и информационный регистр соединены последовательно, другие входы второго дешифратора соединены с соответствующими выходами распределителя, счетный вход регистра-счетчика остатка соединен с выходами распределителя через первый элемент И, другой вход которого

соединен с управляющими входами регистрасчетчика остатка и блока выявления исходного состояния и с единичным выходом триггера, нулевой выход которого соединен управляющим входом распределителя, а нулевой вход - с управляющим входом устройства, П -ый выход распределителя соединен с первым входом второго элемента И, выходы регистра-счетчика остатка соединены со входами блока выявления исходного состояния, выход которого соединен с управляющим входом группы элементов И, отличающееся тем, что, с целью упрощения и повышения быстродействия устройства, оно содержит элемент ИЛИ, входы которого соединены с входами первого дешифратора и с выходами регистра частного и регистра-счетчика остатка, выход элемента ИЛИ соединен со вторым рходом второго элемента И, вы ход которого соединен с единичным входом триггера.

Источники информации, принятые во внимание при экспертизе:

l.y.Kou. Коды с исправлением ошибок и

их реализация в цифровых системах, сб. Мтоды введения избыточности для вычислителных систем, Сов, радио М. 1966, стр. 179-229.

2. Авторское свидетельство СССР №374603, G 06 f 11/10, 26.01.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ГРУППОВЫХ кодовс | 1972 |

|

SU338903A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМОШИБОК | 1970 |

|

SU264774A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ГРУППОВЫХ кодов | 1973 |

|

SU374603A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ И ОБНАРУЖЕНИЕМ МНОГОКРАТНЫХОШИБОК | 1970 |

|

SU273516A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО КОДА ХЕММИНГА | 2004 |

|

RU2270521C1 |

| Устройство для обмена информацией | 1982 |

|

SU1131035A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО КОДА ХЭММИНГА | 2013 |

|

RU2530282C1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| Устройство для декодирования /п,к/ кодов | 1976 |

|

SU638966A2 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

Авторы

Даты

1976-08-25—Публикация

1974-02-18—Подача