Известны декодируюш,ие устройства с исправлением одиночных и обнаружением многократных ошибок, содержащие схему выделения маркера, распределитель, информационный и проверочный регистры.

Предлагаемое устройство отличается от известных ,тем, что оно содержит схему выявления исправляемых и обнаруживаемых ошибок, состоящую из двоичного счетчика, вход которого подключен к выходам клапанов проверочного регистра, логической схемы выявления исправляемых ошибок, входы которой подсоединены к выходам счетчика, а выход - через логические схемы «И к счетным входам: информационного регистра, и логической схемы выявления обнаруживаемых ошибок, входы которой подключены к выходам нроверочного регистра, а выход связан с шиной «установки в нулевое состояние информационного регистра.

Это иозволяет упростить структуру устройства.

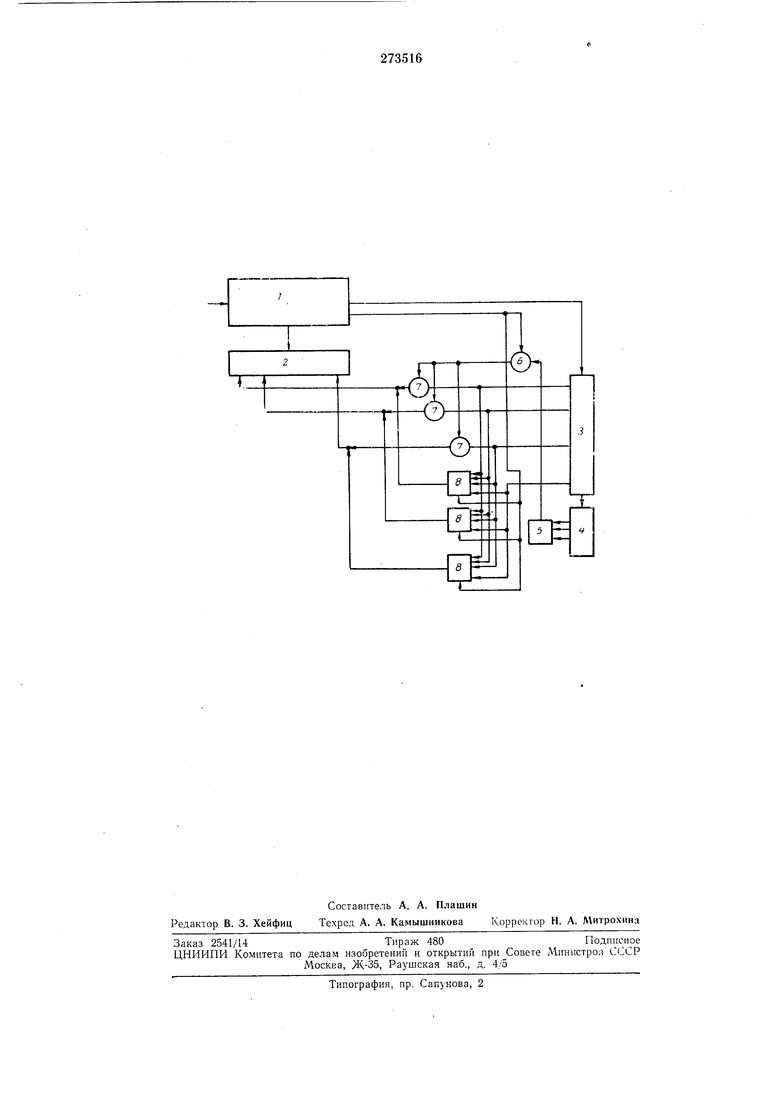

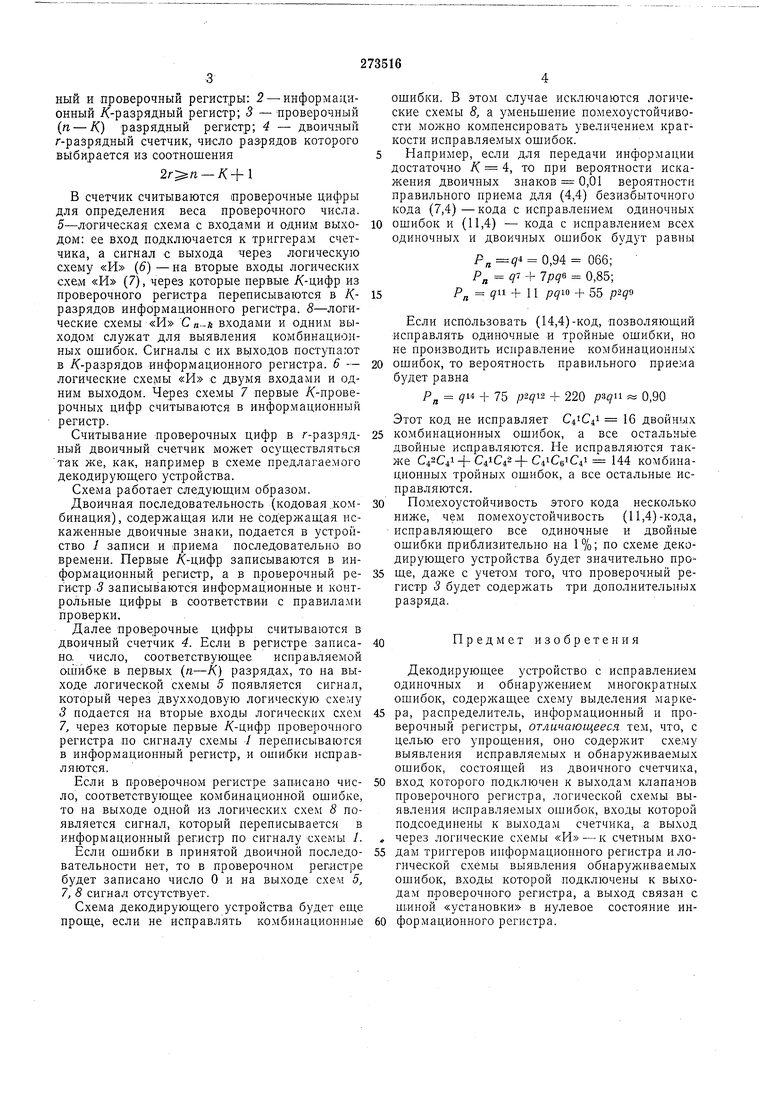

На чертеже представлена блок-схема предлагаемого декодирующего устройства. Для построения кодов, исправляющих ошибки от одиночных до / -кратных включительно, используется зеркальная проверочная матрица, у которой в первые (п - /С) разряды записываются проверочные числа с весом единица.

Упрощение схемы достигается за счет того, что в проверочном регистре при наличии ошибок в первых (п-1{) разрядах образуется -опознаватель, единицы которого указывают место ошибки, а дополнительное устройство выявления исправляемых ошибок указывает, к какой категории относится эта ошибка: к исправляемым или неисправляемым ошибкам.

Для кодов это дает возможность исправить

Г 4- ГЗ L

+(-A + 4-2ft k

ДВОЙНЫХ ошибок, из которых фактически исправляются лишь С .Остальные комбинационные ошибки, состоящие из одиночных ошибок в информационных и одиночных в контрольных разрядах, исправляются при помощи К-логических схелг, входы которых подключены к триггерам проверочного регистра, а выходы - ко входам

триггеров информационного регистра. Число таких ошибок равно

C..

На чертеже приняты следующ.ие обозначения. / - схема приема и записи последовательного двоичного кода, состоящая из схемы выделения маркера, распределителя и двухходовых логических схем «И (схем совпадения). Это устройство осуществляет запись принятой двоичной последовательности в инфо-рмационный и проверочный регистры: 2 информационный /С-разрядный регистр; 5 - проверочный (п - К) разрядный регистр; 4 - двоичный г-разрядный счетчик, число разрядов которого выбирается из соотношения

- К+1

В счетчик считываются проверочные цифры для определения веса проверочного числа. 5- логическая схема с входами и одним выходом: ее вход подключается к триггерам счетчика, а сигнал с выхода через логическую схему «И (6) - на вторые входы логических схем «И (7), через которые первые /С-цифр из проверочного регистра переписываются в /(разрядов информационного регистра. 8-логические схемы «И С л-А входами и одним выходом служат для выявления комбинационных ошибок. Сигналы с их выходов поступают в /(-разрядов информационного регистра. 6 - логические схемы «И с двумя входами и одним выходом. Через схемы 7 первые /(-проверочных цифр считываются в информационный регистр.

Считывание проверочных цифр в г-разрядный двоичный счетчик может осуществляться так же, как, например в схеме предлагаемого декодирующего устройства.

Схема работает следуюш,им образом.

Двоичная последовательность (кодовая.комбинация) , содержащая или не содержащая искаженные двоичные знаки, подается в устройство 1 записи и лриема последовательно во времени. Первые Д-цифр записываются в информационный регистр, а в проверочный регистр 3 записываются информационные и контрольные цифры в соответствии с правилами проверки.

Далее проверочные цифры считываются в двоичный счетчик 4. Если в регистре записано, число, соответствующее исправляемой ошибке в первых (п-Л) разрядах, то на выходе логической схемы 5 появляется сигнал, который через двухходовую логическую схему 3 подается на вторые входы логических схем 7, через которые первые /(-цифр проверочного регистра по сигналу схемы / переписываются в информационный регистр, и ошибки исправляются.

Если в проверочном регистре записано число, соответствующее комбинационной ошибке, то на выходе одной из логических схем 8 появляется сигнал, который переписывается в информационный регистр но сигналу схемы /.

Если ошибки в принятой двоичной последовательности нет, то в проверочном регистре будет записано число О и на выходе схем 5, 7, 8 сигнал отсутствует.

Схема декодирующего устройства будет еще проще, если не исправлять комбинационные

ощибки. В этом случае исключаются логические схемы 8, а уменьшение помехоустойчивости можно компенсировать увеличением краткости исправляемых ошибок.

Например, если для передачи информации достаточно /( 4, то при вероятности искажения двоичных знаков 0,01 вероятности правильного приема для (4,4) безизбыточного кода (7,4)-кода с исправлением одиночных

ошибок и (11,4) - кода с исправлением всех одиночных и двоичных ошибок будут равны

(4 0,94 066; РП Я + 7Р9« 0,85;

Р„ 11 + 1 1 + 55 /729

Если использовать (14,4)-код, позволяющий

исправлять одиночные и тройные ошибки, но

не производить исправление комбинационных

ошибок, то вероятность правильного приема

будет равна

Р qu + 75 + 220 рз,;, 0,90

Этот код не исправляет 16 двойных комбинационных ошибок, а все остальные двойные исправляются. Не исправляются также 144 комбинационных тройных ошибок, а все остальные исправляются.

Помехоустойчивость этого кода несколько ниже, чем помехоустойчивость (11,4)-кода, исправляюшего все одиночные и двойные ошибки приблизительно на 1%; но схеме декодируюшего устройства будет значительно проще, даже с учетом того, что проверочный регистр 3 будет содержать три дополнительных разряда.

Предмет изобретения

Декодирующее устройство с исправлением одиночных и обнаружением многократных ошибок, содержащее схему выделения маркера, распределитель, информационный и проверочный регистры, отличающееся тем, что, с целью его упрощения, оно содержит схему выявления исправляемых и обнарулсиваемых ошибок, состоящей из двоичного счетчика,

вход которого подключен к выходам клапанов проверочного регистра, логической схемы выявления исправляемых ошибок, входы которой подсоединены к выходам счетчика, а выход через логические схемы «И - к счетным входам триггеров ииформациониого регистра и логической схемы выявления обнаруживаемых ошибок, входы которой подключены к выходам проверочного регистра, а выход связан с шиной «установки в нулевое состояние информационного регистра.

5

43

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМОШИБОК | 1970 |

|

SU264774A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ГРУППОВЫХ кодовс | 1972 |

|

SU338903A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ГРУППОВЫХ кодов | 1973 |

|

SU374603A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО РЕКУРРЕНТНОГО КОДА | 1967 |

|

SU205877A1 |

| Устройство для декодирования (п,к)кодов | 1974 |

|

SU526083A1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

| Устройство для исправления ошибок | 1985 |

|

SU1327297A1 |

| Устройство для декодирования /п,к/ кодов | 1976 |

|

SU638966A2 |

| Устройство для перестановочного декодирования циклических кодов | 1973 |

|

SU552716A1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

Даты

1970-01-01—Публикация