Известны декодирующие устройства с исправлением ошибок от одиночных до / включительно, содержащие схему приема и записи, информационный и проверочные регистры.

Предлагаемое устройство отличается от известных тем, что оно содержит схему выявления исправляемых ошибок в информационных и контрольных разрядах, содержащую двоичный счетчик, вход которого подключен к выходным клапанам цроверочного регистра, и логическую схему выявления многократных ошибок, входы которой подключены к двоичному счетчику, а выход - ко входам клапанов проверочного регистра, логические схемы, подключенные к проверочному регистру, выходы которых подключены к информационному регистру, а схема приема и записи последовательного двоичного кода содержит схемы выделения маркера, распределитель, схемы совпадения, причем выходы схемы приема и записи последовательного двоичного кода подключены к соответствующим входам информационного и проверочного регистров.

Это позволяет упростить структуру устройства.

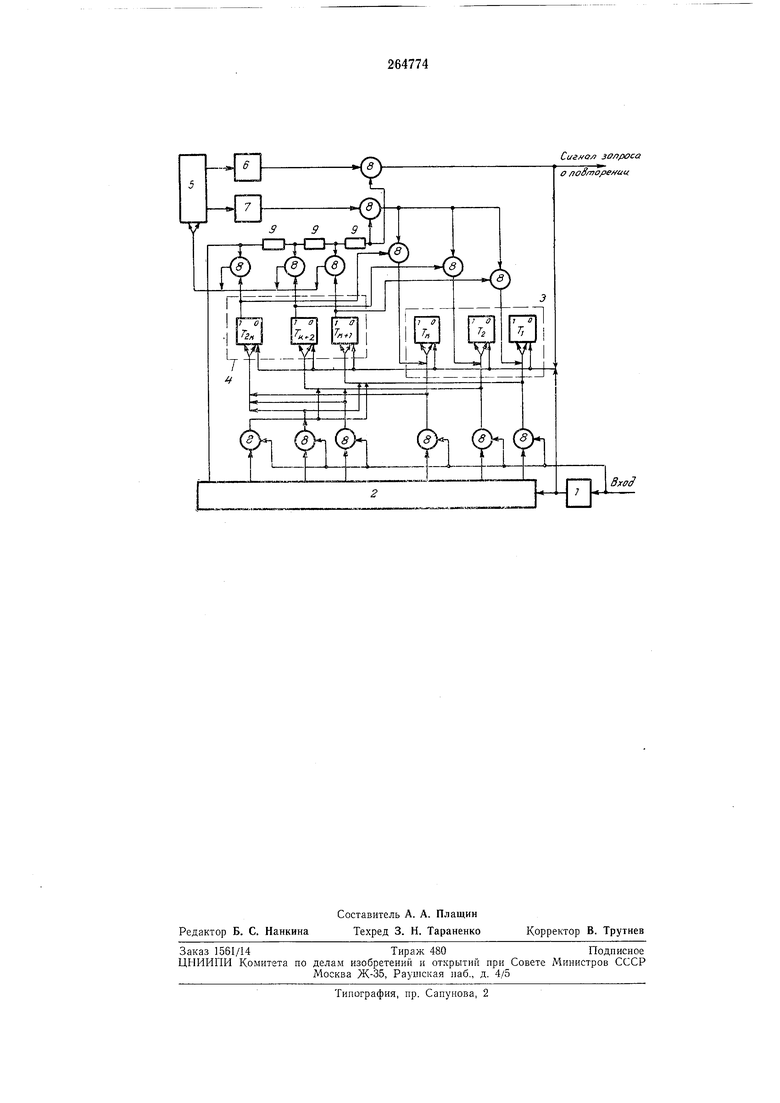

На чертеже представлена блок-схема предлагаемого устройства.

ошибках в информационных разрядах проверочные числа с весом w, причем единицы .указывают номер ошибочного разряда. Проверка веса этого числа дает возможность установить, что ошибка относится к числу исправляемых, поэтому цифра «1 из проверочного регистра считывается в соответствующий триггер информационного регистра. В остальных триггерах этого проверочного регистра в это же время записаны нули, поэтому остальные информационные цифры не изменяются.

Если вес проверочного числа , 1, к-1, то такая ошибка обнаруживается, и регистры сбрасываются в нуль.

Таким образом, упрощение схемы достигается за счет того, что из декодирующего устройства исключается датчик кодовых комбинаций, динамическая память, выходной сумматор или сложный дешифратор проверочных чисел, а уменьшение количества тактов обеспечивается тем, что здесь нет необходимости воспроизводить все 2 кодовые комбинации.

Схема состоит из блока выделения маркера

25 J, распределителя 2, являющиеся схемами

(Приема и записи информационного регистра 3,

дами и одним выходом, а также линии задержки 9.

Кодовая комбинация подается на вход в виде последовательного {и к)-кода. Декодированный маркер запускает распределитель 2 и с помощью распределителя и логических схем цифры кода записываются в информационный регистр 3 (триггеры которого обозначены буквами TI-Tf.) и проверочный регистр 4 (триггеры которого обозначены буквами )В проверочном регистре образуется проверочное число. С последнего каскада распределителя выдается сигнал в линию задержки для считывания цифр проверочного числа в двоич,ный счетчик. В счетчике получается число, которое указывает вес проверочного числа. Если в счетчике будет записано число О или 1, тона .выходе логической схемы 7 появляется сигнал, который считывается через логическую схему «FI и используется для исправления одиночной ошибки. Этот сигнал подается па вторые входы логических схем «И, первые входы которых подключены к триггерам проверочного регистра, а выходы - к счетным входам триггеров информационного регистра.

Если в счетчике образуется число, отличающееся от 0,1 и к-1, то на .выходе логической схемы 6 появляется сигнал, который считывается через логическую схему «И и используется для установки регистров в нуль и для запроса о повторении.

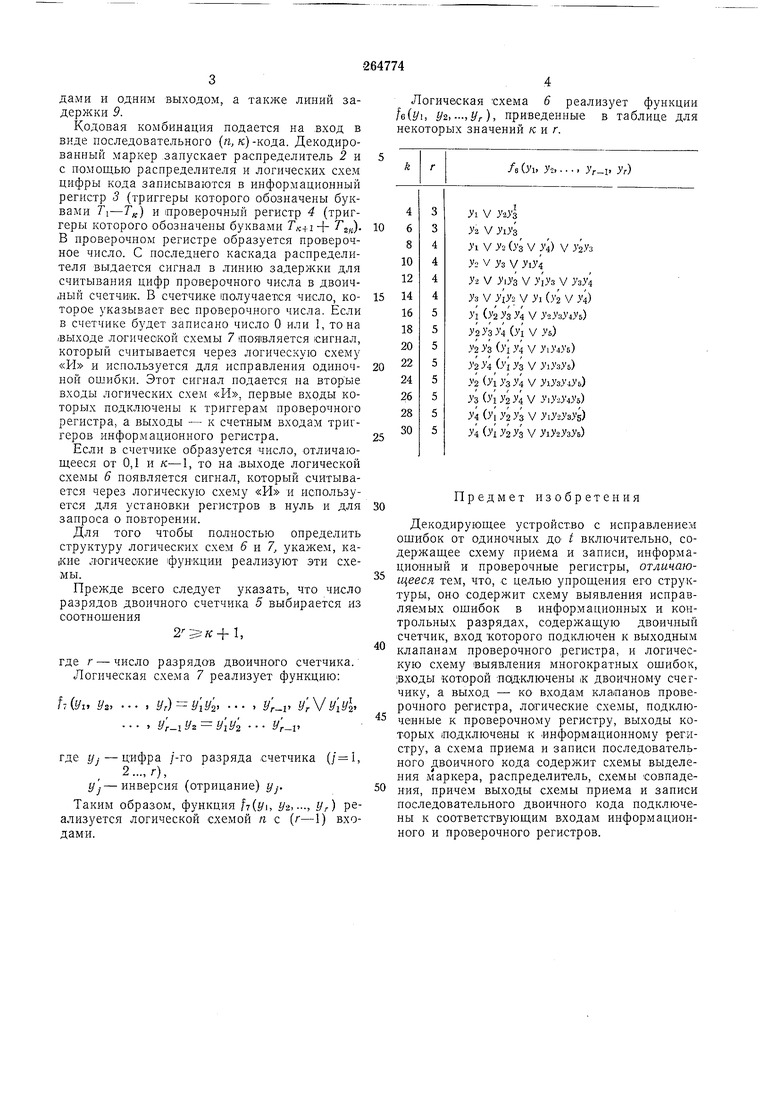

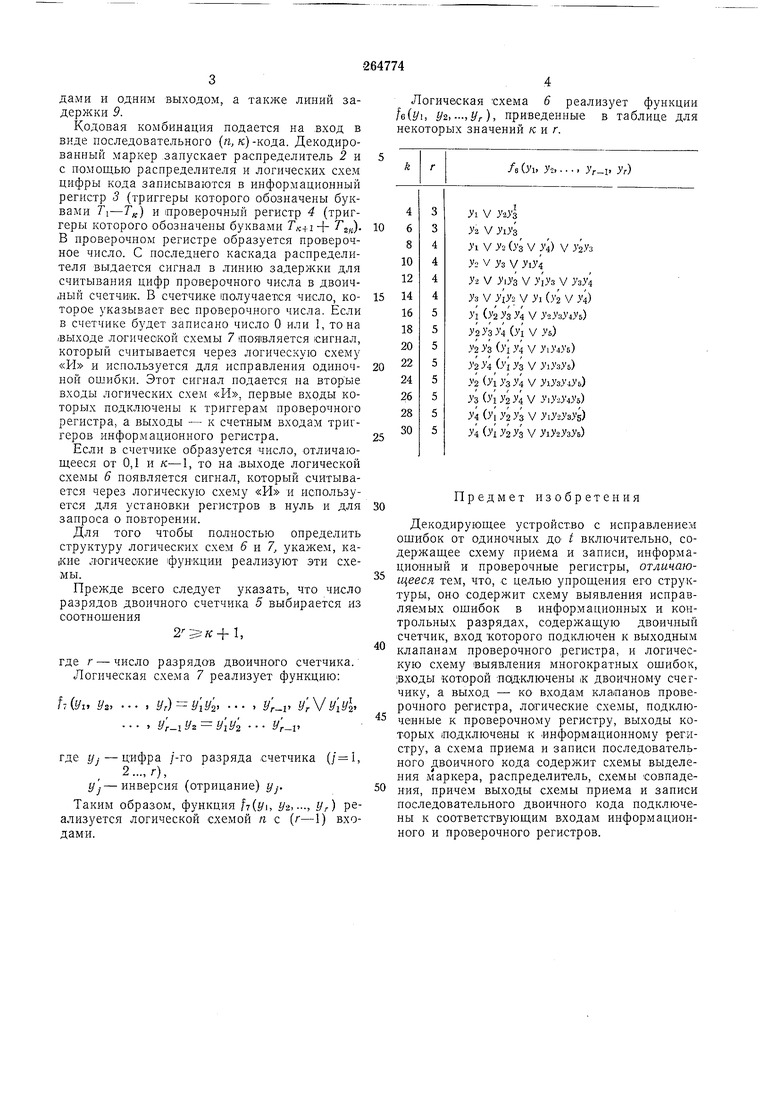

Для того чтобы полностью определить структуру логических схем 5 и 7, укажем, ка|Кие логические функции реализуют эти схемы.

Прежде всего следует указать, что число разрядов двоичного счетчика 5 выбирается из соотношения

,

где г - число разрядов двоичного счетчика. Логическая схема 7 реализует функцию:

f-(yi, /2У,} У1У2 yr-v Уг УгУу

. yr-iyz yiy2 yr-v

где У - цифра /-го разряда счетчика (,

2..., г), у.- инверсия (отрицание) г/у.

Таким образом, функция 1т(у, у,---, У г) ализуется логической схемой и с (г-1) входами.

Логическая схема 6 реализует функции /eCi/i, У2,-.;Уг), приведенные в таблице для некоторых значений /сиг.

Предмет изобретения

Декодирующее устройство с исправлением ошибок от одиночных до t включительно, содержащее схему приема и записи, информационный и проверочные регистры, отличающееся тем, что, с целью упрощения его структуры, оно содержит схему выявления исправляемых ошибок в информационных и контрольных разрядах, содержащую двоичцый счетчик, вход которого подключен к выходным клапанам проверочного регистра, и логическую схему выявления многократных ошибок, ;входы которой лои-ключены к двоичному счегчику, а выход - ко входам клапанов проверочного регистра, логические схемы, подключенные к проверочному регистру, выходы которых подключены к информационному регистру, а схема приема и записи последовательного двоичного кода содержит схемы выделения маркера, распределитель, схемы совпадения, причем выходы схемы приема и записи последовательного двоичного кода подключены к соответствующим входам информационного и проверочного регистров.

Сигнал зопроса

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ И ОБНАРУЖЕНИЕМ МНОГОКРАТНЫХОШИБОК | 1970 |

|

SU273516A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ГРУППОВЫХ кодов | 1973 |

|

SU374603A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ГРУППОВЫХ кодовс | 1972 |

|

SU338903A1 |

| Устройство для декодирования (п,к)кодов | 1974 |

|

SU526083A1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ С МЯГКИМИ РЕШЕНИЯМИ | 2010 |

|

RU2428801C1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1989 |

|

SU1651385A1 |

| Помехоустойчивый кодек для передачи дискретных сообщений | 1990 |

|

SU1727201A2 |

| УСТРОЙСТВО КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2008 |

|

RU2383104C2 |

Даты

1970-01-01—Публикация