1

Изобретение предназначено для телемеханических систем и других систем передачи и приема цифровой информации и используется для циклического декодирования групповых (п, )-кодов, корректирующих все ошибки от одиночных до /-кратных включительно.

Основным недостатком существующих устройств декодирования групповых (п, и)-кодов, исправляющих многократные ощибки, является больщое количество блоков и элементов и сложность функционирования, объясняющая необходимостью обеспечить согласованную работу большого количества блоков устройства.

Цель предлагаемого изобретения заключается в разработке устройства декодирования группового (п, и)-кода, исправляющего ошибки от одиночных до if-кратных включительно с одновременным упрощением схемы устройства.

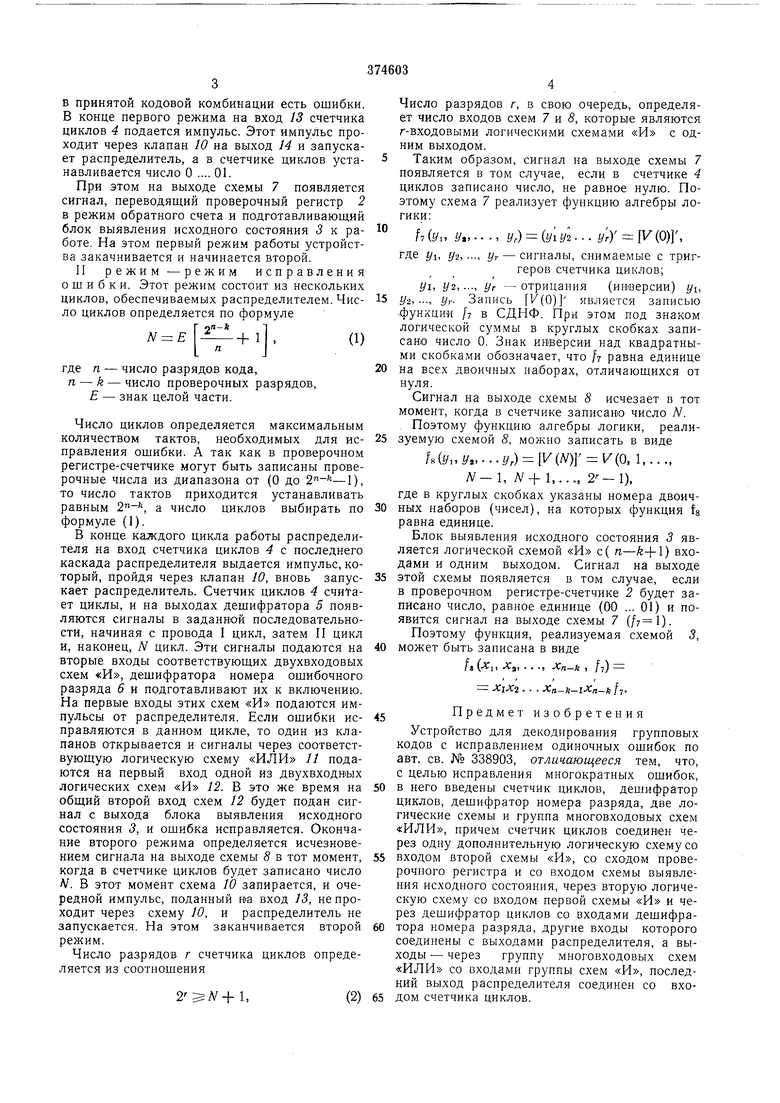

В предлагаемом устройстве эта цель достигается использованием известного устройства декодирования групповых кодов с исправлением одиночных ошибок и введением в него счетчика и дешифратора циклов и логических схем с целью обнаружения места ошибки и ее исправления. Для получения циклического режима работы распределителя и для выбора нужной системы клапанов, через которые нодаются сигналы на исправление ошибок, применяется счетчик циклов и дешифратор циклов, а для обнаружения номера ошибочного разряда - дешифратор ошибочного разряда. На чертеже приведена схема устройства циклического декодирования групповых (п, и)-кодов, исправляющих все ошибки от одиночных до /-кратных включительно.

Устройство состоит из информационного регистра /, проверочного регистра-счетчика 2,

схемы выявления исходного состояния , счетчнка циклов 4, дешифратора циклов 5, дешифратора номера ошибочного разряда 6, логической схемы 7, логической схемы 8, двухвходовых схем «И 9 и 10, группы многовходовых

схем «ИЛИ 11 и группы схем «И 12. Устройство работает в двух режимах. I ре ж им записи принятой кодовой комбинации. Этот режим осуществляется за один цикл работы распределителя

(на чертеже не показан). В начале режима сбрасываются (Уст. «О) информационный регистр /, проверочный регистр 2 и счетчик циклов 4. Затем за один цикл работы распределителя осуществляется запись информационных () и проверочных (xi-Xn-h) цифр в информационной и проверочный регистры. В проверочном регистре-счетчике 2 будет записано проверочное число: если это число равно нулю, то в принятой кодовой комбинации

ошибок нет, если число не равно НУЛЮ, то в принятой кодовой комбинации есть ошибки. В конце первого режима на вход 13 счетчика циклов 4 подается импульс. Этот импульс проходит через клапан 10 на выход 14 и запускает распределитель, а в счетчике циклов устанавливается число О .... 01. При этом на выходе схемы 7 появляется сигнал, переводящий проверочный регистр 2 в режим обратного счета и подготавливающий блок выявления исходного состояния 3 к работе. На этом первый режим работы устройства закачнивается и начинается второй. II режим -режим исправления ошибки. Этот режим состоит из нескольких циклов, обеспечиваемых распределителем. Число циклов определяется по формуле Г 4V+j где п - число разрядов кода, п - k - число проверочных разрядов, Е - знак целой части. Число циклов определяется максимальным количеством тактов, необходимых для исправления ошибки. А так как в проверочном регистре-счетчике могут быть записаны проверочные числа из диапазона от (О до ), то число тактов приходится устанавливать равным 2, а число циклов выбирать по формуле (1). В конце каждого цикла работы распределителя на вход счетчика циклов 4 с последнего каскада распределителя выдается импульс, который, пройдя через клапан 10, вновь запускает распределитель. Счетчик циклов 4 счигает циклы, и на выходах дешифратора 5 появляются сигналы в заданной последовательности, начиная с провода I цикл, затем П цикл и, наконец, Л цикл. Эти сигналы подаются на вторые входы соответствующих двухвходовых схем «И, дешифратора номера ошибочного разряда 6 и подготавливают их к включению. На первые входы этих схем «И подаются импульсы от распределителя. Если ошибки исправляются в данном цикле, то один из клапанов открывается и сигналы через соответствующую логическую схему «ИЛИ 11 подаются на первый вход одной из двухвходных логических схем «И 12. В это же время на общий второй вход схем 12 будет подан сигнал с выхода блока выявления исходного состояния 3, и ошибка исправляется. Окончание второго режима определяется исчезновением сигнала на выходе схемы 8 в тот момент, когда в счетчике циклов будет записано число N. В этот момент схема 10 запирается, и очередной импульс, поданный ва вход /5, не проходит через схему 10, и распределитель не запускается. На этом заканчивается второй режим. Число разрядов г счетчика циклов определяется из соотношения , 5 ° 15 20 25 30 35 40 5 50 55 60 65 Число разрядов г, в свою очередь, определяет число входов схем 7 и 5, которые являются г-входовыми логическими схемами «И с одним выходом. Таким образом, сигнал па выходе схемы 7 появляется в том случае, если в счетчике 4 циклов записано число, не равное нулю. Поэтому схема 7 реализует функцию алгебры логики:f7 (у., У, у.) (У1У1... угУ V (0), где г/1, г/2,..., УГ - сигналы, снимаемые с триггеров счетчика циклов; г/1, г/2,..., УГ - отрицания (ивверсии) г/i, г/2,..., УГ- Запись fV(0) является записью .функции /7 в СДНФ. При этом под знаком логической суммы в круглых скобках записано число 0. Знак инверсии над квадратными скобками обозначает, что f равна единице на всех двоичных на:борах, отличающихся от нуля. Сигнал на выходе схемы 8 исчезает в тот момент, когда в счетчике записаню число N. . Поэтому функцию алгебры логики, реализуемую схемой 8, можно записать в виде h(y..y,...yr} (Q,,..., Л/-1, Л+l,..., ), где в круглых скобках указаны номера двоичных наборов (чисел), на которых функция fs равна единице. Блок выявления исходного состояния 3 является логической схемой «И с( п-й-j-l) входами и одним выходом. Сигнал на выходе этой схемы появляется в том случае, если в проверочном регистре-счетчике 2 будет записано число, равное единице (00 ... 01) и появится сигнал на выходе схемы 7 (). Поэтому функция, реализуемая схемой 3, может быть записана в виде /J (ЛГи Х, . . ., Хп-Ь т |) Xixz . . . xn-k-ixn-k IT Предмет изобретения Устройство для декодирования групповых кодов с исправлением одиночных ошибок по авт. св. № 338903, отличающееся тем, что, с целью исправления многократных ошибок, в него введены счетчик циклов, дешифратор циклов, дешифратор номера разряда, две логические схемы и группа многовходовых схем «ИЛИ, причем счетчик циклов соединен через одну дополнительную логическую схему со входом второй схемы «И, со сходом проверочного регистра и со входом схемы выявления исходного состояния, через вторую логическую схему со входом первой схемы «И и через дешифратор циклов со входами дешифратора номера разряда, другие входы которого соединены с выходами распределителя, а выходы - через группу многовходовых схем «ИЛИ со входами группы схем «И, последний выход распределителя соединен со входом счетчика циклов.

(o-i,Оя) -S ,JьУ r I b, t/l I/.,

b...,V/.) J-i-TT x

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМОШИБОК | 1970 |

|

SU264774A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ГРУППОВЫХ кодовс | 1972 |

|

SU338903A1 |

| Устройство для декодирования (п,к)кодов | 1974 |

|

SU526083A1 |

| Устройство для декодирования /п,к/ кодов | 1976 |

|

SU638966A2 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ И ОБНАРУЖЕНИЕМ МНОГОКРАТНЫХОШИБОК | 1970 |

|

SU273516A1 |

| СПОСОБ И ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО ИСПРАВЛЕНИЯ ДВУХ ОШИБОК В ПРИНИМАЕМОМ КОДЕ | 2006 |

|

RU2336559C2 |

| Запоминающее устройство с исправлением ошибок | 1983 |

|

SU1133624A1 |

| СПОСОБ КОДОВОЙ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2011 |

|

RU2450436C1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО КОДА ХЕММИНГА | 2004 |

|

RU2270521C1 |

| Способ кодовой цикловой синхронизации для каскадного кода Рида-Соломона и Боуза-Чоудхури-Хоквингема [РС(32,16,17), БЧХ(31,16,7)] при одновременном применении жестких и мягких решений | 2020 |

|

RU2747623C1 |

Авторы

Даты

1973-01-01—Публикация