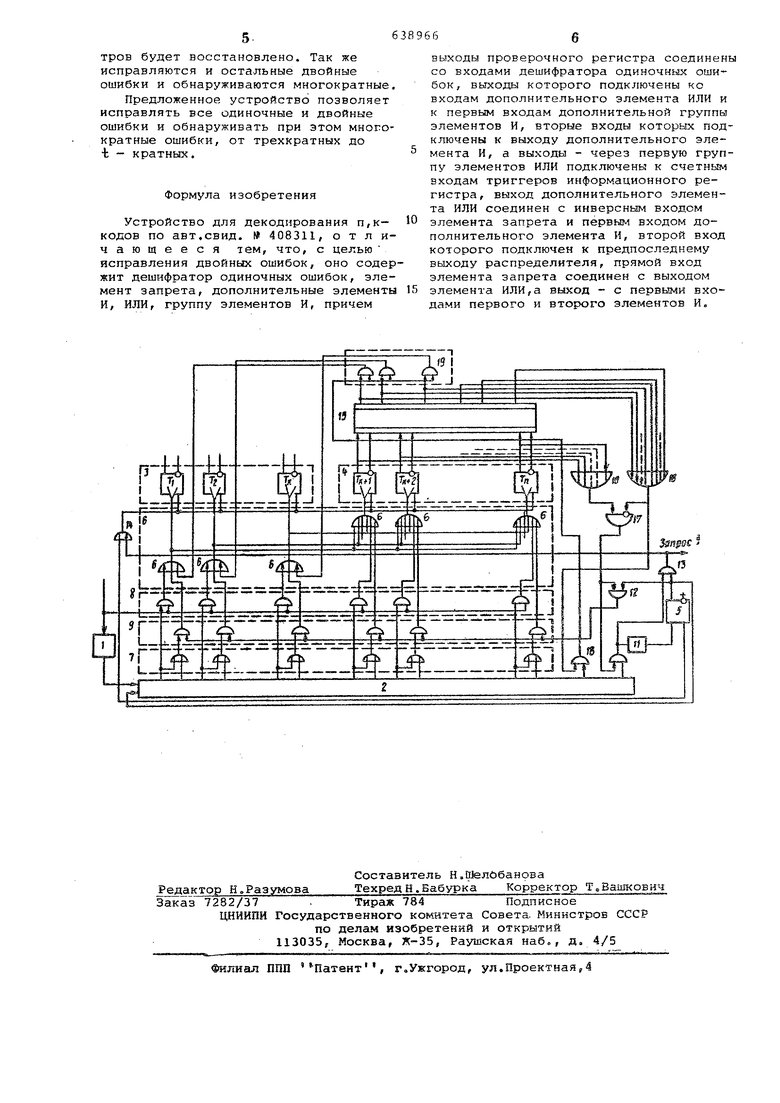

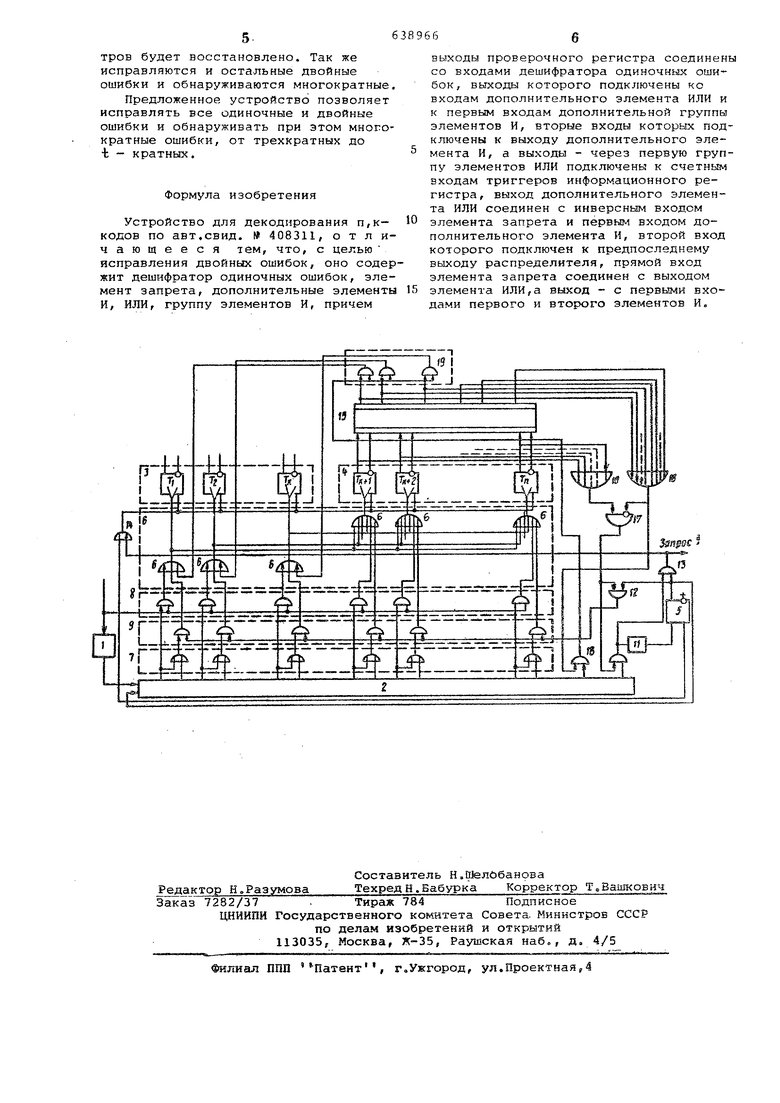

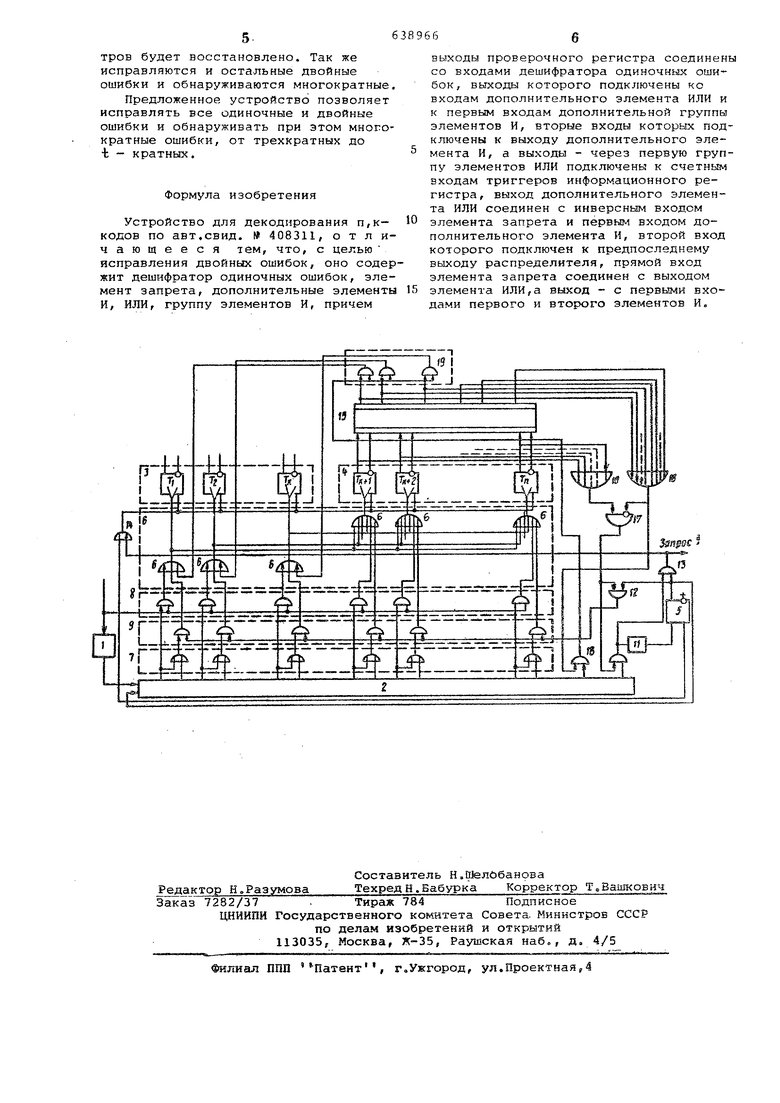

Первый цикл - запись принятой празрядной кодовой комбинации. Входна последовательность, состоящая из мар кера и цифр Ej - an , поступает на вход устройства. Импульс, получа оадийся на выходе схемы 1, запускает распределитель 2 и устанавливает регистры 3, 4 и триггер 5 в положение О. В течение первого цикла цифры а а. v{ записываются в ;.,регистры причем в информационный регистр записываются информационные цифры а, а , а в проверочный регистр цифры записываются в соответствии с уравнениями проверки данного кода. Напри М0рг для 14,4 - кода, у которого п--14 и К--4, уравнения имеют вид (3,4,5),,Кг - (2„4,б) , (2,3,7) ,X. - (2.,3,,4,8) , (1,4р9) ,Х.- (1,3,10.) , (1,3,4,11)., Хс (1,2,12) , - (1,2,3,14)„ (Ь2,4,ЛЗ , ЬГ скобках указаны номера разрядо сумг а цифр которых по mod г образует проверочную цифру. Например, (3p4, +ад + а (тоА 14,4 кодможет исправлять все одиночные и двойные ошибки и обнаруживать все,трехкратные и четырехкратные ошибки, В проверочном регистре в конце первого цикла окажется записанным проверочное число (синдром) X. Если XI равен О , то двоичная последевэтельность принимается за кодовый вектор и переключение схемы на второй цикл не происходит. Если зна-ген,ие X соответствует одиночной ошибке то на ОДНОМ из выходов дешифратора появляется сигнал. Этот сигнал через элемент ИЛИ 16 поступает на вход схе глы Запрета и вход элемента И 18, зак рывает элемент запрета и подготавливает к срабатыванию элемент И 18. Так как в проверочном регистре число отличается от нуля, то появится сигнал на выходе элемента ИЛИ 10, но этот сигнал не. пройдет через элемент запрета 17., так как он запирается си налом с выхода элемента ИЛИ 16, Импульс с предпоследнего каскада распр делителя проходит через элемент И 18 и считывает сигнал с соответствующего выхода дешифратора в тот из триггеров информационного регистра,, где записана ошибочная цифра. Значение цифры изменяется ( заменяется на О или О на ) и, таким образом, осуществляется исправле иие одиночной ошибки. Дешифратор имеет п-выходов, которые заведены на входы элемента ИЛИ 16, Из них первые к-выходы подключены также к группе к к-элементов И 19.с этих элементов считываются сигналы для испра ления к-одиночных ошибок в информацйонных разрядах. Импульс с последне го каскада распределителя не пройдет через элемент И 11, так как отсутствует сигнал на пыходе элемента запрета 17. Если при передаче в п-разрядной последовательности произочша многократная ошибка (t 5 2) , то в проверочном регистре будет записано число X, соответствующее этой ошибке. На выходе элемента ИЛИ 10 появится сигнал и, так как сигнал на выходе элемента ИЛИ 16 отсутствует, то элемент запрета 17 срабатывает, и на его выходе появляется сигнал, который поступит на левые входы элементов И 11, 12, Импульс с последнего каскада распределителя пройдет через элемент И 11 и установит триггер 5 в положение с некоторой задержкой во времени,. Эта задержка в начале второго цикла работы устройства необходима для того, чтобы сигнал с последнего каскада распределителя не прошел через элемент И 13 на выход устройства. Для упрощения настройки устройства и повышения надежности его функционирования во входном проводе установки триггера в 1 возможно применение элемента задержки Сигнал с единичного вы5сода триггера 5 поступит на входы элементов И 12, 13 и запустит распределитель. Сигнал с выхода элемента К 12 поступит на элементы И 9 и подготовит их к работе во втором цикле. Второй цикл - и.икл исправления двойных ошибок или обнаружения многократных, С первых двух отводов распределителя снимаются последовательно два импульса Первый из них через элементы ИЛИ 7, И 9 и ИЛИ 6 пройдет в триггер Т., информационного регистра и изменит цифру а на противоположную« Кроме того, этот сигнал, в соответствии с правилами проверки, поступит в проверочный регистр и изменит проверочное число„ Если двойная ошибка состоит из ошибки в цифре а и ошибки в какой-либо еще цифре, то проверочное число Б регистре после изменения будет соответствовать одиночной ошибке. Поэтому появится сигнал на выходе дешифратора .15, который проходит через элемент ИЛИ 16 и закрывает элемент запрета 17, Сигнал на его выходе исчезает и запираются элементы И 11, 12 и 9, В конце второго цикла импульс с предпоследнего каскада распределителя прой,цет через элемент И 18 и исправит вторую искаженную цифру, если она является информационной. Если ошибка имеет кратность больше двух, то Б конце второго цикла с последнего каскада распределителя через элементы И 11, 13 будет выдан сигнал запроса о повторении и через элемент ИЛИ 14 сигнал установки регистров в О. Если первая цифра а., не искажена j то Htvffsynbc со второго отвода распределителя пройдет через элемен 1 гы ИЛИ 7, И 9 н ИЛИ б и содержимое ;;-л-1формационного и проверочного регистров будет восстановлено. Так же исправляются и остальные двойные ошибки и обнаруживаются многократные Предложенное устройство позволяет исправлять все одиночные и двойные ошибки и обнаруживать при этом много кратные ошибки, от трехкратных до t - кратных. Формула изобретения Устройство для декодирования п,ккодов по авт.свид. № 408311, отли чающееся тем, что, с целью исправления двойных ошибок, оно содер жит дешифратор одиночных ошибок, элемент запрета, дополнительные элементы И, ИЛИ, группу элементов И, причем выходы проверочного регистра соединены со входами дешифратора одиночных ошибок, выходы которого подключены ко входам дополнительного элемента ИЛИ и к первым входам дополнительной группы элементов И, вторые входы которых подключены к выходу дополнительного элемента И, а выходы - через первую группу элементов ИЛИ подключены к счетным входам триггеров информационного регистра, выход дополнительного элемента ИЛИ соединен с инверсным входом элемента запрета и первым входом дополнительного элемента И, второй вход которого подключен к предпоследнему выходу распределителя, прямой вход элемента запрета соединен с выходом элемента ИЛИ,а выход - с первыми входами первого и второго элементов И„

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для декодирования (п,к)кодов | 1974 |

|

SU526083A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ГРУППОВЫХ кодов | 1973 |

|

SU374603A1 |

| УСТРОЙСТВО для ДЕКОДИРОВАНИЯ ГРУППОВЫХ кодовс | 1972 |

|

SU338903A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМОШИБОК | 1970 |

|

SU264774A1 |

| ДЕКОДИРУЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ ОДИНОЧНЫХ И ОБНАРУЖЕНИЕМ МНОГОКРАТНЫХОШИБОК | 1970 |

|

SU273516A1 |

| Тренажер радиооператоров | 1984 |

|

SU1280429A2 |

| Устройство для исправления ошибок | 1983 |

|

SU1095183A1 |

| Устройство для исправления ошибок | 1982 |

|

SU1120335A1 |

| Устройство для исправления одиночных и обнаружения многократных ошибок | 1982 |

|

SU1115055A1 |

| Устройство для исправления ошибок | 1989 |

|

SU1750061A1 |

Авторы

Даты

1978-12-25—Публикация

1976-04-12—Подача